本文转载自:孤独的单刀的CSDN博客

1、什么是AXI4-Full?

AXI 表示 Advanced eXtensible Interface(高级可扩展接口),它是由 Arm 定义的接口协议,包含在“高级微控制器总线架构 AMBA”标准中。

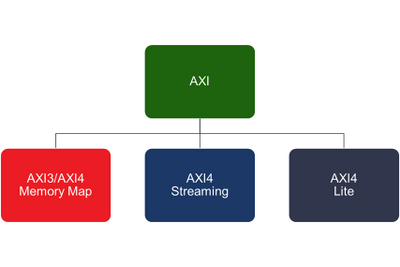

AXI4 接口 (AMBA 4.0) 分 3 种类型:

AXI4 (AXI4-Full):用于满足高性能存储器映射需求。

AXI4-Lite:用于简单的低吞吐量存储器映射通信(例如,往来于状态寄存器的通信)。

AXI4-Stream:用于高速流传输数据。

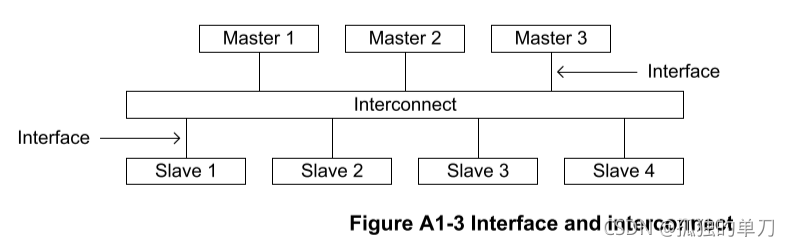

一般情况下,AXI4-Full总线也被直接简称为AXI4总线。AXI4-Full、AXI4-Lite都是内存映射型总线(需要地址),其是多主多从的拓扑结构,可通过Interconnect(AXI4交换设备)来进行互联。具体到XILINX的AXI4应用,一般使用这两个IP来进行多主多从的AXI接口互联:AXI Interconnect(一般使用这个)、AXI SmartConnect。拓扑结构图如下:

2、通道(Channel)

AXI 协议定义了 5 条通道:

其中 2 条用于读取传输事务(transaction):

读地址(AR) read address

读数据 (R) read data

另 3 条用于写入传输事务(transaction):

写地址(AW) write address

写数据(W) write data

写响应(R) write response

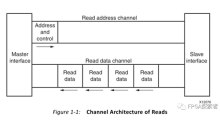

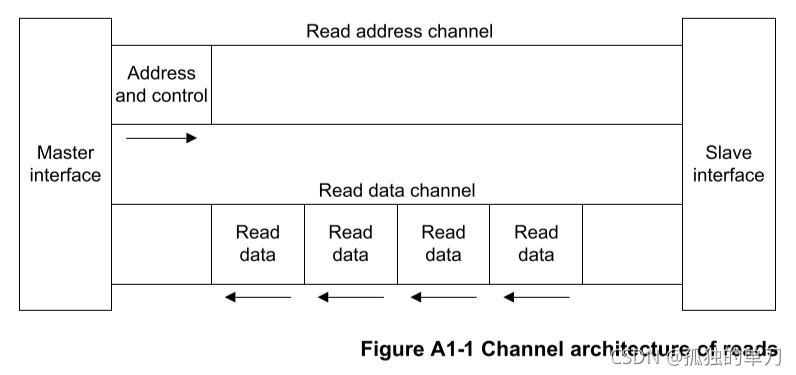

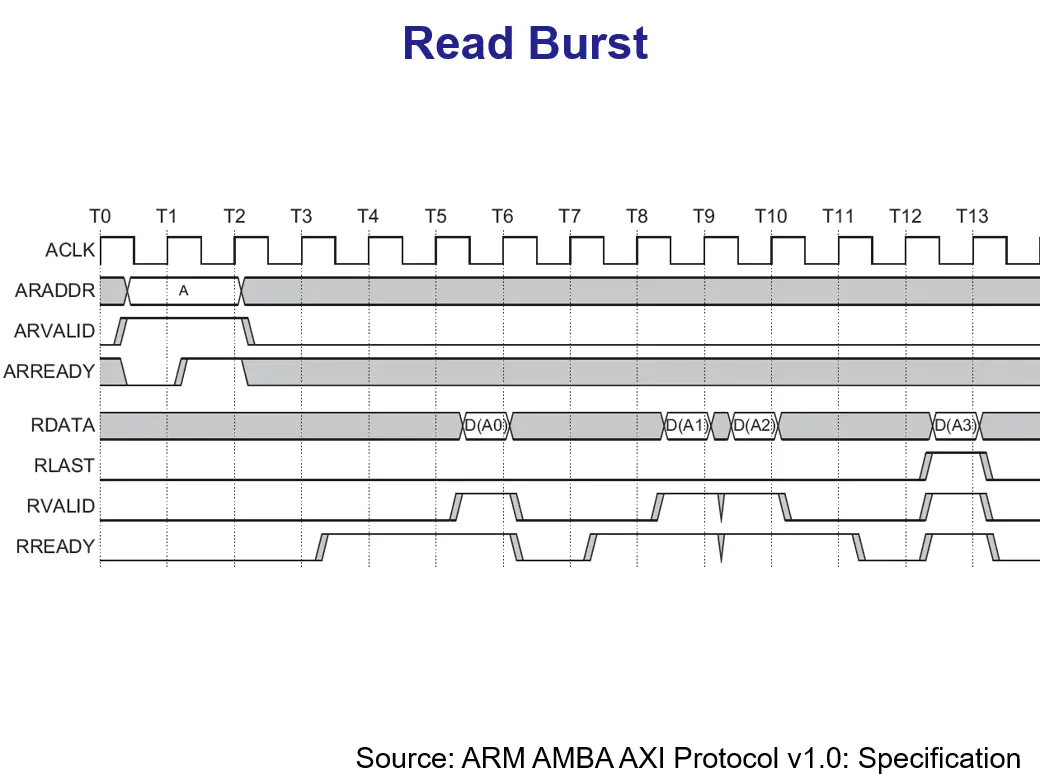

2.1、AXI 读取传输事务

AXI 读传输事务需要在 2 条读取信道上发生多次传输:读地址通道 (Read Address Channel)、读数据通道 (Read data channel) 。

首先,读地址通道 (Read Address Channel) 从主设备 (Master) 发送到从设备 (Slave),以便设置地址和部分控制信号。

然后,此地址的数据通过读数据通道 (Read data channel) 从从设备发送到主设备。

请注意,根据下图所示,每个地址中可发生多次数据传输。此类型的传输事务称为突发 (burst)。需要注意的是AXI4-Full是支持突发的,而AXI4-Lite是不支持突发的,或者说“突发长度为1”。

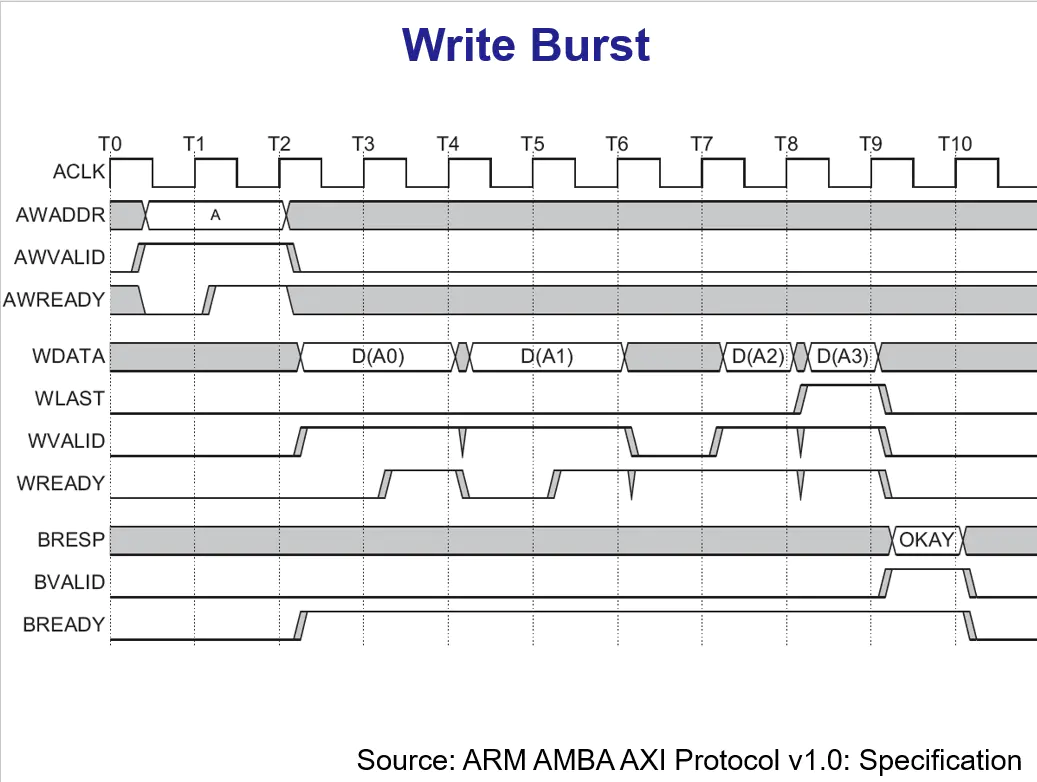

2.2、AXI 写入传输事务

AXI 写入传输事务需要在 3 条读取信道上存在多次传输。

首先,写地址通道 (Write Address Channel) 从主设备发送到从设备,以便设置地址和部分控制信号。

然后,此地址的数据通过写数据通道 (Write data channel) 从主设备发射到从设备。

最后,写入响应通过写响应通道 (Write Response Channel) 从从设备发送到主设备,以指示传输是否成功

写响应通道 (Write Response Channel) 上可能的响应值包括:

OKAY (0b00):正常访问成功。表示已成功完成正常访问

EXOKAY (0b01):专属访问成功。

SLVERR (0b10):从设备错误。已成功访问从设备,但从设备希望向发端主设备返回错误条件(例如,数据读取无效)。

DECERR (0b11):解码器错误。通常由互连组件生成,用于指示传输事务地址处没有任何从设备

看到这里可能会发现读、写事务所需的通道数不相同,写事务需要3条通道,而读事务只需要2条通道,较之少了一条“读响应通道”,难道读事务不需要响应吗?读事务当然也需要响应,只不过既然已经存在一条读数据通道,刚刚好这条通道就是用来传输数据的,那么自然也可以用来传输数据作为读取响应。读事务的响应值规则与写事务的响应值规则一致。

2.3、通道定义(channel definition)

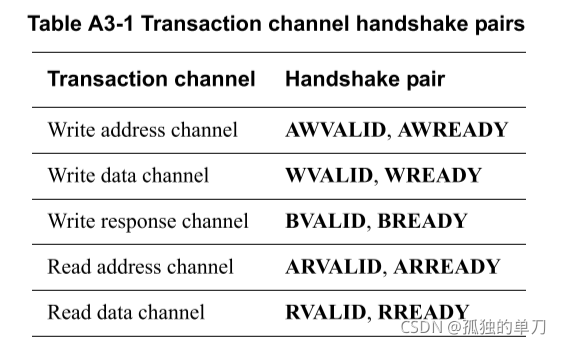

首先,5个通道都具有的同一类信号:VALID、READY。这两个信号用来实现AXI协议的握手机制(handshake)。在读写数据两条数据通道中,传输突发传输(Burst Transaction)中的最后一个数据,必须要给出 LAST 信号,来标识这是此次突发传输中的最后一个数据。在共同的定义之外,各个通道有自己的定义。

读、写地址通道(Read and write address channels)

读、写事务分别具有各自的独立通道,写入本次事务所需的地址和控制信息。

读数据通道(Read data channel)

读数据通道上包括从机发送给主机的读数据,以及从机对于本次读传输操作的回复。总线数据位宽可以是 8,16,64,128,256,512 或者是 1024 bit。

写数据通道(Write data channel)

写数据通道上包括主机发送给从机的写数据。总线数据位宽可以是 8,16,64,128,256,512 或者是 1024 bit。写数据通道还具有STROBE 信号,该信号以数据的字节为单位进行选取,可实现数据的掩码功能。

写响应通道(Write response channel)

写响应通道用于从机将写操作响应回复给主机。所有写传输操作都需要以写回复通道上接收写响应作为完成信号。

3、信号

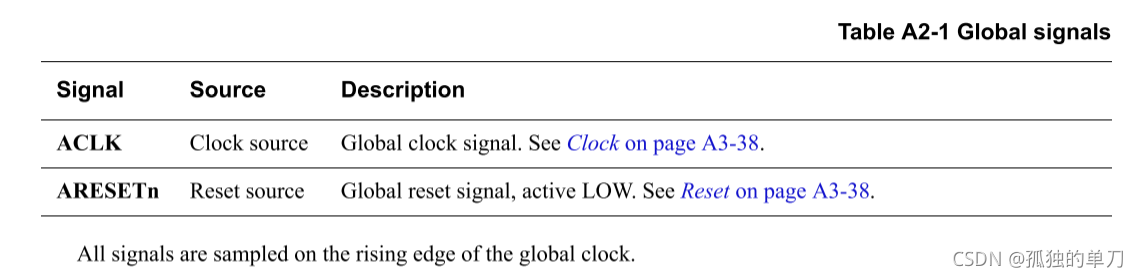

3.1、全局信号(Global signals)

ACLK:全局时钟信号,所有的传输操作都发生在 ACLK 的上升沿

ARESETn:低电平有效的同步复位信号(可以是异步复位,但必须同步释放在时钟上升沿,即异步复位同步释放)

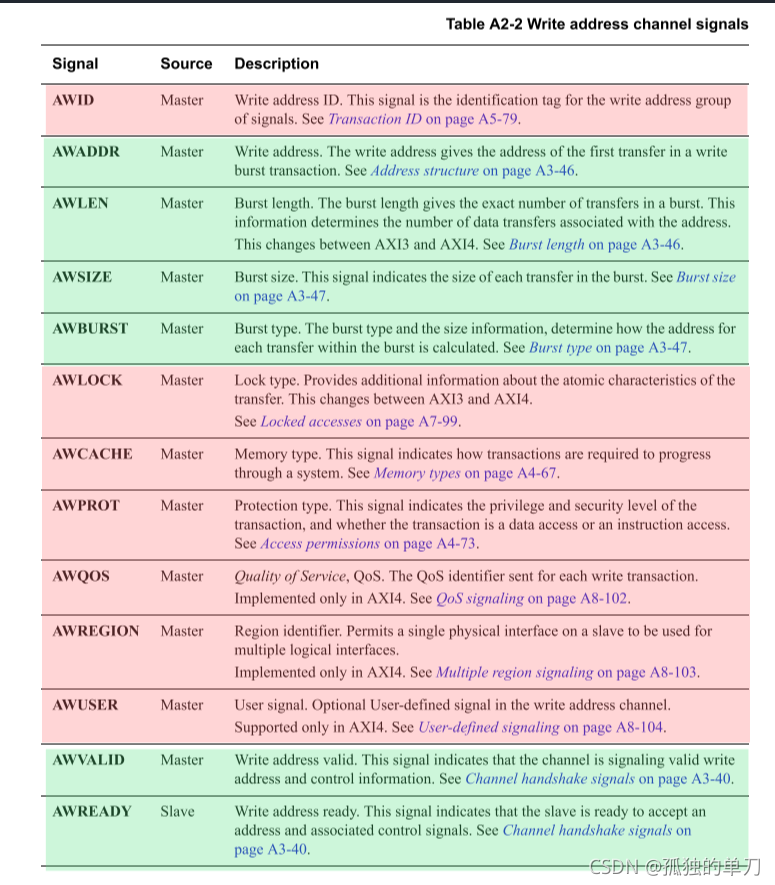

3.2、写地址通道信号(Write address channel signals)

上图中绿色是不可或缺的信号,红色是一些对内存或者原子操作的信号,基本上用不到(至少草鸟我暂时还用不到)。所以我这里只对绿色信号进行讲解,红色的信号可自行参阅ARM的手册。

该通道的信号均用AW作为前缀(address write):

AWADDR:写地址,给出一次写突发传输的写地址。主机到从机;

AWLEN :写传输的突发长度。主机到从机;

AWSIZE:写突发大小,给出每次突发传输的字节数。主机到从机;

AWBURST:突发类型。主机到从机;

AWVALID:有效信号,表明此通道的地址控制信号有效。主机到从机;

AWREADY:表明"从"可以接收地址和对应的控制信号。从机到主机。

3.3、写数据通道信号(Write data channel signals)

该通道的信号均用W作为前缀(write):

WDATA :写数据,主机到从机;

WSTRB :WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值,WVALID为高时,WSTRB为高的字节线必须指示有效的数据。主机到从机;

WLAST :表明此次传输是最后一个突发传输。主机到从机;

WVALID :写有效,表明此次写有效。主机到从机;

WREADY :表明从机可以接收写数据。从机到主机。

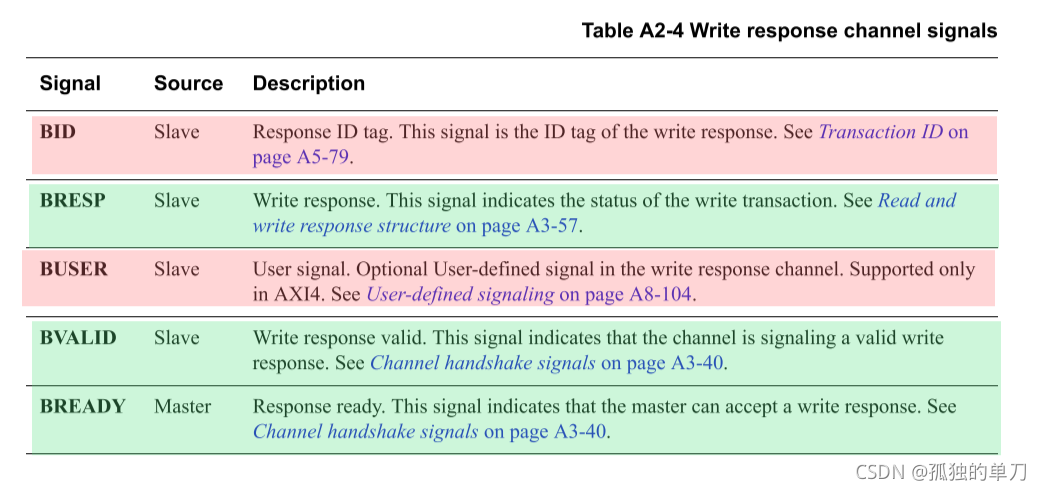

3.4、写响应通道信号(Write response channel signals)

该通道的信号均用B作为前缀(我也不知道B是什么意思,知道的可以告诉我):

BRESP :写响应,表明写传输的状态。从机到主机;

BVALID :写响应有效。从机到主机;

BREADY :表明主机能够接收写响应。主机到从机。

3.5、读地址通道信号(Read address channel signals)

该通道的信号均用AR作为前缀(address read):

ARADDR:读地址,给出一次读突发传输的读地址。主机到从机;

ARLEN:传输的突发长度。主机到从机;

ARSIZE:读突发大小,给出每次突发传输的字节数。主机到从机;

ARBURST:突发类型。主机到从机;

ARVALID:有效信号,表明此通道的地址控制信号有效。主机到从机;

ARREADY:表明"从"可以接收地址和对应的控制信号。从机到主机。

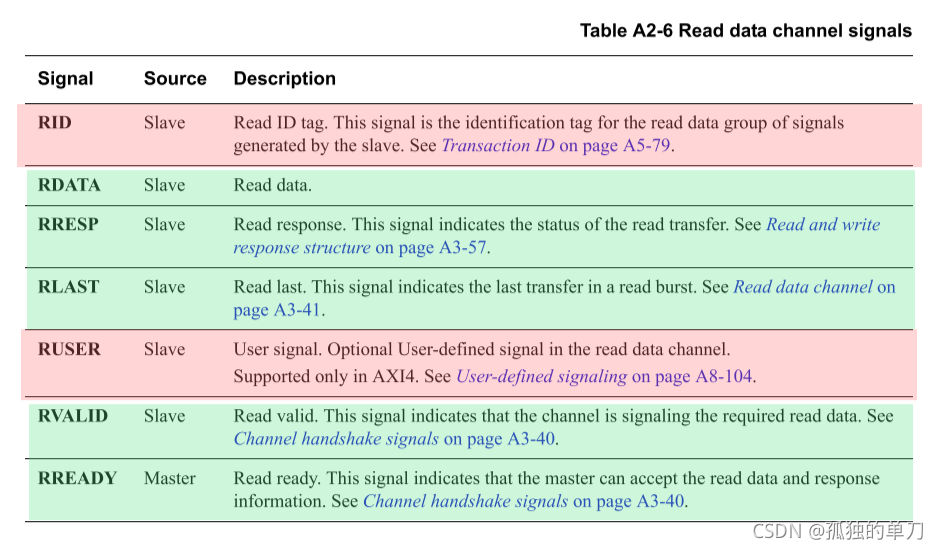

3.6、读数据通道信号(Read data channel signals)

该通道的信号均用R作为前缀(read):

RDATA:读到的数据。从机到主机;

RRESP :读响应,表明读传输的状态。从机到主机;

RLAST:表明此次传输是最后一个突发传输。从机到主机;

RVALID:读有效信号。从机到主机;

RREADY:表明"主机"可以接收从机发送的数据。主机到从机。

4、握手机制(handshake)

AXI 总线共有 5 个独立的通道,分别为写地址、写数据、写回应、读地址、读数据通道。5 条通道相互独立,有一些细小的差别,但共同使用一套握手机制:VALID/READY 机制,来实现信息的传递。

在握手机制中,通信双方分别扮演发送方(Source)和接收方(Destination),两者的操作(技能)并不相同。

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息已经就绪,并保持于消息总线上

接收方置高 READY 信号表示接收方已经做好接收的准备

当双方的 VALID/READY 信号同时为高,在时钟 ACLK 上升沿,完成一次数据传输。所有数据传输完毕后,双方同时置低自己的信号。所谓的双向流控机制,指的是发送方通过置起 VALID 信号控制发送的时机与速度,接收方也可以通过 READY 信号的置起与否控制接收速度。发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

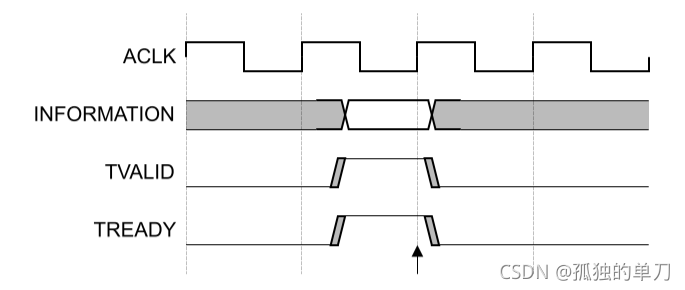

4.1、三种握手情况

VALID/READY 信号按照到达的先后顺序可以分为 3 种情况:

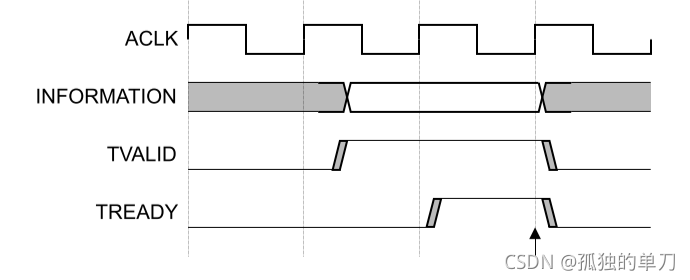

情况1:VALID信号先到达,READY信号后到达(主机先于从机做好了发送数据的准备)

主机先拉高TVALID信号--表明当前主机可以传送数据给从机,而TVALID一旦被拉高,则只能在从机进行响应传输了数据后才能拉低。从机在接收到主机发送的准备好的信号后,会对自身的情况做判断,判断自己是否具备了接收数据的准备,这也给了从机对数据流进行反压的能力,保证从机的接收处理能力不会瘫痪。一旦从机可以接收数据,便拉高TREADY信号,表明自己可以接收数据。此时TVALID && TREADY为高,在时钟的上升沿进行数据传输。

不妨举个接地气的例子(写的不好,有点俗套):

快递小哥(主机MASTER)拿了一车快递,准备全部送去小区的菜鸟驿站入库,与驿站值班小妹(从机SLAVE)对话如下:

小哥:老妹,我这来了一车快递,赶紧让我入库(主机可以发送数据,拉高TVALID)

小妹:你先别急,我这货架还没空出来呢!先让我整理整理(从机没有做好接收数据的准备)

小妹: 好了,大兄弟,你赶紧入库吧(从机可以接收数据,拉高TREADY)

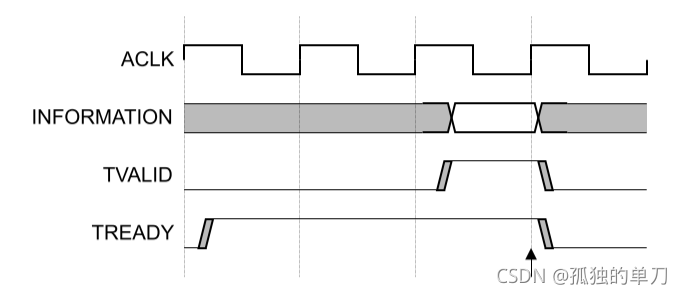

情况2:READY信号先到达,VALID 信号后到达(主机后于从机做好了发送数据的准备)

从机拉高TREADY信号,表明自己可以接收数据。主机会对自身的情况做判断,判断自己是否具备了发送数据的准备,一旦主机可以发送数据便拉高TVALID信号,此时TVALID && TREADY为高,在时钟的上升沿进行数据传输。

(依旧是俗套的例子)快递小哥(主机MASTER)拿了一车快递,准备全部送去小区的菜鸟驿站入库,与驿站值班小妹(从机SLAVE)对话如下:

小妹:大兄弟,你赶紧入库吧,我都等你半天了,不然早回家了(从机可以接收数据,拉高TREADY)

小哥:老妹,我这车快没电了,跑不快,再给我两分钟(主机没有做好发送数据的准备)

小哥:老妹,我终于来了,赶紧的吧(主机可以发送数据,拉高TVALID)

情况3:VALID、READY信号同时到达(主机、从机同时做好了传输数据的准备)

主机拉高TVALID信号的同时从机拉高TREADY信号,分别表明自己可以发送/接收数据,在时钟的上升沿进行数据传输。

(依旧是俗套的例子)快递小哥(主机MASTER)拿了一车快递,准备全部送去小区的菜鸟驿站入库,与驿站值班小妹(从机SLAVE)对话如下:

小妹:来了啊,大兄弟,赶紧的吧(从机可以接收数据,拉高TREADY)

小哥:哎哟我去,这不巧了吗,咱也刚到(同时主机也可以发送数据,拉高TVALID)

4.2、通道关系

各个通道之间基本是独立的,以下3种联系除外:

写回复必须在其所属传输的最后一个写数据完成后

读数据必须在接收到读地址信号后产生

通道间的握手需要满足通道间的握手依赖性(handshake dependencies)

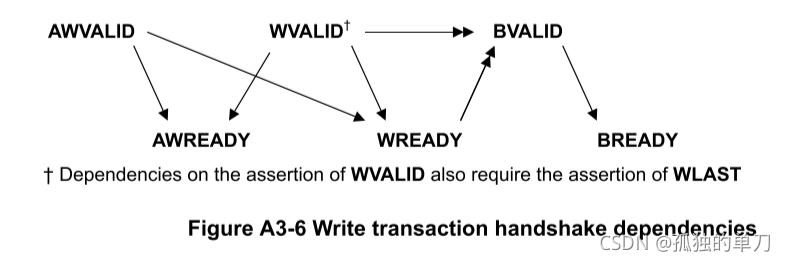

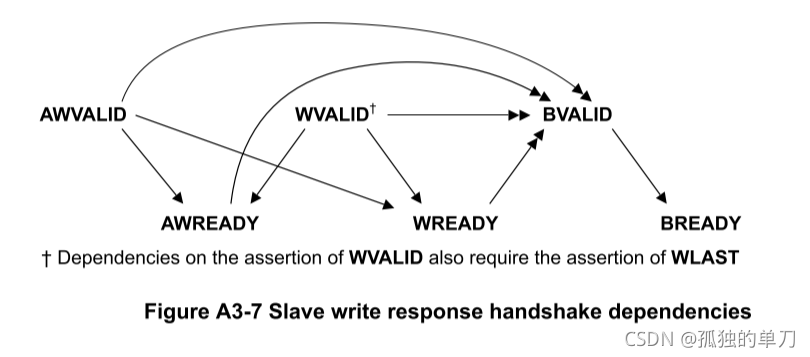

通道握手信号的依赖关系(Dependencies between channel handshake signals)

为了防止死锁(deadlock)情况的产生(如VALID信号等READY信号,而READY信号又在等VALID信号,这样就永远都没法握手),握手信号需满足以下规则:

发送方的VALID信号不能依赖READY信号来置位

接收方 READY 信号可以检测到 VALID 置位后再置位

以下是上述原则具体到各种情况的具体分析。

图中单箭头表示其指向的信号可以在箭头起始信号置位之前或之后置位或同时置位(无依赖);

图中的双头箭头表示:其指向的信号必须在箭头起始信号置位之后置位(指向信号依赖起始信号)

1、读事务的依赖性

主机的 ARVALID 信号禁止等待从机的 ARREADY 信号置位后才置位,防止死锁

从机的 ARREADY 信号可以先于主机、后于主机或同时于主机的 ARVALID 信号置位(如单头箭头所示),无依赖性

从机的 RVALID 信号必须等待 ARVALID 和 ARREADY 信号均置位后置位(如两个双头箭头所示),具有依赖性

从机的 RVALID 信号禁止等待主机的 RREADY 信号置位后才置位,防止死锁

主机的 RREADY 信号可以先于从机、从于主机或同时于从机的 RVALID 置位前置位(如单头箭头所示),无依赖性

2、写事务的依赖性

根据上节的分析内容,很容易对上图进行分析。这里只说下图中+号的含义:BVALID信号必须等待 WVALID 和WREADY 信号均置位后置位,同时还依赖WLAST信号的置位。这是因为BVALID信号是写响应有效信号,而我们知道一次写数据的数据使用WLAST信号来表征最后一个数据,也就是说WLAST在被置位之前,一次突发传输是没有结束的。

3、写响应的依赖性

不做具体分析,看箭头即可。

5、事务结构(Transaction structure)

1、突发传输(burst-based)

AXI4-Full是一种支持突发传输(BURST)的协议,而AXI4-Lite不支持突发传输,或者说突发长度为“1”。突发传输通俗来讲,就是一次只需要提供首地址,即可传输约定长度的数据。例如,首地址0X00,突发长度为8,那么一次就可以往地址0x00-0x07中一共写入8个数据。

典型的突发写时序如下:

典型的突发读时序如下:

2、突发长度(Burst length)

指一次突发传输的数据长度。读事务ARLEN[7:0];写事务AWLEN[7:0]。协议中的 AxLen 信号从零开始表示,实际的长度值为 AxLen + 1。即Burst_Length = AxLEN[7:0] + 1

突发传输须遵守以下规则:

WRAP传输类型(一次突发传输类型,后面会说)的突发长度只能是2,4,8,16

在一次突发传输中,地址不能跨越一个 4KB 分区

突发传输不能在完成所有数据传输前提前结束(early termination)

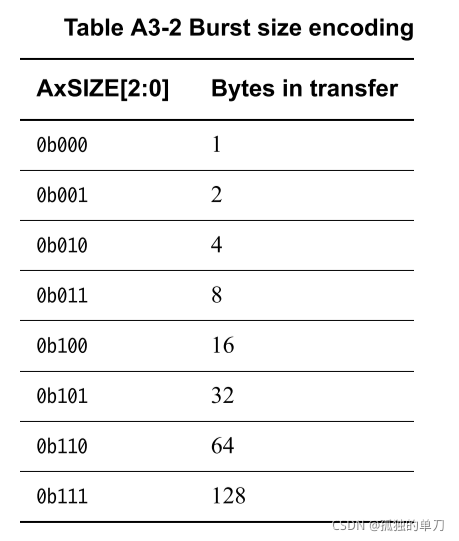

3、突发传输宽度(burst size)

指传输中的数据位宽,具体地,是每周期传输数据的字节数量,在协议中使用 AXSIZE 信号控制。突发传输宽度信号 AXSIZE 位宽为 3bit,表示为:传输宽度 = 2 ^ AXSIZE

具体如下:

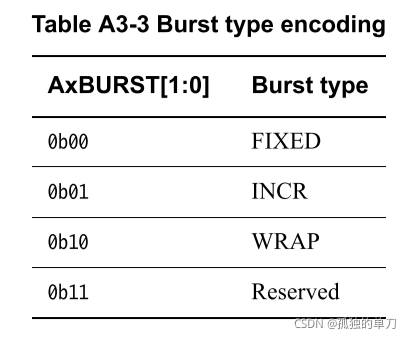

4、突发传输类型(Burst type)

共有 3 种,分别为 FIXED,INCR 以及 WRAP:

FIXED:每次传输事务的地址均为同一地址。该类型适合对同一地址进行反复操作,例如写入或者读出FIFO,其操作地址就是固定的。

INCR:增量突发,后续数据的地址在初始地址的基础上进行递增,递增幅度与传输宽度相同。适合对于 RAM 等通过地址映射(mapped memory)的存储介质进行读写操作,最为常用

WRAP:与增量突发类似,不过其地址增长到最高地址后会跳转到边界地址,再重新递增。适合对cache的访问

5、写选取(Write strobes)

WSTRB 信号中的单个 bit 置起,表示对应位置上的字节有效,对应关系为:WSTRB[n] 对应 WDATA[8n+7:8n],也就是:当 WSTRB[n] 为 1 时,WDATA[8n+7:8n]有效。WSTRB 信号比特位宽等于数据通道位宽的字节数量,比如 32bit 位宽的数据通道,对应 WSTRB 信号位宽为 4bit。

这个信号是用来实现掩码功能的,对于我们的一般应用,直接一直将其拉高,表示当前传输数据全部有效即可。

6、读、写响应(Read and write response)

响应值包括:

OKAY (0b00):正常访问成功。表示已成功完成正常访问

EXOKAY (0b01):专属访问成功。

SLVERR (0b10):从设备错误。已成功访问从设备,但从设备希望向发端主设备返回错误条件(例如,数据读取无效)。

DECERR (0b11):解码器错误。通常由互连组件生成,用于指示传输事务地址处没有任何从设备

其他

接下来介绍了解一下XILIX的验证IP----AXI Verification IP。