本文转载自:十年老鸟的CSDN博客

前言

srio 的IQ接口都是基于axistream的,以前没怎么用过axistream的接口,或者说没怎么用过复杂条件下的axistream的接口,今天就来总结和改造一下

包括以下信号

wire ireq_tvalid; wire ireq_tready; wire ireq_tlast; wire [63:0] ireq_tdata; wire [7:0] ireq_tkeep; wire [31:0] ireq_tuser;

axistream 一边是发送端,一边是接收端。

接收端的时序还比较好判断,只要判断tvalid准备好了,只要发送一个tready,那么tvalid和tready同时为高的时候,ireq_tdata就可以采集下来。

这几天的困惑在于发送端,发送端需要等待tready信号的指示,而且发送端并不知道下一个时钟周期的tready到底是高还是低。

同时,我希望写一个简单FIFO的接口来对接这个AXISTREAM接口,例如我希望我要发送的数据时序像写FIFO那么简单,至于FIFO和AXISTREAM之间能够自动进行转化,后面操作起来就方便了。

我给自己设置了一个条件:

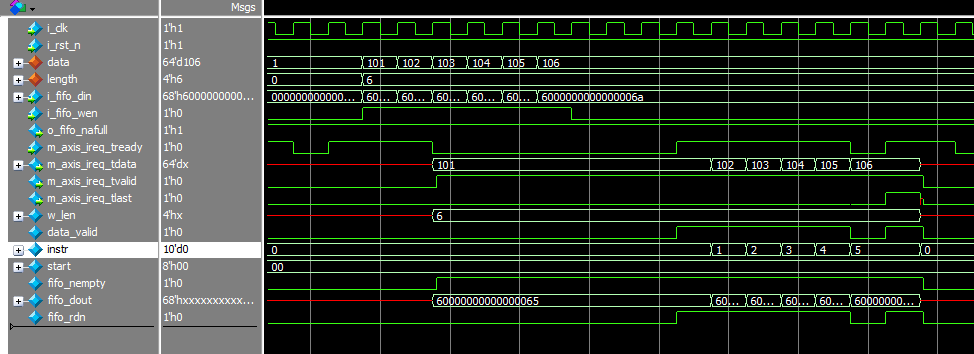

m_axis_ireq_tready <= {$random}%2;

也就是tready信号是随机的,需要在这种情况下能够完成接口的时序转化

接口转化

这两天我都困惑与这个矛盾,使用标准FIFO需要rdn之后数据才会出来,而输入的tready高低电平又是随机的,以至于我无法判断rdn之后的下一个时钟周期是否能够rdn。感觉很麻烦

目前我想到的方法就是

FIFO采用First Word Fall Through,且rdn之后下一个时钟周期需要出来数据。但Xilinx IP的最少也是rdn之后的下两个时钟才输数据,所以这个FIFO需要自己去设计。

之所以希望rdn之后下一个时钟周期需要出来数据。我是希望tvalid和tready同时为高的时候也作为rdn的使能,这样当前数据取走后,下一个时钟数据就又准备好了。

关于fifo_nempty,最后一个输入rdn之后,fifo_nempty下一个时钟要拉低。fifo_nempty指示为高的时候,同时fifo_dout也必须是有效的。

看起来似乎没问题