本文转载自:孤独的单刀的CSDN博客

这篇文章将讨论如何在 verilog 中使用不同的运算符,这些运算符提供了一种在 verilog 设计中处理数字数据的方法。这种处理方法非常简单----和简单的逻辑门一样,但是设计者可能还需要对数据执行复杂的逻辑或数学运算。

无论如何,verilog 提供了许多的运算符,使设计者能够对数据执行各种不同的计算或运算。

大多数情况下,设计者可以使用verilog的运算符来创建可以被综合的布尔表达式或逻辑电路,但是也有一些运算符写出的代码是无法被综合的。

所以接下来一起看看那些可以在 verilog 代码中使用的各类运算符吧。

1、Verilog 按位运算符(Bit Wise Operators)

按位运算符可以将多个1位输入组合成一个1位输出,verilog向量类型也使用按位运算符。最常用的方式是使用按位运算符在 verilog 中实现逻辑门。

以下是verilog 中使用的位运算符的完整列表。

下面的 verilog 代码展示了如何使用这些运算符。

y = ~a; y = a & b; y = a | b; y = a ~| b; y = a ~& b; y = a ^ b; y = a ~| b;

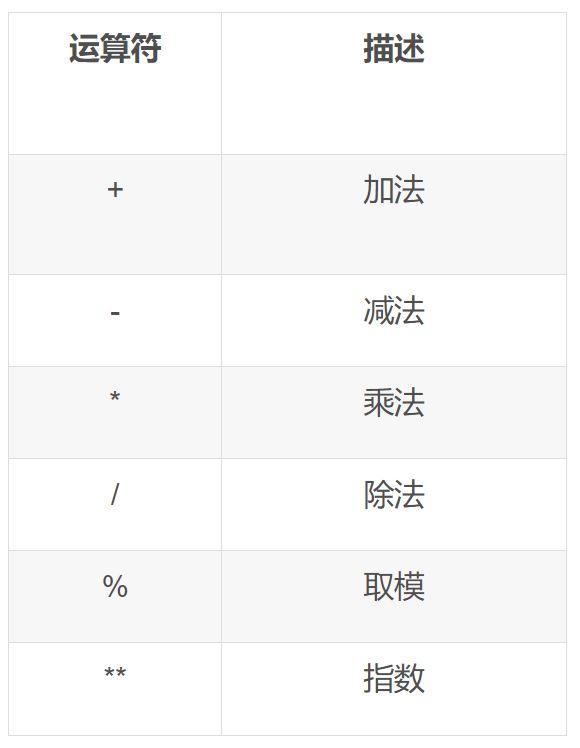

2、Verilog 算术运算符(Arithmetic Operators)

算术运算符可以用来实现基本的算术运算。这些运算符很眼熟,因为它们大多都是日常生活中常见的数学符号。

虽然大多数综合工具都可以综合加法(+)、减法(-)和乘法(*)运算符,但这通常会导致设计的逻辑性能欠佳。因此,必要时需要设计专门实现这些功能的逻辑电路,或者直接在 FPGA 中使用DSP模块来更有效地实现这些操作。

设计者应该尽量避免在代码中使用取模(%)、指数(**)或除法(/)运算符,因为大多数综合工具都无法直接将其综合成实际电路。

以下是verilog 中使用的算术运算符的完整列表。

下面的代码片段展示了如何使用这些运算符。

y = a + b; y = a - b; y = a * b; y = a / b; y = a % b; y = a ** b;

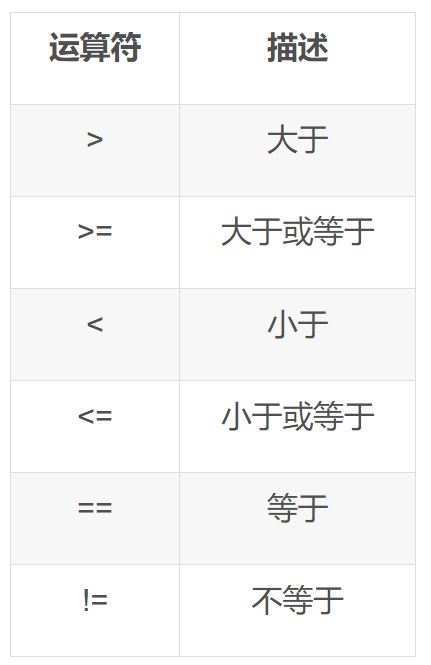

3、Verilog 关系运算符(Relational Operators)

关系运算符可以用来比较两个不同变量的值,比较的结果将返回逻辑值1或逻辑值0----分别代表 真(true) 和假(false) 。

这些运算符和其他编程语言(如C、Java)中的运算符很相似,其中的大部分在基础的数学表达式中也很常见。

以下是verilog 中使用的关系运算符的完整列表。

y = a > b; //如果a大于b则y值为1,否则y值为0 y = a >= b; //如果a大于或等于b则y值为1,否则y值为0 y = a < b; //如果a小于b则y值为1,否则y值为0 y = a <= b; //如果a小于或等于b则y值为1,否则y值为0 y = a == b; //如果a等于b则y值为1,否则y值为0 y = a != b; //如果a不等于b则y值为1,否则y值为0

4、Verilog 逻辑运算符(Logical Operators)

逻辑运算符和按位运算符类似。与关系运算符一样,这些表达式的结果是返回 1(真)或 0(假)。

同样,这些运算符类似于 C 或 Java 等语言中使用的运算符。在 verilog 中使用的逻辑运算符只有3个。

以下是verilog 中使用的逻辑运算符的完整列表。

下面的代码片段展示了如何使用这些运算符。注意在使用这些运算符时要使用括号来分隔表达式中的不同元素。

y = (a == b) && (c == d); //如果a等于b且c等于d,则y值为1;否则y值为0 y = (a == b) || (a == c); //如果a等于b且a等于c,则y值为1;否则y值为0 y = !(a == b); //如果a等于b则y值为0;否则y值为1

5、Verilog 移位运算符(Shift Operators)

除了已经看到的运算符之外,还有一些额外的运算符可以用于特定的逻辑函数。

其中最有用和最常用的一种是移位运算符,如下表所示。

在设计数字电路时,经常会用到移位操作。因此,verilog 提供了一种简单技术来实现这些功能----移位运算符。

移位运算符需要两个参数。第一个参数是要移动的信号,第二个参数是要移动的位数。

使用逻辑移位运算符时,在将信号移位所需位数后,所有的空白位置都用 0 填充。相反,算术移位运算符则保留移位信号的符号位。因此,它们只能与有符号(signed)类型一起使用。

算术左移和逻辑左移时,右边低位都会补 0。逻辑右移时,左边高位会补 0;而算术右移时,左边高位则会补充符号位,以保证数据缩小后值的正确性。

下面的代码片段展示了如何使用移位运算符。

a = a << 3; b = b >> 8; c = $signed(c) <<< 3; d = d >>> 5;

6、Verilog 条件运算符(Conditional Operators)

在Verilog中,条件运算符可以用来来根据条件语句将数据分配给不同的信号。

要使用条件运算符,需要在 ? 运算符之前写一个逻辑表达式,然后判断它是真还是假。根据表达式的真假将两个值中的某一个赋值给输出。

这个运算符可能很熟悉,因为它也用于其他编程语言,例如C和Java。

下面的代码片段展示了条件运算符的一般语法。

output = <condition> ? <true> : <false>

当 <condition> 中给出的表达式计算结果为真时,输出将是 <true> 中给出的值;如果条件表达式的计算结果为假,输出则是 <false> 中给出的值。

下面的代码片段展示了条件运算符的用法。

a = c > b ? c : b; //如果c大于b,则a等于c;否则a等于b

7、Verilog 拼接运算符(Concatenation Operators)和复制运算符(Replication Operators)运算符

这些运算符的输出都是向量,但这两个运算符的输入可以是单个位或向量。

这两个 verilog 运算符如下表所示。

使用 verilog 拼接运算符可以将两个或多个信号组合成一个向量。例如,有 2 个1bit的信号,设计者希望将它们组合起来用作多路选择器的地址。例如,下面的代码片段将产生一个值为 0011 的输出向量c。

c ={ 2'b00, 2'11};复制运算符可以将相同的值赋值给向量中的多个位。使用复制运算符时,必须指定想要复制的信号或值,以及想要复制它的次数。例如,下面的代码片段将产生一个值为 1111_1111 的输出向量c(1'b1被复制了8次)。

c = {8{1'b1}};下面的 verilog 代码展示了如何共同使用拼接运算符和复制运算符。

c = {a, {3{a,b}}}; //c = a_ab_ab_ab;