本文转载自:Vuko-wxh的CSDN博客

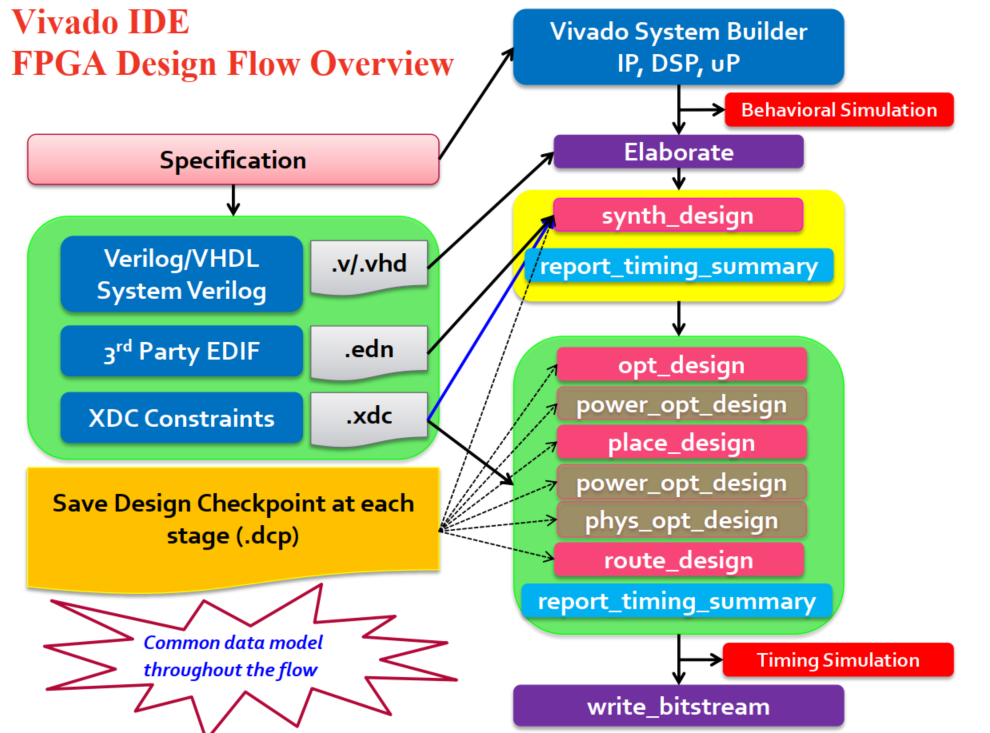

实现

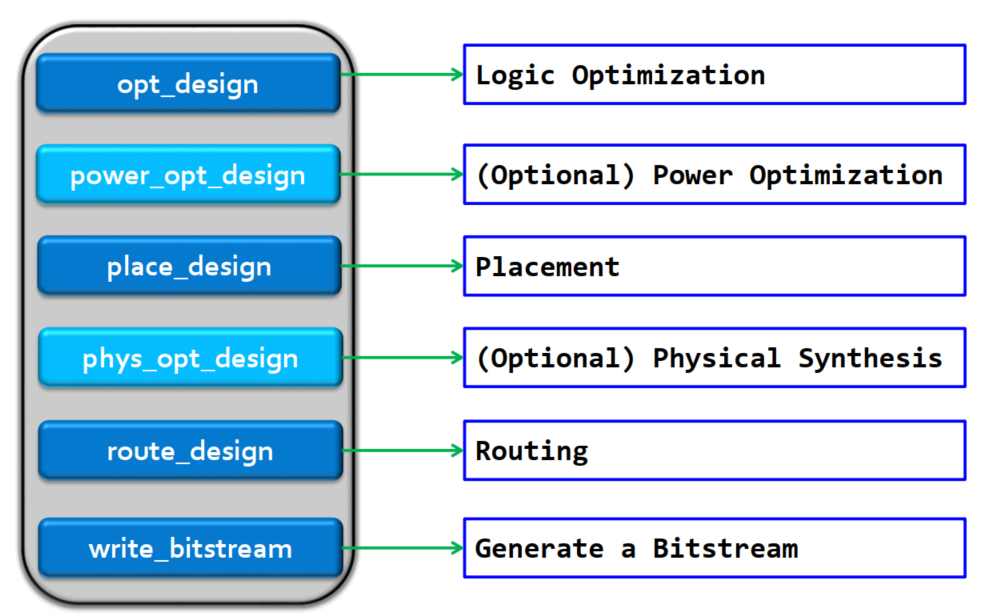

FPGA的实现过程可以对综合后生成的网表进行逻辑综合优化、以及布局、布线方面的优化。针对特定的设计可以进行选择功率以及物理综合设计进行优化。

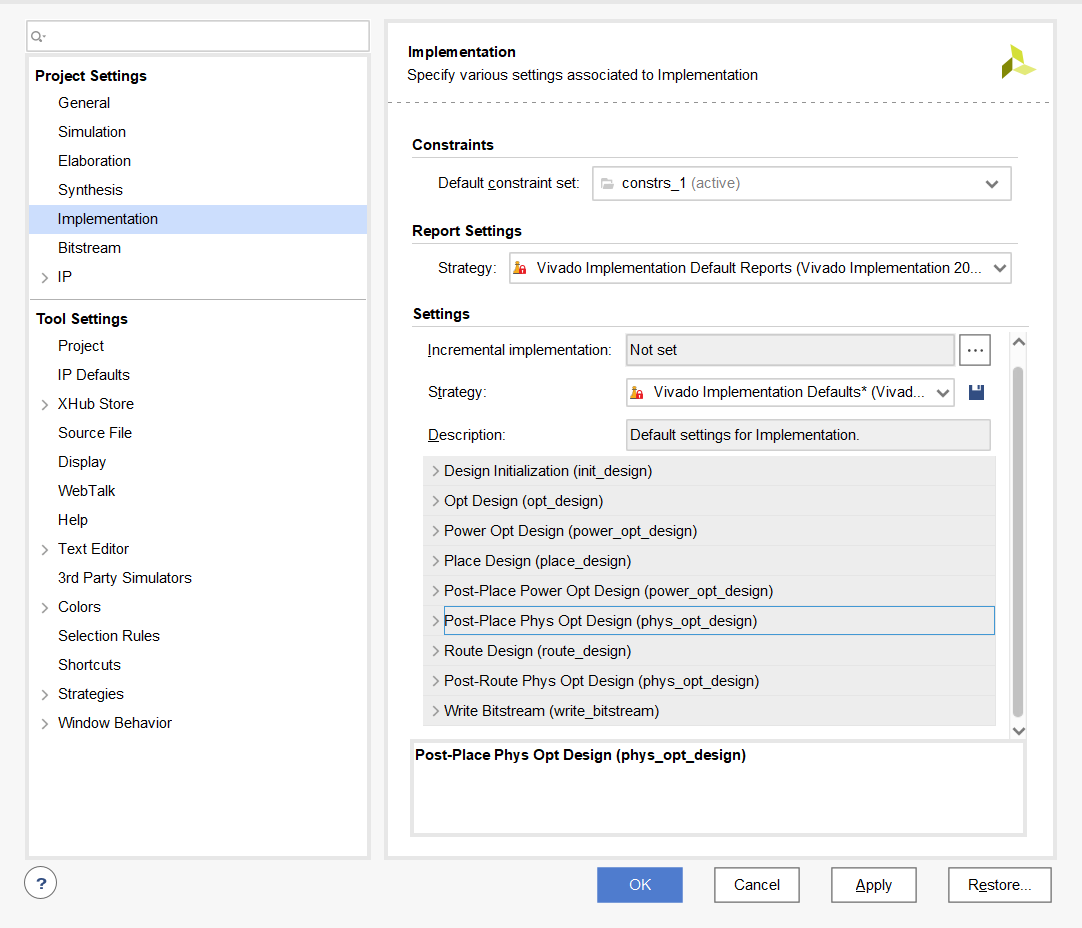

右键实现的选项,点击实现设置即可看到实现有关的配置界面,可以在设置中选择指定的约束文件,综合策略。

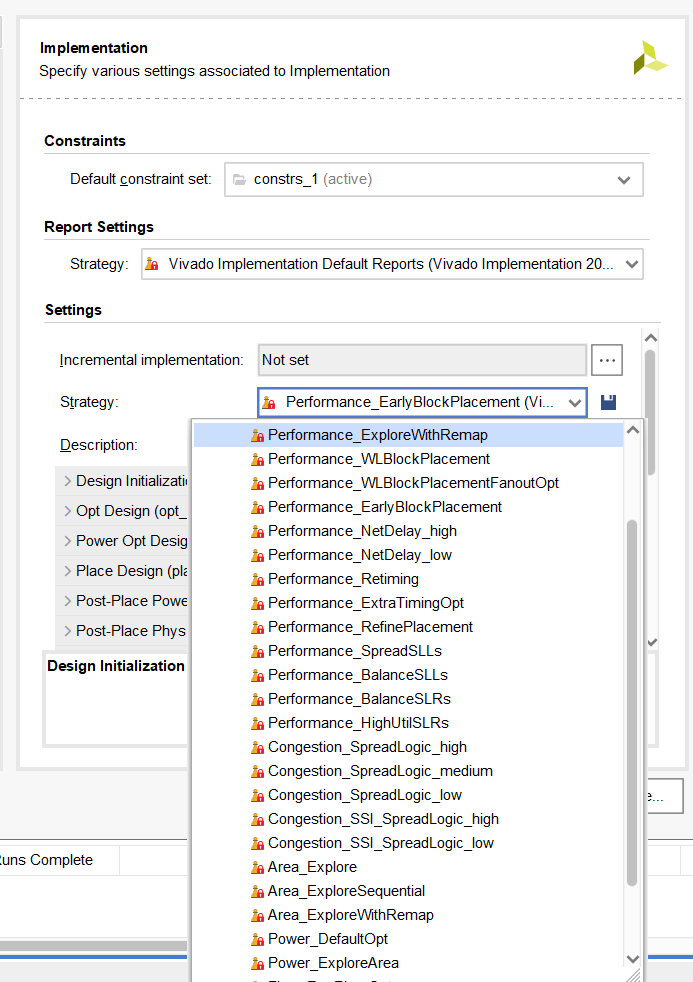

在strategy的下拉菜单中,可以针对不同的性能和指标要求尝试选择不同的策略应用与项目工程中。

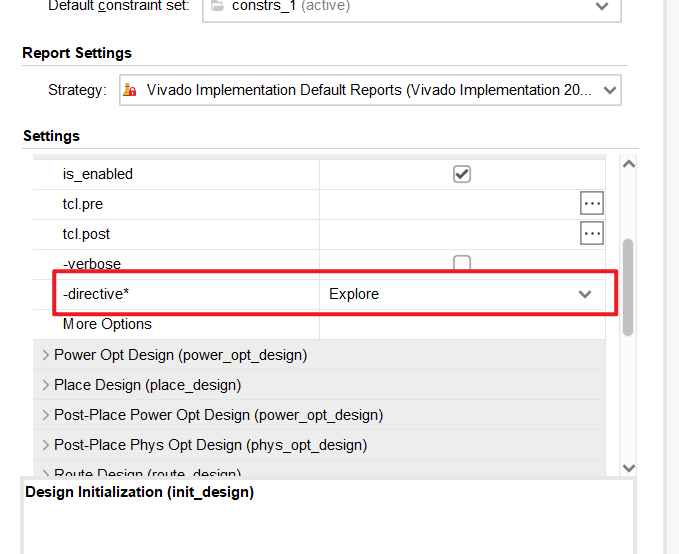

同时,在description中的各个部分也可以指定directive进行定制各个部分的实现方案。

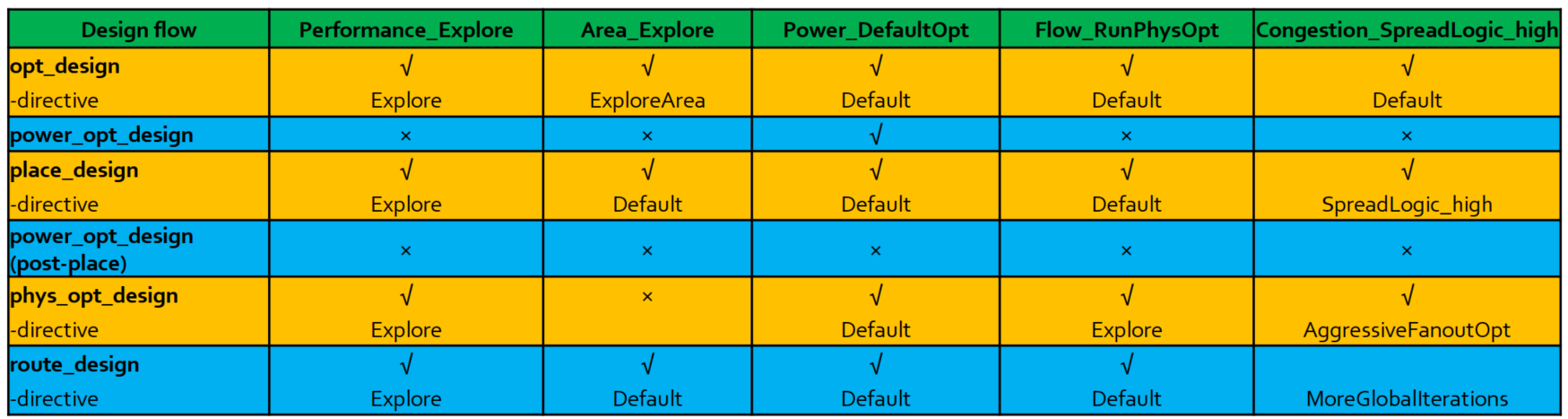

例如下表中为实现不同指标的优化,例如Area、Power、phys等,对各个阶段的directive的设计是不同的。

当实现策略中包含SLL或者SLR的术语,该策略只能在SSI设备中进行使用运行。

directive与strategy的区别

directive:是指定某一阶段的指令,用于定制某一阶段的优化策略和实现方法。

strategy:则是为了实现某个指标,而运行的一系列的directive,可以将strategy看做是一个对各个阶段的directive指定好的策略合集。

所以,针对不同策略来说,对应的各个阶段的directive可能是不同的,使用者可以在进行实现时,进行定制自己的实现策略。

建议:尝试Performance_Explore

Performance_Explore策略是一个很好的首选,因为它可以涵盖所有类型的设计。

当设计不太满足设计指标需求时,可以进行尝试使用Performance_Explore策略。但相比较而言带来的坏处就是,会增加大量的实现阶段的时间。

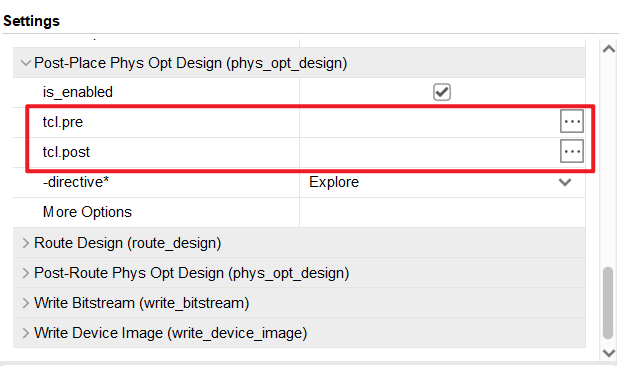

TCL 设计(pre、post)

针对各个步骤,可以通过tcl脚本进行指导运行,可实现针对某个阶段或者整个流程的管控。

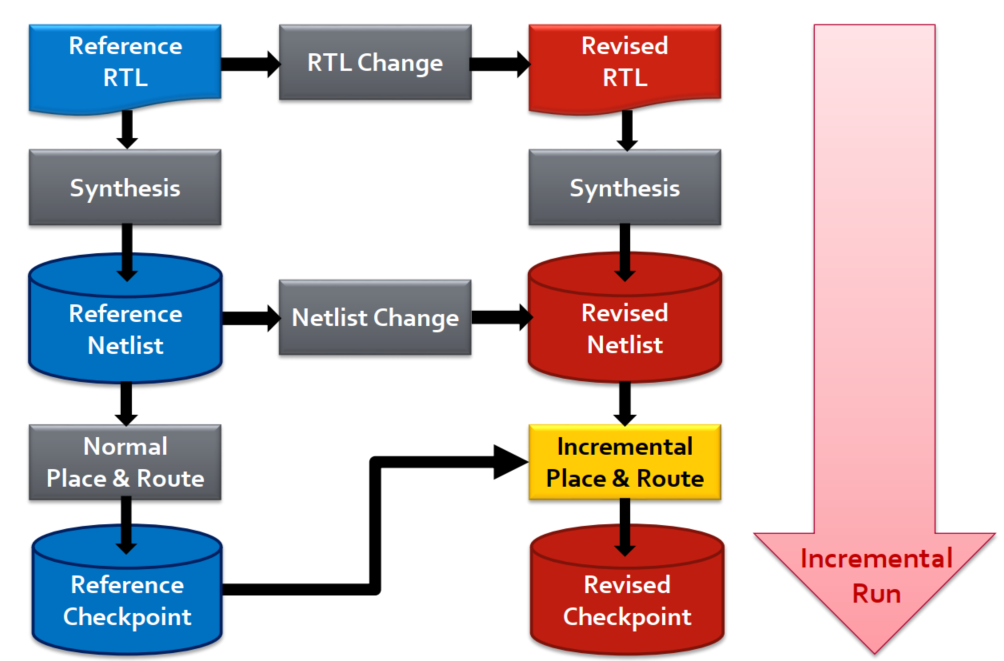

增量实现

传统的FPGA开发流程中,我们设计完成RTL代码,然后进行综合,实现。但是针对RTL在完成功能设计后,有些情况下检查发现只是部分逻辑功能有问题,需要做少量改变,此时,我之前的做法是将前面的过程再重复一遍…做过FPGA开发的都知道,工程规模的扩大,综合实现的时间在增加。很显然只改了一行RTL代码而编译整个工程,这样做是很蠢的。

因此,为了解决这一问题,赛灵思在工具中引入了增量实现的功能。该功能需要用到之前综合设计好dcp文件然后在实现阶段进行增量布局布线,从而实现对代码的微调的设计的快速实现。

增量实现的应用场景与好处

当改变的部分小于所使用的cell的5%时,可以使用增量实现的方式运行实现阶段的布局布线。

相比正常设计流程,布局布线的速度将会提升3倍左右。同时也会指导工具提供预测性更强的结果,此外也会更加利于时序收敛。

参考设计和当前设计

增量实现的参考设计是指当前设计的早期的迭代版本,他应该是已经作何布局布线后的设计,将会使用到布局布线后的dcp文件,如:XXXX_routed.dcp

当前设计是相比参考设计而言,进行了微小的设计调整和优化,这些设计优化可以是:

1. RTL的修改变化

2. 网表的修改变化

3. 同时修改的网表和RTL的工程设计

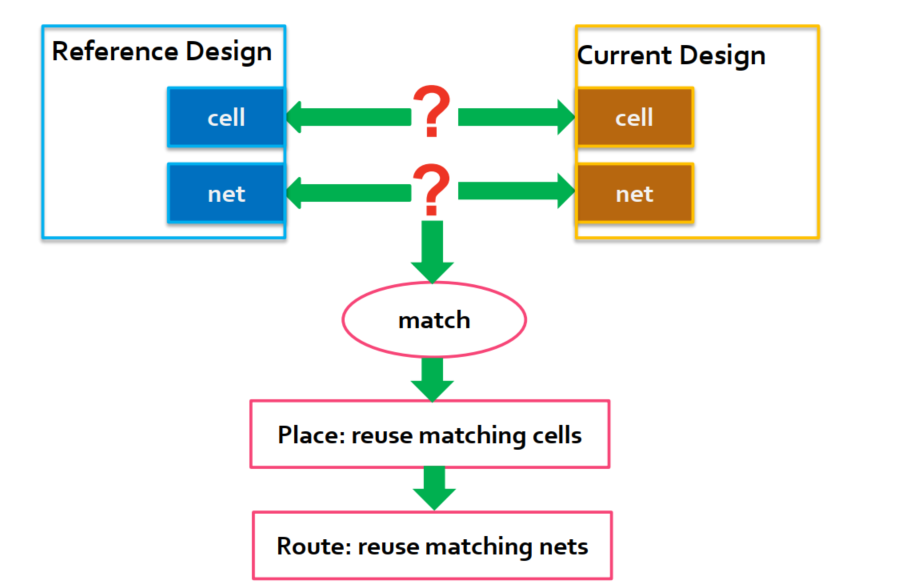

增量实现的运行机制

增量实现的运行过程,首先对参考设计以及当前设计的cell和net进行提取,然后进行对比比较,在布局布线中将会复用那些匹配的cells和nets的布局布线结果。

微小改变并不都适合增量实现

但对于增量设计而言,并不是所有的我们认为的微小调整都可以被增量布局布线所接受。

以下在设计部分对增量布局布线有很大影响:

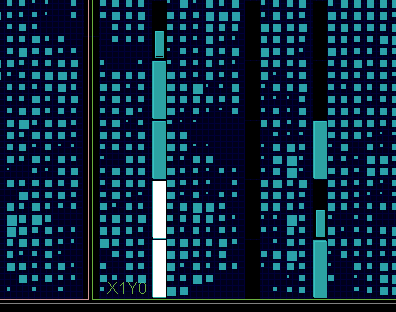

增加推断存储器的大小,个人觉得原因如下,因为存储器在实现过程中要涉及到多个的级联拼接,而对于BRAM实际在FPGA中的布局情况以及级联排列的相关规则,势必会给布线带来很大的难度,因此,该部分的修改不见得会将布局布线延时减小。下图展示的是一个BRAM存储器在实际设计中的布局情况,随着使用位宽和容量增大,会将RAM资源进行级联布线。

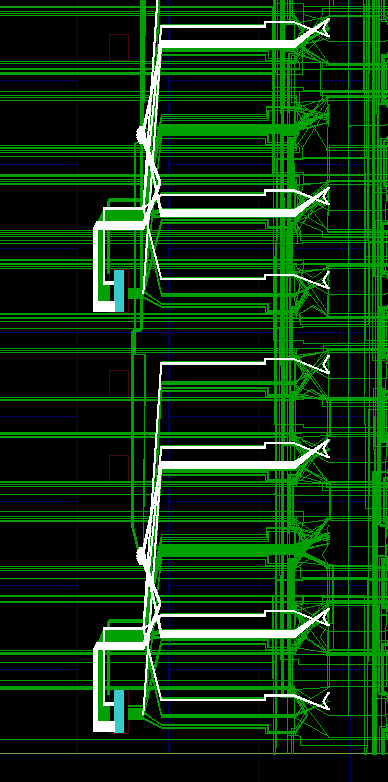

下图展示了部分bram布线情况。

拓展内部总线,类似改变存储器的情况。

将有符号数改成无符号数,将有符号数改成无符号数后,所有关于该数的运算都要进行重新考量和计算,因此会引入大量的布线布局布线改动。

改变约束和综合选项也可能会对增量布局布线带来影响:

1. 改变时序约束和重新综合

2. 保留或消除逻辑层次

3. 启用寄存器re-timing

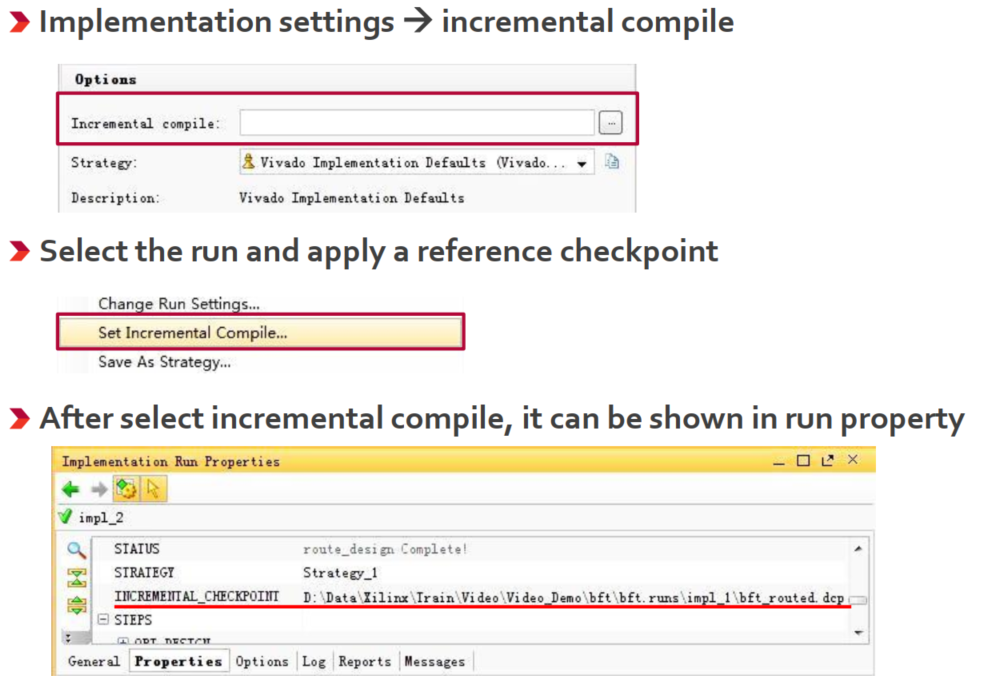

设置增量布局布线

在实现的选项栏中,可以找到设置增量实现的相关操作栏,可以指定参考的dcp文件,设置启用增量实现。

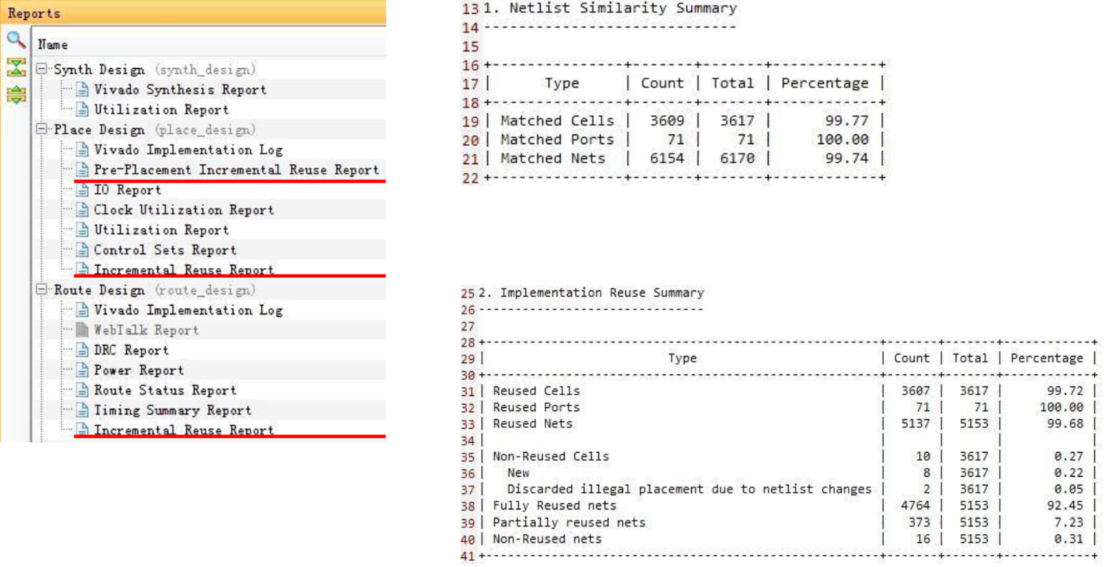

查看增量实现报告

在报告栏中,我们可以打开增量实现的报告用于查看复用的网络以及cell和port的数量和占比。

同时也可以在报告中查看当前路径的布局布线情况,确认在增量布局布线的设置下,该链路是否进行了重新布局布线的操作。使用report_timing/report_timing_summary –label_reused 可进行查看。

表示中的R、PNR用于指示该部分的状态,具体如下:

R:该部分进行了布局布线的复用。

NR:该部分都没有进行了布局布线的复用。

PNR:该部分复用了布局但是没有进行布线的复用。

N:该部分是新设计增加的对象。