版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/weixin_43813325/article/details/108476811

AURORA

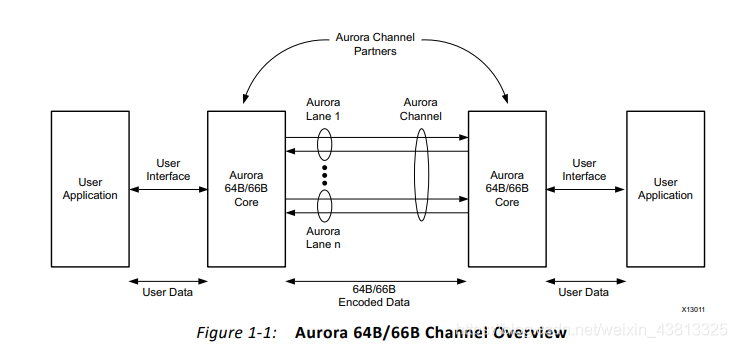

Aurora 协议是Xilinx公司针对高速传输开发的一种可裁剪的轻量级链路层协议,通过一条或多条串行链路实现两设备间的数据传输。Aurora协议可以支持流和帧两种数据传输模式,以及全双工、单工等数据通信方式,赛灵思提供8B/10B和64B/66B两种编码方式的IP CORE,其主要区别就是编码效率。

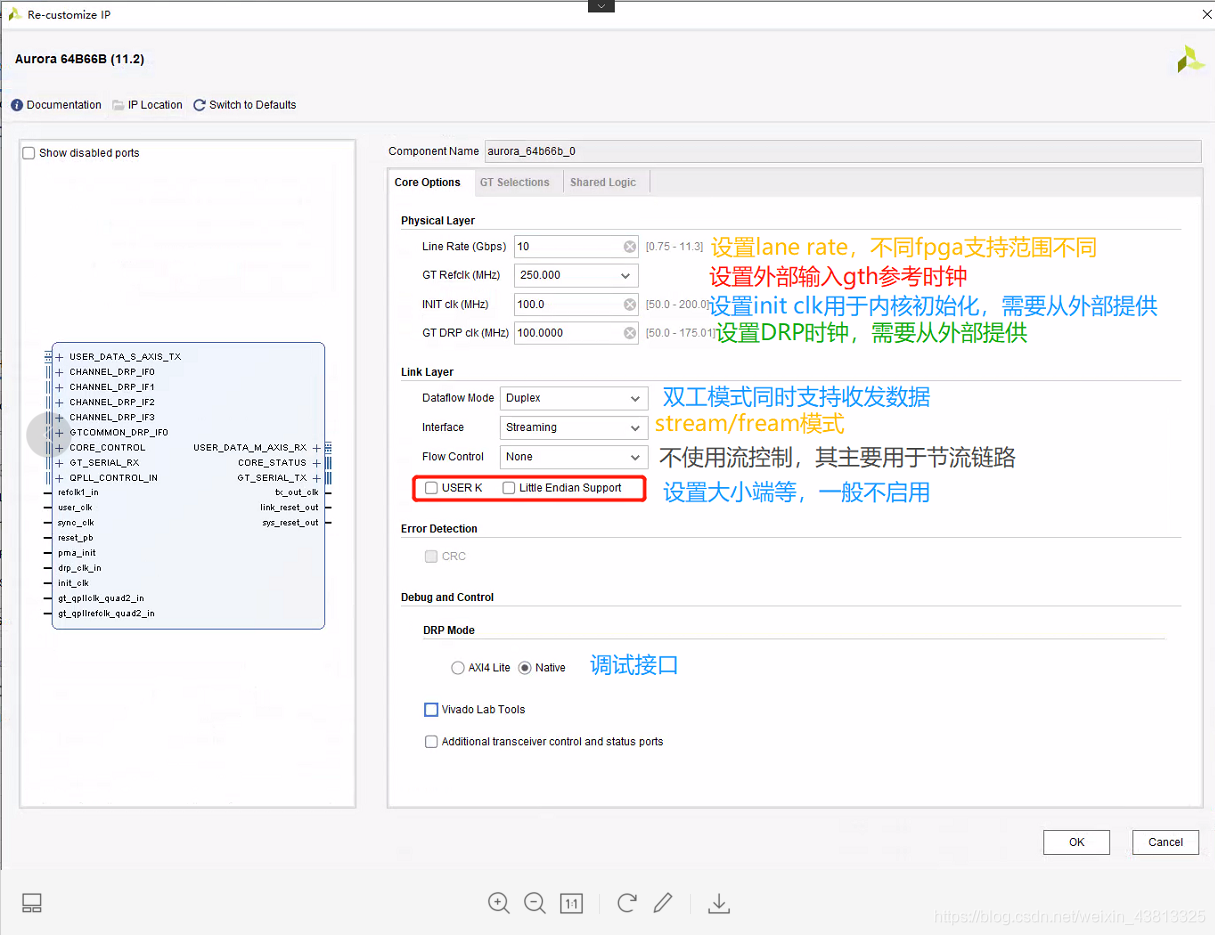

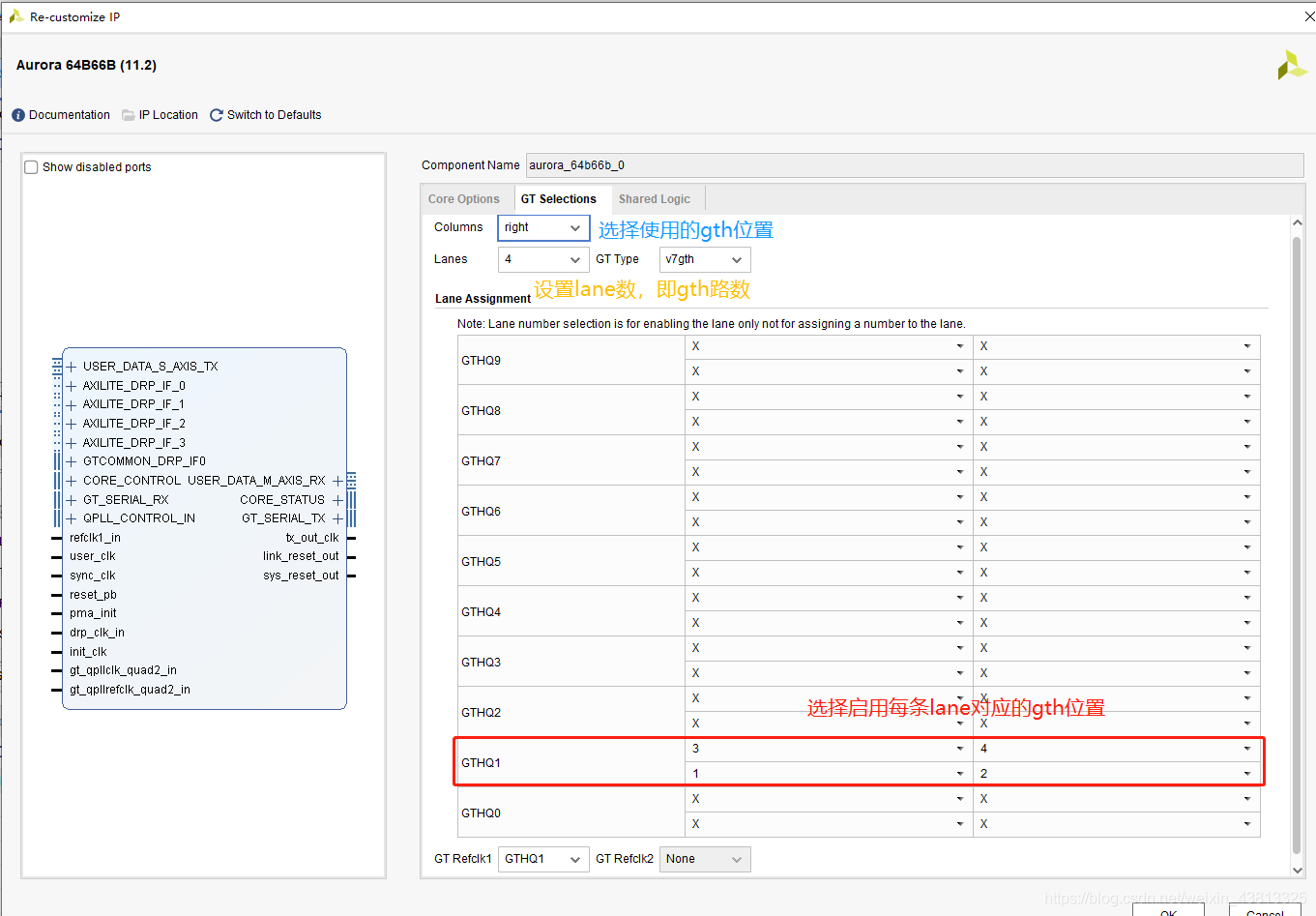

下面主要介绍64B/66B AURORA。

64B/66B AURORA如图所示,其是一种轻量级串行通信协议,用于设备间通过GTH/GTX/GTY收发器进行通信的串行协议,收发两端通过GTH/X/Y lane收发数据,支持双工数据通信。

对于收发端的64B/66B core来说,其内部包含以下部分:

1️⃣lane logic:控制GT 收发器各个lane初始化,处理编解码字符和错误检测。

2️⃣global logic:全局逻辑监控各个logic lane防止错误。

3️⃣rx user interface:用户接受数据接口。

4️⃣tx user interface:用户发送数据接口。

端口描述

aurora提供两种工作模式,其中FRAME模式可以传输任意大小的数据,允许被高优先级中断,可选节流控制可以用来节流链路。

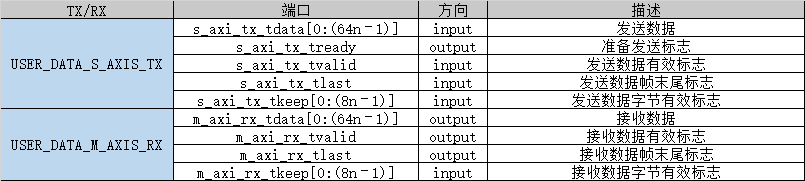

1️⃣ FRAME用户接口定义如下:

FRAME模式提供的端口如下所示:

FRAME mode example:

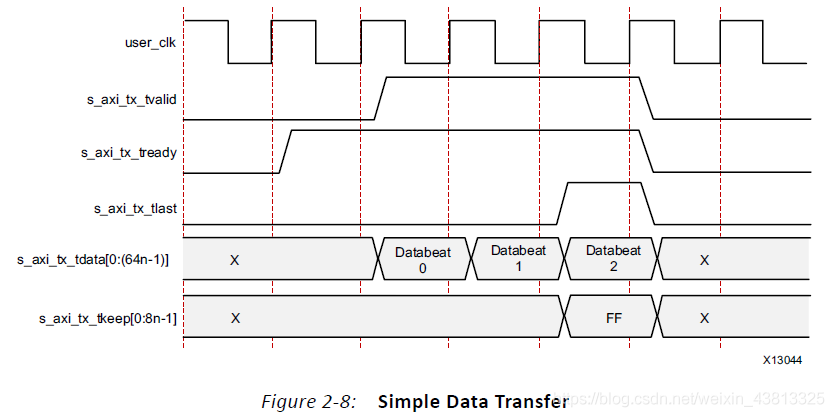

发送数据:

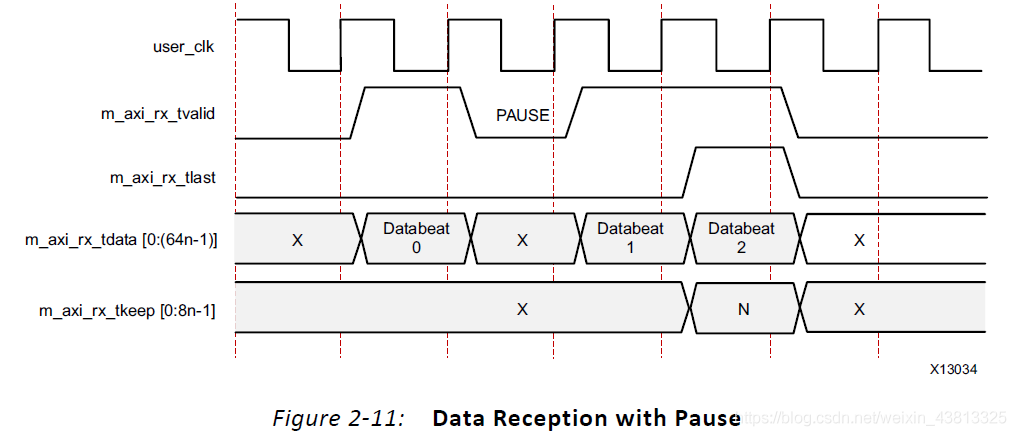

接收数据:

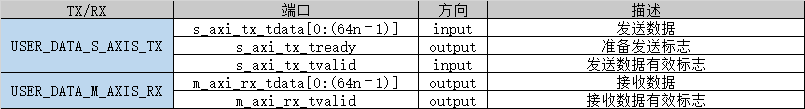

2️⃣ STREAM用户接口定义如下:

stream模式提供接口如下:

STREAM mode example:

发送数据:

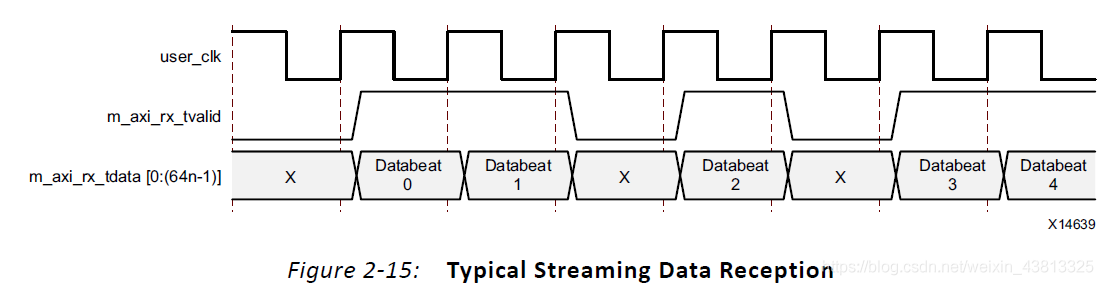

接收数据:

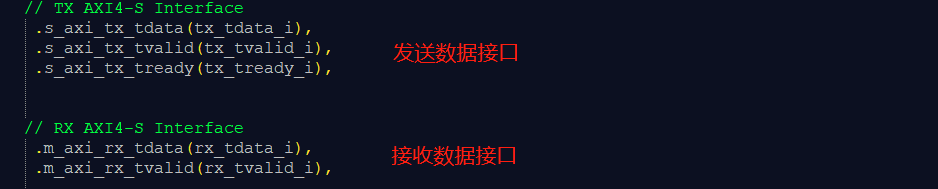

IP CORE调用(streaming模式)

调用example design

aurora_64b66b_0_support

u_aurora_64b66b_0_support

(

// TX AXI4-S Interface

.s_axi_tx_tdata(tx_tdata_i),

.s_axi_tx_tvalid(tx_tvalid_i),

.s_axi_tx_tready(tx_tready_i),

// RX AXI4-S Interface

.m_axi_rx_tdata(rx_tdata_i),

.m_axi_rx_tvalid(rx_tvalid_i),

// GT Serial I/O

.rxp(RXP),

.rxn(RXN),

.txp(TXP),

.txn(TXN),

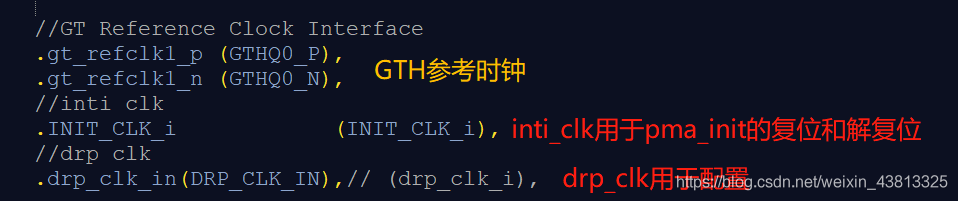

//GT Reference Clock Interface

.gt_refclk1_p (GTHQ0_P),

.gt_refclk1_n (GTHQ0_N),

//inti clk

.INIT_CLK_i (INIT_CLK_i),

//drp clk

.drp_clk_in(DRP_CLK_IN),// (drp_clk_i),

// Error Detection Interface

.hard_err (hard_err_i),

.soft_err (soft_err_i),

// Status

.channel_up (channel_up_i),

.lane_up (lane_up_i),

// System Interface

//.init_clk_out (INIT_CLK_i),

.user_clk_out (user_clk_i),

.sync_clk_out(sync_clk_i),

.reset_pb(reset_i),

.gt_rxcdrovrden_in(gt_rxcdrovrden_i),

.power_down(power_down_i),

.loopback(loopback_i),

.pma_init(gt_reset_i),

.gt_pll_lock(gt_pll_lock_i),

// .drp_clk_in(DRP_CLK_IN),// (drp_clk_i),

// ---------- AXI4-Lite input signals ---------------

.s_axi_awaddr(s_axi_awaddr_i),

.s_axi_awvalid(s_axi_awvalid_i),

.s_axi_awready(s_axi_awready_i),

.s_axi_awaddr_lane1(s_axi_awaddr_lane1_i),

.s_axi_awvalid_lane1(s_axi_awvalid_lane1_i),

.s_axi_awready_lane1(s_axi_awready_lane1_i),

.s_axi_awaddr_lane2(s_axi_awaddr_lane2_i),

.s_axi_awvalid_lane2(s_axi_awvalid_lane2_i),

.s_axi_awready_lane2(s_axi_awready_lane2_i),

.s_axi_awaddr_lane3(s_axi_awaddr_lane3_i),

.s_axi_awvalid_lane3(s_axi_awvalid_lane3_i),

.s_axi_awready_lane3(s_axi_awready_lane3_i),

.s_axi_wdata(s_axi_wdata_i),

.s_axi_wstrb(s_axi_wstrb_i),

.s_axi_wvalid(s_axi_wvalid_i),

.s_axi_wready(s_axi_wready_i),

.s_axi_bvalid(s_axi_bvalid_i),

.s_axi_bresp(s_axi_bresp_i),

.s_axi_bready(s_axi_bready_i),

.s_axi_wdata_lane1(s_axi_wdata_lane1_i),

.s_axi_wstrb_lane1(s_axi_wstrb_lane1_i),

.s_axi_wvalid_lane1(s_axi_wvalid_lane1_i),

.s_axi_wready_lane1(s_axi_wready_lane1_i),

.s_axi_bvalid_lane1(s_axi_bvalid_lane1_i),

.s_axi_bresp_lane1(s_axi_bresp_lane1_i),

.s_axi_bready_lane1(s_axi_bready_lane1_i),

.s_axi_wdata_lane2(s_axi_wdata_lane2_i),

.s_axi_wstrb_lane2(s_axi_wstrb_lane2_i),

.s_axi_wvalid_lane2(s_axi_wvalid_lane2_i),

.s_axi_wready_lane2(s_axi_wready_lane2_i),

.s_axi_bvalid_lane2(s_axi_bvalid_lane2_i),

.s_axi_bresp_lane2(s_axi_bresp_lane2_i),

.s_axi_bready_lane2(s_axi_bready_lane2_i),

.s_axi_wdata_lane3(s_axi_wdata_lane3_i),

.s_axi_wstrb_lane3(s_axi_wstrb_lane3_i),

.s_axi_wvalid_lane3(s_axi_wvalid_lane3_i),

.s_axi_wready_lane3(s_axi_wready_lane3_i),

.s_axi_bvalid_lane3(s_axi_bvalid_lane3_i),

.s_axi_bresp_lane3(s_axi_bresp_lane3_i),

.s_axi_bready_lane3(s_axi_bready_lane3_i),

.s_axi_araddr(s_axi_araddr_i),

.s_axi_arvalid(s_axi_arvalid_i),

.s_axi_arready(s_axi_arready_i),

.s_axi_araddr_lane1(s_axi_araddr_lane1_i),

.s_axi_arvalid_lane1(s_axi_arvalid_lane1_i),

.s_axi_arready_lane1(s_axi_arready_lane1_i),

.s_axi_araddr_lane2(s_axi_araddr_lane2_i),

.s_axi_arvalid_lane2(s_axi_arvalid_lane2_i),

.s_axi_arready_lane2(s_axi_arready_lane2_i),

.s_axi_araddr_lane3(s_axi_araddr_lane3_i),

.s_axi_arvalid_lane3(s_axi_arvalid_lane3_i),

.s_axi_arready_lane3(s_axi_arready_lane3_i),

.s_axi_rdata(s_axi_rdata_i),

.s_axi_rvalid(s_axi_rvalid_i),

.s_axi_rresp(s_axi_rresp_i),

.s_axi_rready(s_axi_rready_i),

.s_axi_rdata_lane1(s_axi_rdata_lane1_i),

.s_axi_rvalid_lane1(s_axi_rvalid_lane1_i),

.s_axi_rresp_lane1(s_axi_rresp_lane1_i),

.s_axi_rready_lane1(s_axi_rready_lane1_i),

.s_axi_rdata_lane2(s_axi_rdata_lane2_i),

.s_axi_rvalid_lane2(s_axi_rvalid_lane2_i),

.s_axi_rresp_lane2(s_axi_rresp_lane2_i),

.s_axi_rready_lane2(s_axi_rready_lane2_i),

.s_axi_rdata_lane3(s_axi_rdata_lane3_i),

.s_axi_rvalid_lane3(s_axi_rvalid_lane3_i),

.s_axi_rresp_lane3(s_axi_rresp_lane3_i),

.s_axi_rready_lane3(s_axi_rready_lane3_i),

//---------------------- GTXE2 COMMON DRP Ports ----------------------

.qpll_drpaddr_in(qpll_drpaddr_in_i),

.qpll_drpdi_in(qpll_drpdi_in_i),

.qpll_drpdo_out (qpll_drpdo_out_i),

.qpll_drprdy_out (qpll_drprdy_out_i),

.qpll_drpen_in (qpll_drpen_in_i),

.qpll_drpwe_in (qpll_drpwe_in_i),

// .INIT_CLK_i (INIT_CLK_i),

//.init_clk_n (1'b0),

.link_reset_out (link_reset_i),

.mmcm_not_locked_out (pll_not_locked_i),

.sys_reset_out (system_reset_i),

.tx_out_clk (tx_out_clk_i)

);

时钟端口描述

复位端口描述

数据端口描述