本文转载自:FpgaHome微信公众号

ZYNQ芯片主要由PS端(ARM处理器)和PL端(FPGA逻辑单元)组成,因此ZYNQ芯片结合了ARM芯片和FPGA芯片的优点于一身。本实验主要介绍使用PS端来完成ZYNQ串口打印输出的功能。

虽然本实验仅仅使用了PS,但是还要建立一个Vivado工程,用来配置PS管脚。虽然PS端的ARM是硬核,但是在ZYNQ当中也要将ARM硬核添加到工程当中才能使用。本实验使用的Vivado版本为Vivado2021.1。

1. Vivado工程的建立

(1)打开Vivado,创建一个名为“Uart_HelloWorld”的工程;

(2)点击“Create Block Design”,创建一个Block设计,也就是图形化设计;

(3)进入到“Block Design”界面后,点击“Add IP”按钮,搜索“zynq”,在搜索结果列表中双击“ZYNQ7 Processing System”;

(4)双击Block图中的“processing_system7_0”(即zynq的PS端IP核),配置该IP核的参数;

(5)首先出现的界面是ZYNQ硬核的架构图,可以很清楚看到它的结构,可以参考ug585文档,里面有对ZYNQ的详细介绍。图中绿色部分是可配置模块,可以点击进入相应的编辑界面,当然也可以在左侧的窗口进入编辑。

(6)本教程使用的ZYNQ开发板为ZerdBoard,该开发板使用J14串口用于数据传输,电路图如下图所示,可知该串口的FPGA端接口为MIO48、MIO49。

(7)选择“Peripheral I/O Pins”选项卡,勾选“UART1”;

(8)选择“MIO Configuration”选项卡,设置好Bank0 I/O Voltage和Bank1I/O Voltage;ZedBoard的Bank0 I/O Voltage设为LVCMOS 3.3V、Bank1 I/O Voltage设为LVCMOS 1.8V。

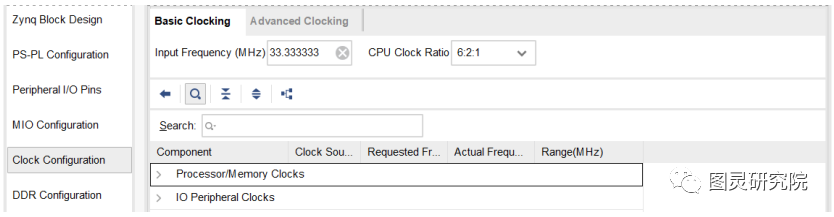

(9)选择“Clock Configuration”选项卡,根据ZerdBoard板卡配置,Input Frequency(MHz)设置为33.333333MHz,CPU Clock Ratio默认为6:2:1。

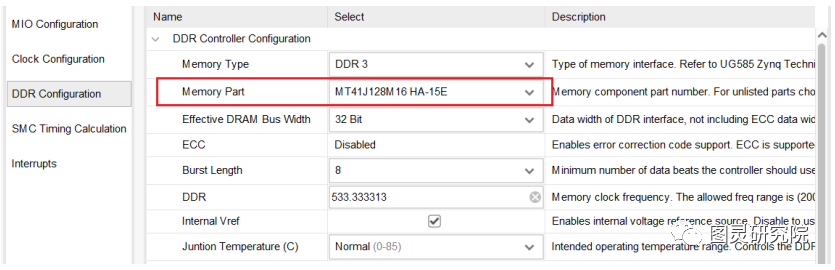

(10)选择“DDR Configuration”选项卡,根据ZerdBoard板卡配置,DDR型号选择为MT41J128M16HA-15E。

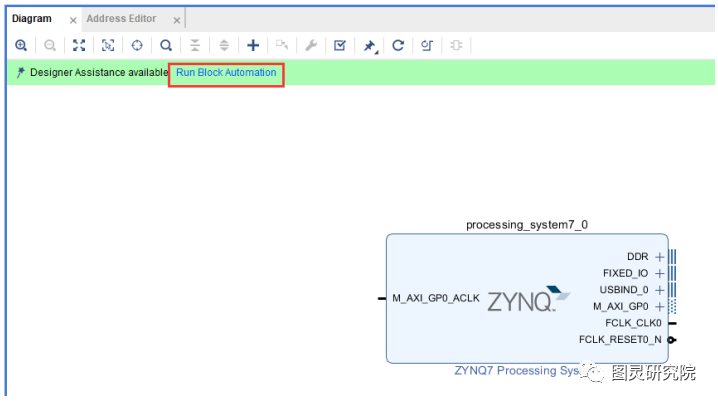

(11)点击“OK”按钮,完成该IP核的配置。点击“Run Block Automation”, Vivado软件会自动完成一些导出端口的工作。

(12)按照默认点击“OK”,不更改任何参数。

(13)点击“OK”以后我们可以看到PS端导出一些管脚,包括DDR还有FIXED_IO,DDR是DDR3的接口信号,FIXED_IO为PS端固定的一些接口,比如输入时钟,PS端复位信号,MIO等。连接FCLK_CLK0到M_AXI_GP0_ACLK,按“Ctrl+S”保存设计。

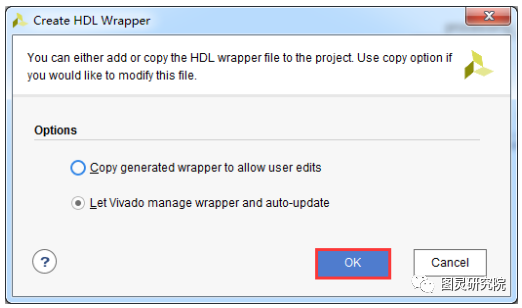

(14)选择Block设计,右键“Create HDL Wrapper...”,创建一个Verilog或VHDL 文件,为block design生成HDL顶层文件。

(15)保持默认选项,点击“OK”

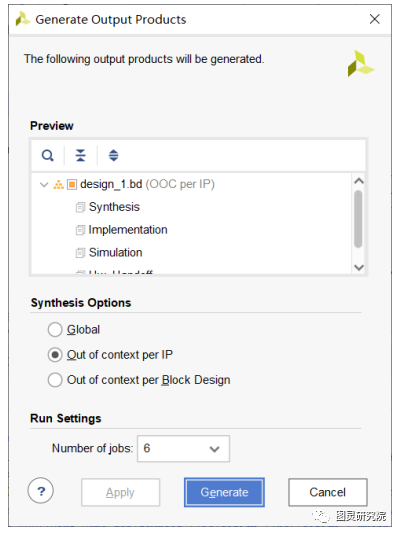

(16)展开设计可以看到PS被当成一个普通IP来使用。选择block设计,右键“Generate OutputProducts”,此步骤会生成block的输出文件,包括IP,例化模板,RTL源文件,XDC约束,第三方综合源文件等等。供后续操作使用。

(17)弹出的窗口直接安装默认设置,点击“Generate”。

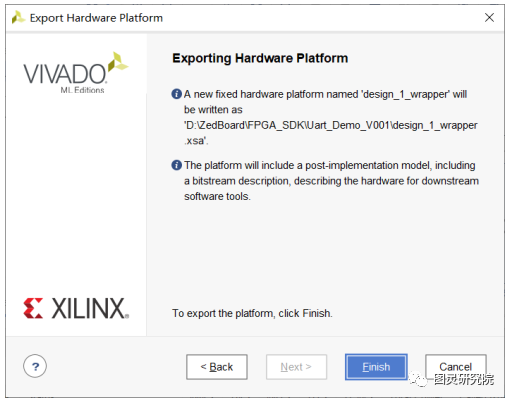

(18)点击Vivado “Flow Navigator”一栏里的“Generate Bitstream”,等待Vivado生成好bit文件后,在菜单栏“File -> Export -> Export Hardware...”导出硬件信息,这里就包含了PS端的配置信息。

(19)在弹出的对话框中勾选“Include bitstream”并点击“Next”以及“Finished”。

(20)到此为止,Vivado的工作告一段落,Vivado最后导出了一个硬件平台的XSA文件。软件开发工程师用该XSA文件便可以脱离Vivado软件环境对上层应用软件进行开发。

2.Vitis(SDK)工程的建立和调试

在Vivado早期的版本中,软件工程师的开发是在SDK软件中进行的,Vivado目前最新的版本(例如Vivado 2021.1)已将原来的SDK软件升级为Vitis软件。

(1)点击 Vivado 菜单“Tools-> Launch VitisIDE”,启动 Vitis。

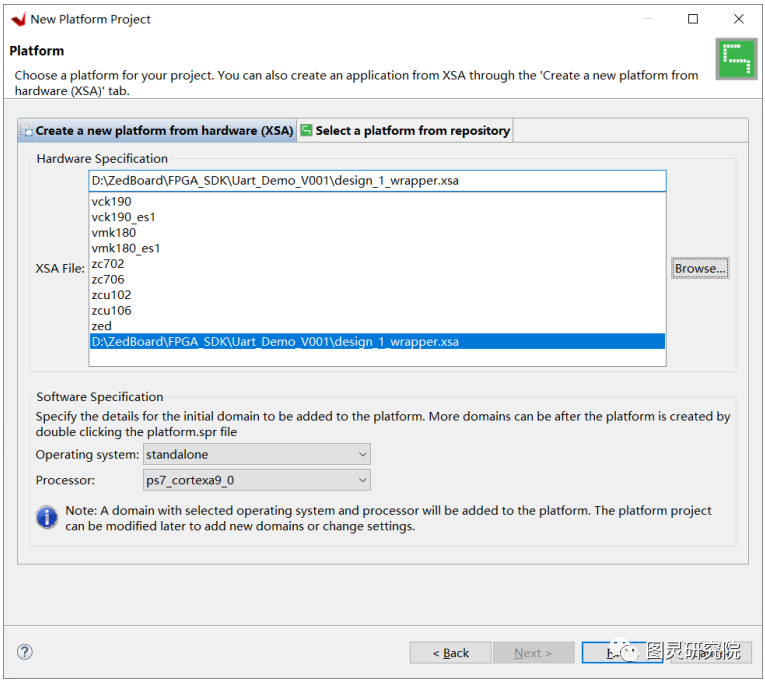

(2)首先我们要建立一个平台工程。这个平台工程即对应于我们刚刚在Vivado下搭的硬件平台。点击Vitis菜单“File-> New->Platform Project…”。

(3)工程命名“Zynq7000_Platform”,并点击下一步。

(4)点击“Browse…”指定硬件平台文件,即我们刚用Vivado最后导出的硬件平台配置XSA文件。点击完成。

(5)可以在项目的游览窗口里看到刚建立的平台工程文件夹。

(6)建立好平台工程后,我们再建立一个应用工程,该工程即实现串口打印“Hello World”信息。点击Vitis菜单“File-> New->Application Project…”,并点击下一步。

(7)选中我们刚建好的“Zynq7000_Platform”平台工程,并点击下一步。

(8)给应用工程取个名字,并点击下一步。

(9)从应用工程模板里,选择“Hello World”工程,点击“Finish”按钮。

(10)分别编译平台工程和应用工程。

(11)至此,我们完成了所有SDK软件的配置和开发工作。

3.下载程序至开发板

(1)作者使用的开发板为ZedBoard开发板,板卡上的跳线帽MIO2~MIO6都接地,如下图所示。板卡和计算机之间连好JTAG下载线和串口线(USB转串口),给板卡上电。

(2)Vitis下点击“Run Configurations…”

(3)点击“Single Application Debug(GDB)”,在“Application”选项卡中勾选“ps7_cortexa9_0”,点击“Run”按钮。

(4)程序运行成功后,便会在计算机的串口调试助手上打印如下信息。

(5)至此我们完成了ZYNQ串口打印输出项目的全部工作内容。

4. 工程源码下载

本文使用的工程可以通过在公众号输入 ZYNQ_UART 来获取工程下载链接,工程使用的vivado版本为2021.1。