作者:张海军,文章来源: 傅里叶的猫微信公众号

前言:本文章为FPGA问答系列,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面有价值的问题,并汇总成文章,如果问题多的话就每周整理一期,如果问题少就每两周整理一期,一方面是希望能帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。

Q:clock skew会影响时序违例吗?

A:这个问题可以参考高老亚军师公众号(FPGA技术驿站)中的一篇文章。在文中提到:

对于发送时钟和接收时钟是同一时钟的单周期路径,时钟抖动对建立时间有负面影响,但对保持时间没有影响。这一点,在Vivado的时序报告中也可以看到。如下图所示,图中左侧为建立时间时序报告,可以看到Clock Uncertainty,而右侧为保持时间时序报告,是没有Clock Uncertainty。

但如果发送和接收是不同的时钟,而且这两个不是异步时钟,那我们可采用多周期路径进行约束,这个时候,skew对建立和保持时间都是有影响的,也可以从时序报告中看出:

上面这个两个图都是高老师文章中的图,有兴趣的可以去看高老师的原文。

Q:定义一个parameter不指明位宽,工具在implemention时应该是会自动转换成最小位宽么?

A:如果parameter没定义位宽,vivado应该会默认为integer类型,parameter的参数应该不会在implemention看到,在综合之前就会把这些参数吃掉了。

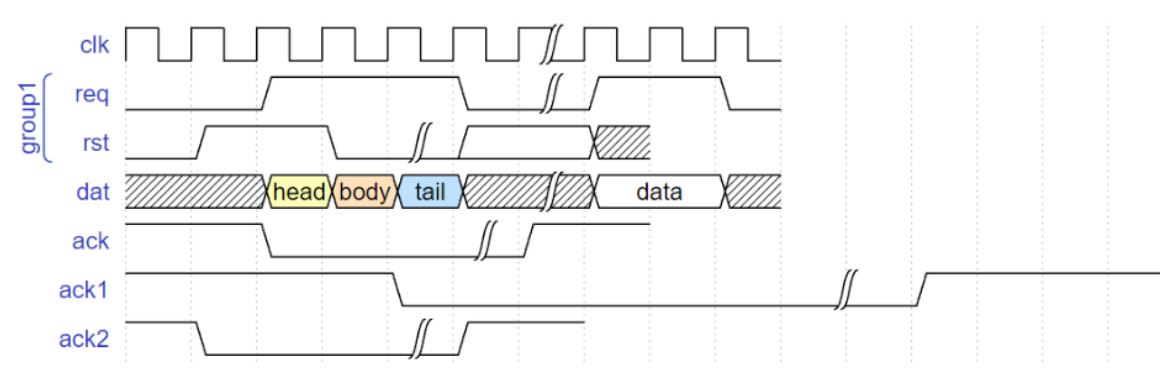

Q:有什么好用的时序绘图工具?

A:WaveDrom是一个免费开源的在线数字时序图渲染引擎。它可以使用JavaScript, HTML5和SVG来将时序图的WaveJSON描述转成SVG矢量图形,从而进行显示。WaveDrom可以嵌入到任何网页中。

下图是WaveDrom画出来的时序图:

Q:fpga + dac输出波形,为何锯齿波的时候,频率稍微高一点,幅度下降,正弦波却不会下降?

A:这跟锯齿波的频谱有很大关系,如果我们画一下锯齿波的频谱,会发现它的频谱是很宽的,不像正弦波是单一的频点,所以当锯齿波信号带宽超过DAC的带宽时,输出的信号就会被削弱。