版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/syrg520/article/details/108272368

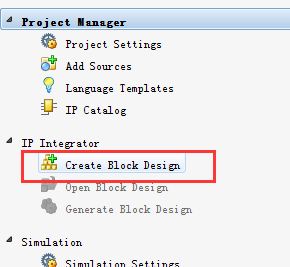

1.选择创建Block Design并命名

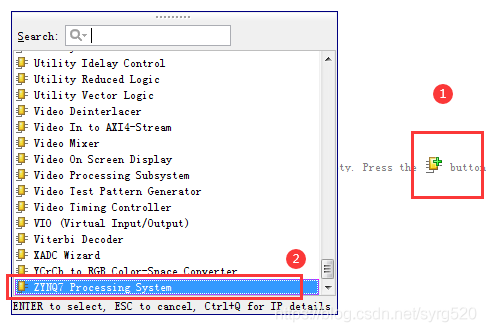

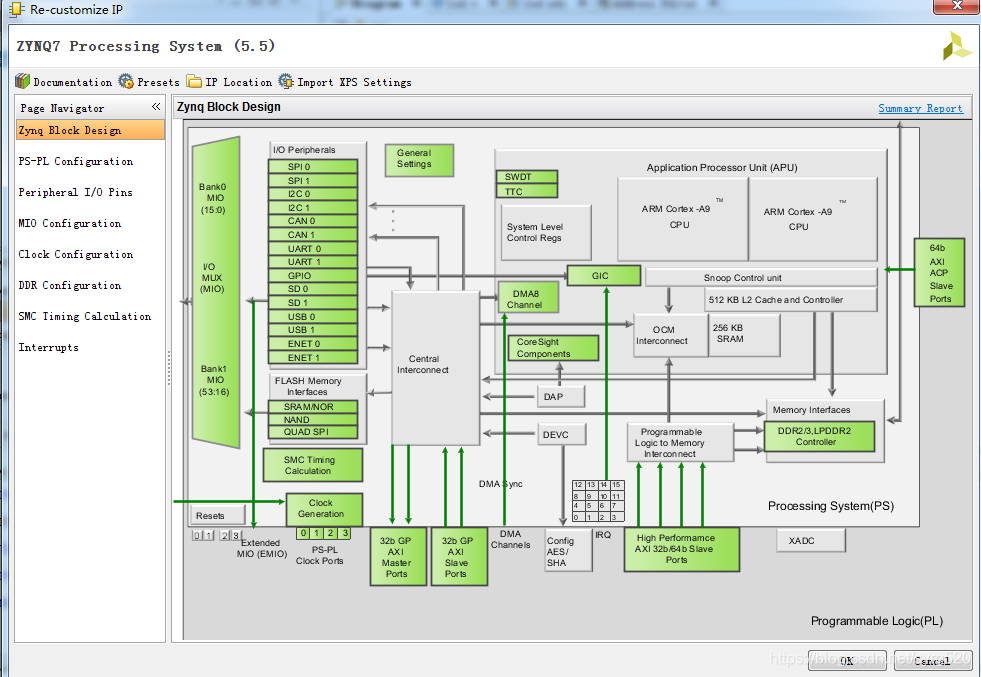

2.点击Add IP,并选择ZYNQ7

3.双击 ZYNQ Processing System,打开 ZYNQ 系统的配置界面

1)PS_PL 页面提供了 PS 到 PL 的相关接口配置信息以及 PS 部分一些配置信息;

2)Peripheral I/O Pins 页面主要是对一些通用外设接口的配置;

3)MIO Configruation 页面主要是对 MIO 已经EMIO 的分配控制;

4)Clock Configruation 页面主要是对 PS 端时钟资源的配置和管理;

5)DDR Configration 页面主要是对 DDR控制器一些参数的配置;

6)Interrupts 页面主要是对中断进行配置管理

4.点击 PS-PL Configuration ,在 Gemeral 目录下,选择UART1 波特率是115200,并取消不用的AXI GP0接口

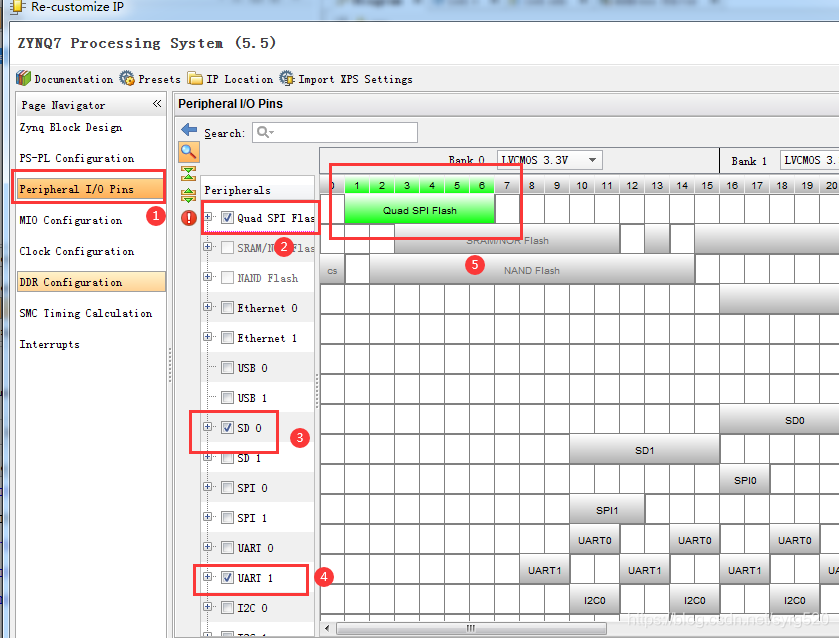

5.点击 Peripheral I/O Pins ,会出现以下的 IO 配置界面。(这里为了将程序下载到SD或Quad SPI Flash,并通过串口显示bootloader信息,故选择SD、 Quad SPI Flash、UART。)

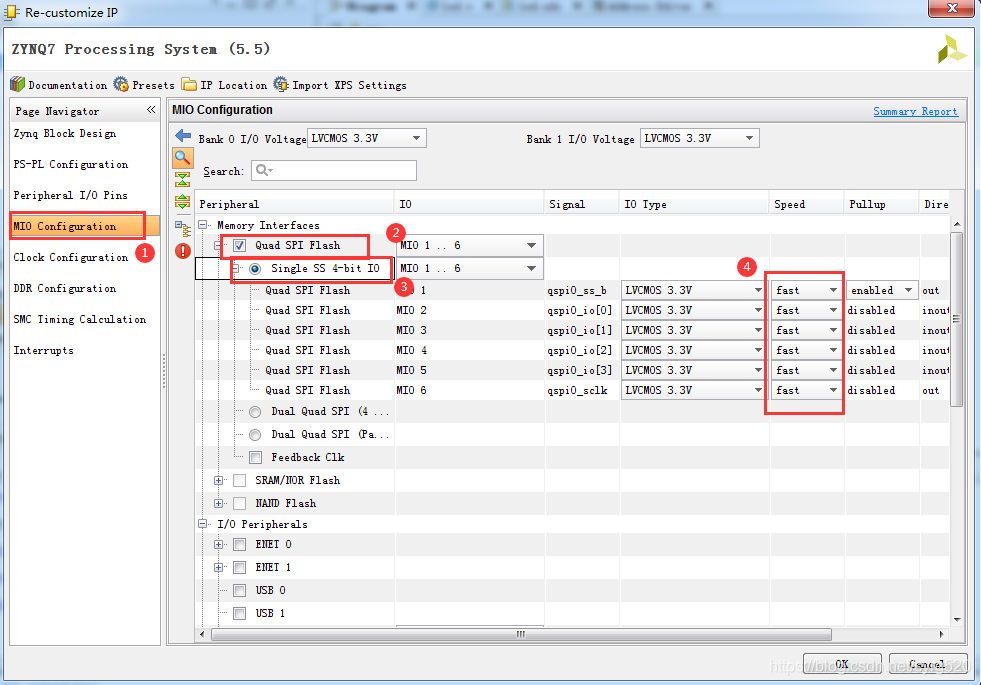

6.在 MIO Configuration 项,Bank1电压选择1.8V,把 Quad SPI Flash 的 MIO1~MIO6 Speed 配置成 fast 模式,在SD0引脚MIO40~MIO45 Speed 也配置成 fast 模式,CD选择MIO47

7.点击 Clock Configuration ,选择 ZYNQ 系统的一些时钟,CPU工作时钟是 666.666666Mhz(767Mhz), DDR 的工作时钟是533.333333Mhz,还有些是外设的工作时钟。QSPI 的时钟频率,默认是 200Mhz,这里不做修改。FCLK_CLK0这里设置为50Mhz,SDIO时钟100Mhz

8. 点击DDR Configration,在这个界面上是选择 DDR 芯片的名称和一些参数。我们再 Memory Part 中需要选择跟开发板上 DDR3 型号一样的名称

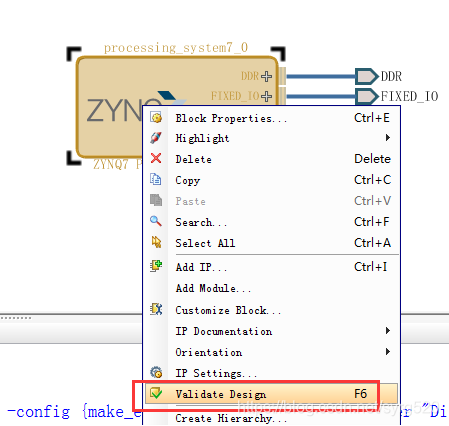

9.完成后点击OK.再在 Diagram 界面里点击"Run Block Automation"完成对 ZYNQ7 Processing System IP核的配置,生成外部 ZYNQ 系统的外部链接 IO 管脚。再右键点击Validate Design,进行验证设计

10.在 Source 窗口中选中 sys.bd,右键并先后选择Generate Output Projects 和 Create HDL Wrapper 进行操作

11.在sys_wrapper中例化led模块,并添加约束文件。再综合、实现、生成bit文件

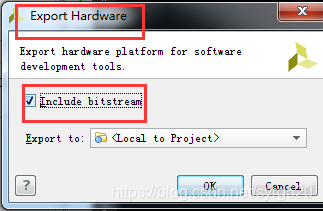

12.将硬件信息导出,File->Export->Export HardWare,同时添加bitstram文件

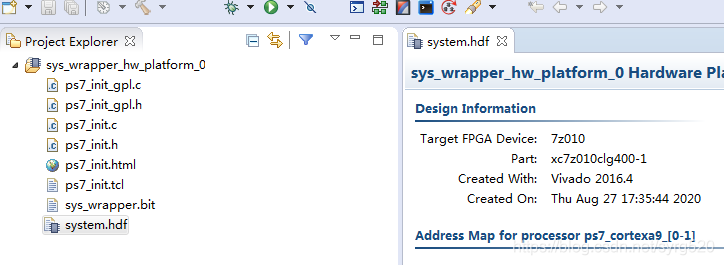

13.启动SDK,File->Launch SDK,生成sys_wrapper_hw_platform_0