本文转载自:无界逻辑(微信号:wujieluoji)微信公众号

一般在实际应用的电路设计中,出现同一个时钟驱动整个电路模块的概率是非常小的。根据自定向下的设计方法,大部分情况下,工程中会出现多个时钟域的模块。如内存控制器工作在200MHz,以太网MAC工作在156.25MHz,IIC Master工作在100MHz,Cache工作在50MHz等等情况。这时候就会涉及到信号跨时钟域的问题,如果不处理,就会出现亚稳态现象,整个电路的功能就不再可靠。

跨时钟(CDC:Clock Domain Change)可分为多种情况,如:单bit跨时钟域(一般控制信号),多bit跨时钟域(一般总线数据信号)。跨时钟域还需要考虑一种情况,如:从低时钟跨到高时钟域,从高时钟域跨低时钟域。

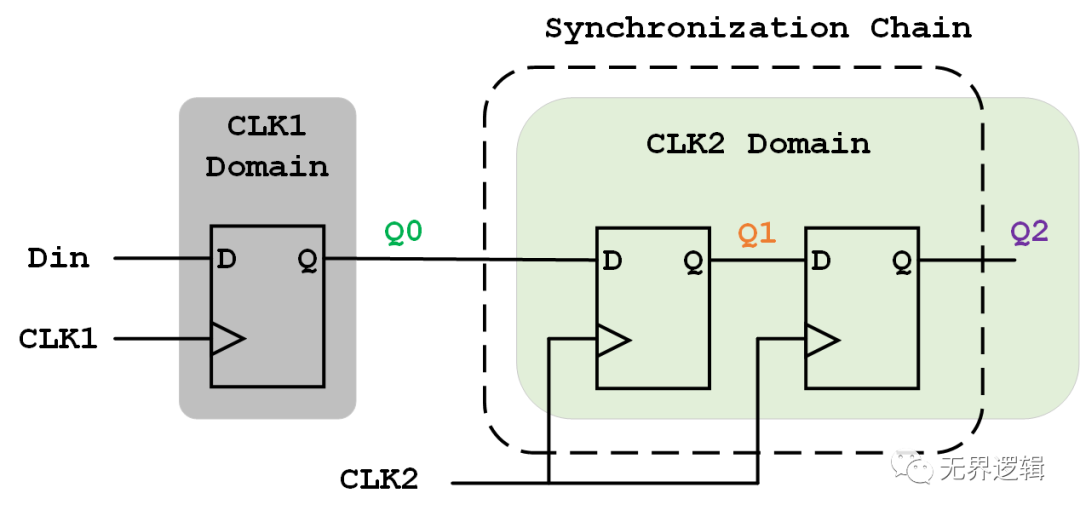

本文重点讲解单bit跨时钟域的处理方法。单bit跨时钟域处理,采用两级同步的方法,如下图所示。

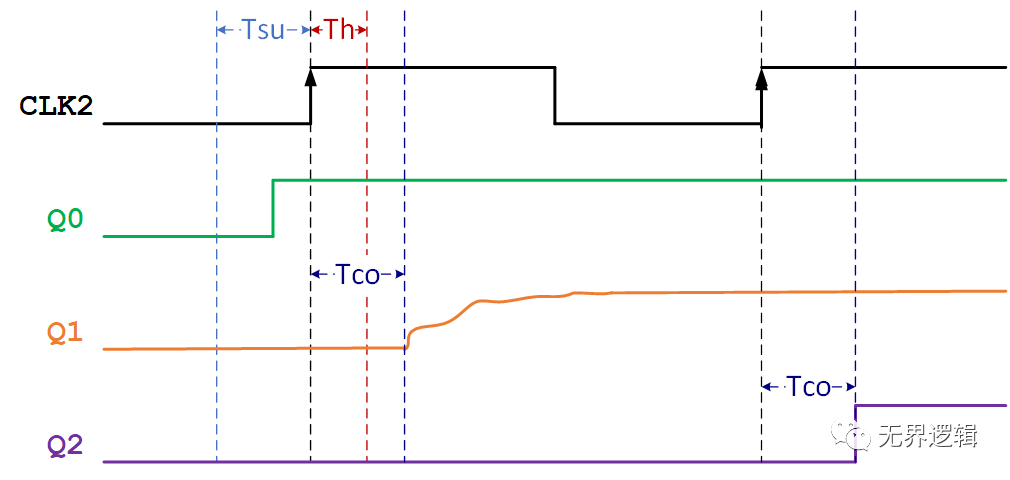

如下图,可以看到Q1在第一次的采样时,发生了亚稳态现象,而此时,Q2采样的Q1稳定的信号。在第二次采样时,Q1的亚稳态经过一个Clock2的时钟周期后,已经脱离亚稳态,信号已经稳定。此时,Q2可以正常采到Q1有效的高电平信号。参考文章:FPGA设计拦路虎之亚稳态度决定一切(面试必问)

参考文章:FPGA的建立时间和保持时间(面试必问)

需要注意的是:

1.Clock1时钟域的信号Q0需要保证宽度,确保可被CLK2能够采到,可以通过展宽的方法处理。

2.上图画的比较理想的情况,两级并不能绝对消除亚稳态危害,只是把亚稳态概率降低到可接受的程度。问题,使用三级打拍是不是更好呢?根据业界的说法,改善程度不大。

两级采样代码:

always @(posedge clk2 or negedge rst_n) begin

if (rst_n == 1'b0) begin

q1 <= 1'b0 ;

q2 <= 1'b0 ;

end

else begin

q1 <= q0;

q2 <= q1;

end

end

如要捕获上升沿,则需要再打一拍;利用Q2和Q3组合逻辑产生;参考文章:FPGA如何进行边沿检测

assign up_p1 = q2 & !q3;

always @(posedge clk2 or negedge rst_n) begin

if (rst_n == 1'b0) begin

q3 <= 1'b0 ;

end

else begin

q3 <= q2;

end

end

是不是很简单?如有疑问,请联系作者。