本文转载自: 无界逻辑(微信号:wujieluoji)微信公众号

多bit信号跨时钟域如何处理呢?为什么不能使用两级打拍的方式呢?很多同学只记住了结论,本文以图示的方式细说一下。

可 先回顾FPGA的单bit信号跨时钟域处理方法(面试比问),可能会出现下面两种情况。

单bit位宽数据两级同步情况

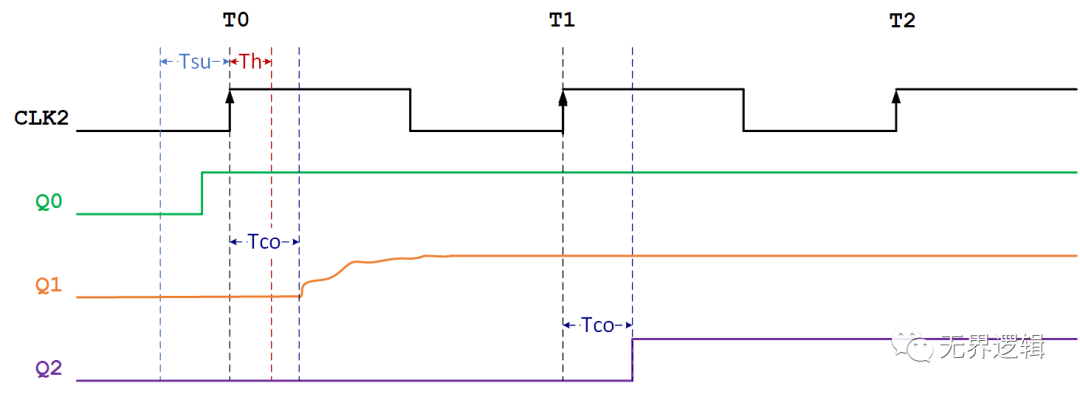

情况一:下图是在T0时刻发生了亚稳态,T1时刻Q1的输出已经稳定在高电平,且满足Tsu和Th,因此T1时刻,Q2就成功的锁存了高电平。

情况二:下图是在T0时刻发生了亚稳态,T1时刻Q1的输出已经稳定在低电平,且满足Tsu和Th,因此T1时刻,Q1重新成功的锁存了Q0的高电平,Q2成功的锁存了Q1的低电平。T2时刻,Q2成功的锁存了Q1的高电平。

可知Q2最终都会锁存到Q0的高电平。要么在T1时刻,要么在T2时刻。换句话说,Q2要么锁存旧数据,要么锁存到新数据。

两bit位宽数据两级同步情况

加入针对2bit数据的跨时钟域处理,也是采用两级打拍同步,又会出现什么情况呢。我们举例说明:原始数据为Q00和Q01,分别进行两级同步电路处理,最终输出Q20和Q21。

若T0时刻,Q0从2‘b00,跳变为2’b11,且Q10在亚稳态后,稳定在低电平,而Q11在亚稳态后,稳定在高电平。

最终Q2会在T2时刻,采样到2‘b11的数据。而在T1和T2之间采样到2’b10的数据。

换句话说,Q2不再是要么锁存Q0的旧数据,要么锁存到Q0的新数据,而是有可能出现其它的数据。假如电路中,通过Q2==2'b10产生脉冲来控制其它的逻辑,这里就会出现功能上的错误。

同理,更多bit的数据跨时钟域采用两级同步处理,情况类似。

总结

很多博客只是描述了一下结论:多bit数据跨时钟域无法使用两级寄存处理。对于背后的根因,本文进行了解析。”字不如图,图不如表“,希望本文对你有所帮助。