本文转载自: FPGA的现今未微信公众号

RGMII是Reduced Gigabit Media Independent Interface的缩写,是精简的GMII接口,虽然它的性能只有1Gbps,但是在通信领域却有着广泛应用的接口。这种接口FPGA供应商通常都会提供IP core,这里主要是对相关的设计(和厂商IP core可能会不一样,基本功能相同)做一个回忆和总结,为定制化提供一些思路。

在系统中的位置

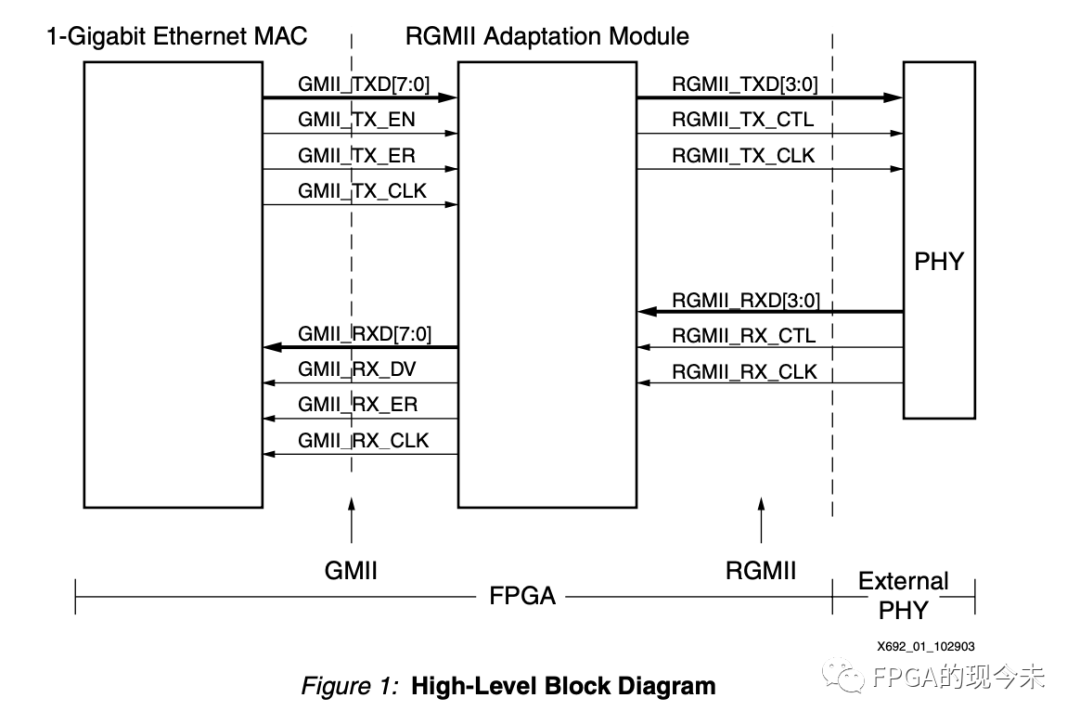

我们知道以太网的通信离不开PHY芯片,那PHY和RGMII接口到底是什么关系呢?如下图所示,PHY芯片实现实现了RGMII接口到网口(RJ45)的转换,PHY的其他功能这里不介绍,读者可以上网查找相关介绍。RGMII接口就是PHY芯片和FPGA之间的接口。

那在FPGA内部如何实现与PHY芯片的通信呢?借用Xilinx的一张图,如下图所示:

在FPGA内部,有2个功能模块,一个是RGMII Adaptation Module,一个是MAC。前者主要完成了GMII接口和RGMII接口之间的转换,后者主要完成1G MAC的功能。本篇文章主要介绍RGMII Adaptation Module,即GMII到RGMII的转换。

接口信号和时序

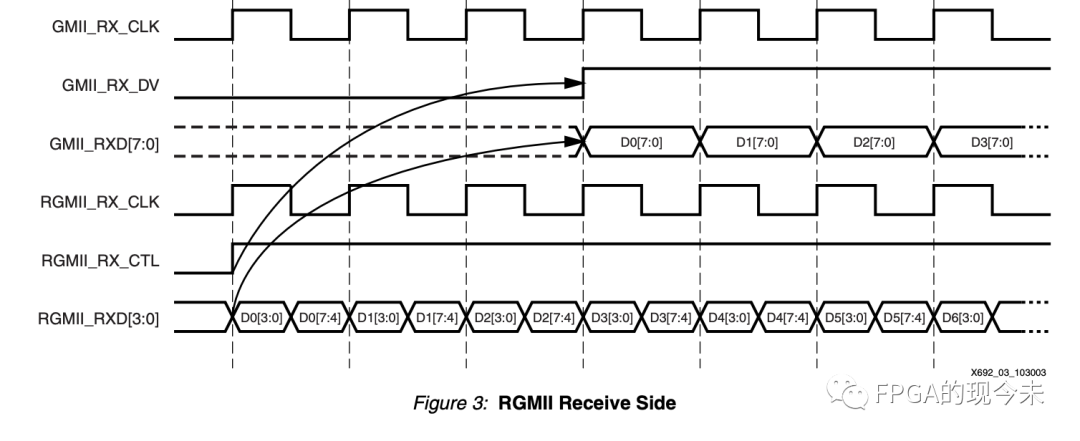

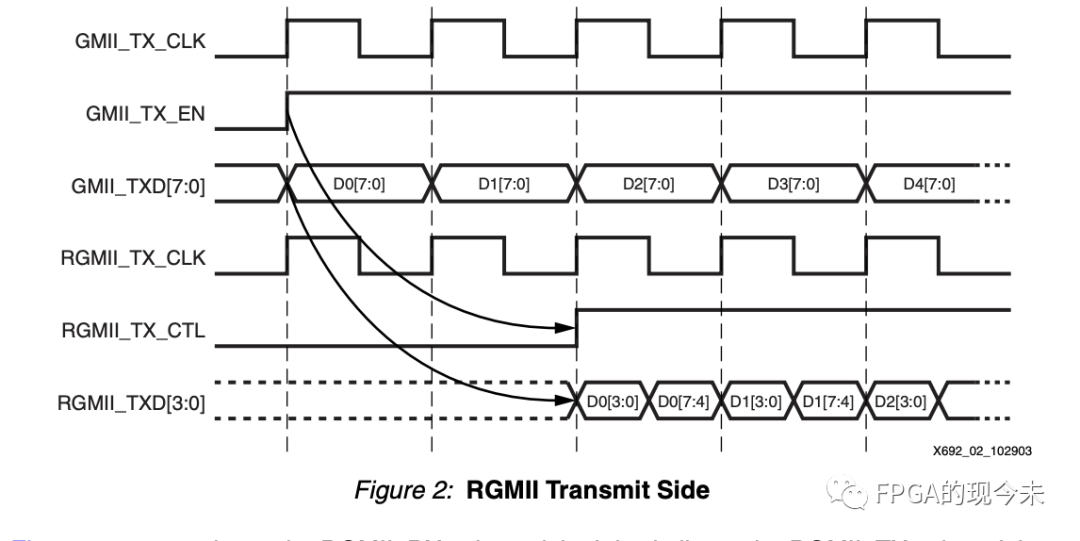

对于RGMII接口,有一个原则,就是谁发送数据,谁就发送时钟,并且是上下沿双沿采用。从GMII到RGMII接口时序是怎么变化的呢?还是借用xilinx的二张图,对于RX方向,就是将双沿数据转成单沿数据;TX方向就是将单沿数据转成双沿数据。

设计方案

那究竟如何设计呢?对于这样接口其实不需要开发者太多的设计技巧,有固定的官方“模版”,在vivado中,通过IP catalog找到“Tri Mode Ethernet MAC”这个IP,选择RGMII接口后,在生成的文件中,有一个文件tri_mode_ethernet_mac_0_rgmii_v2_0_if.v实现了上述接口的转换,这里对官方的代码做一个简单的分析,了解实现的方案,如下图所示:

对于rx方向,输入的数据和有效信号,经过IBUF后,进入IDELAYE2中,这里可以实现相位的调整,然后通过IDDR实现双沿转单沿。接收的随路时钟通过IBUF和BUFR后送给后继模块采样。对于tx方向如下图所示,待发送的数据通过ODDR实现单沿转双沿后,再通过OBUF发送出去。这里需要注意的是,待发送的随路时钟,和ODDR的工作时钟有90°的相位差,这样的目的是方便对端数据的采样,当然可以更具实际情况,在发送端调整时钟相位,或者只有一个时钟,即用ODDR的工作时钟直接作为随路时钟。

通过上面的分析,核心的功能就是2个,第一个是用IDDR和ODDR实现双沿和单沿的转换,第二个就是利用IDELAYE2实现相位的调整。

另外除了上述的IP外,还有gmii to rgmii这个IP同样实现了上述功能。

总结

这里主要思考一个问题,这个模块真的需要我们自己来写吗?不可以用厂家提供的IP吗?当然可以,而且一般也建议采用厂家提供的IP,这就好比设计中常用的FIFO,我们一般使用厂家提供的FIFO IP,但是不代表我们就可以不用了解FIFO的实现原理。同理,了解RGMII和GMII之间转换的设计方案后,对于我们后续的调试也会有大大的帮助。