本文转载自: FPGA入门到精通微信公众号

IP核是一个组件化的设计单元,用于减少系统设计中的重复工作,提高开发效率。本文将介绍Vivado中XCI与XCIX文件以及如何使用Core Container打包IP核,希望能够帮助大家更好地理解和使用IP核。

一、XCI和XCIX格式文件

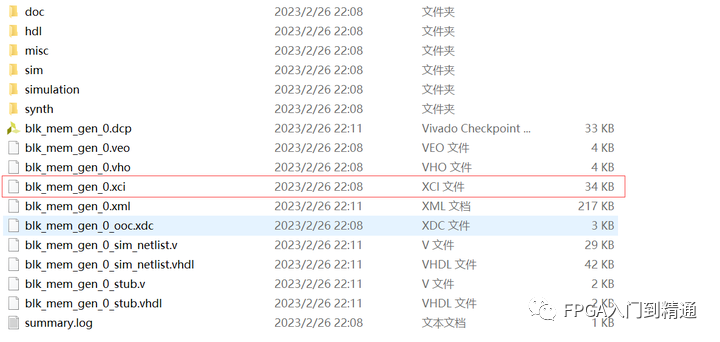

在Vivado中生成 IP核时,一般默认是对应的IP核文件夹会生成在工程目录的.srcs/sources_1/ip路径下。这个文件夹包含了所有与该IP核相关的文件,最主要的是XCI文件,其中包含了用户配置的相关信息。

Vivado还提供了Core Container特性,可以将所有与IP相关的文件压缩到一个以XCIX为扩展名的二进制文件中。同样XCIX文件也可以以源文件的形式添加到工程中。

XCI文件和XCIX文件在Vivado中的表现形式完全相同,在vivado中都可以看到与IP核相关的所有单独文件。

那么为什么要用Core Container打包IP核呢?最大的优势在于简化版本控制管理。对于版本控制系统来说,需要管理的文件越少越方便,Core Container将众多文件打包到一个二进制文件中,正是为了满足这方面的需求。这意味着,通过Core Container打包IP核,版本控制会更加简单方便。

二、设置Core Container

绝大多数IP核都支持Core Container特性,有两种设置方法:

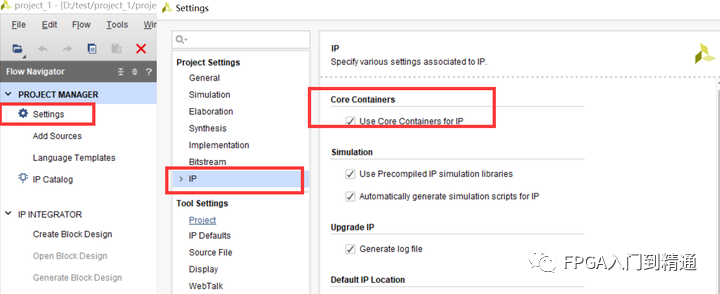

1、打包工程内所有IP

在项目Settings中的IP标签下,选中“Use Core Containers for IP”(默认为不选),这样工程中的所有IP核都会被打包为XCIX格式。

2、打包单个IP

如果只想打包单个IP核,在Sources窗口的IP Sources标签下,在对应IP核的右键菜单中,选择“Enable/Disable Core Container”,来启用或禁用Core Container功能,如下图所示。

三、总结

无论是哪种方式,都需要将其添加到项目中,并在设计中使用IP核。选择适合自己的打包方式可以显著提高开发效率和代码复用性。希望本文能够对FPGA开发者有所帮助。