作者:张海军,来源: 傅里叶的猫

Forwarded Clock是一种时钟信号管理技术,用于在不同部件之间同步数据和控制信号。Forwarded Clock的目的是减少时钟偏斜(clock skew)和提高系统的整体性能和可靠性。这种方法特别关注于如何有效地将时钟信号从一个系统部分传递到另一个部分,以确保整个系统同步运行。

Forwarded Clock翻译成中文就是转发时钟,由于系统同步可能会带来较大的时钟skew,就采用源同步的方案,此时就是需要将这个时钟再转发出去。

在AMD FPGA的官网上,有这样的解释:

A forwarded clock is term that is usually used with a source synchronous output interface.

In a source synchronous output interface, the FPGA sends clock and data to an external device (eg. a digital-to-analog converter (DAC)).

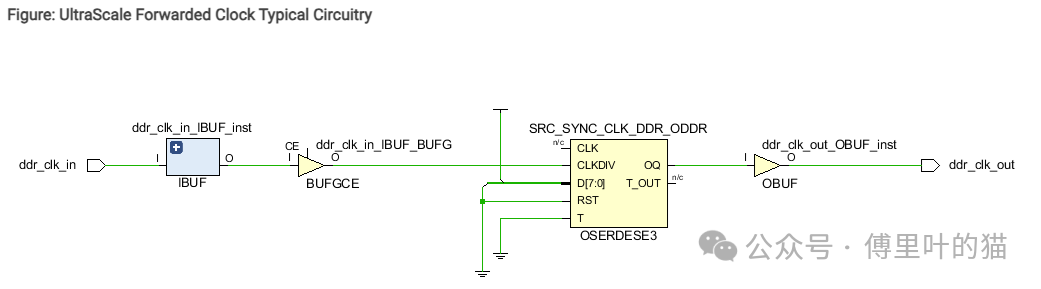

As you correctly mentioned, the ODDR is often used to send the forwarded clock out of the FPGA – as shown in the schematic below.

从图中很明显可以看出,Forwarded Clock其实也是一种Generated Clock,约束如下:

create_generated_clock -name FCLK1 -source [get_pins ODDR1/C] -divide_by 1 [get_ports SSO1_CLK]

当然,也可以采用下面的方式:

为什么要使用ODDR来驱动,而不是直接将时钟输出呢?

Output DDR can forward a copy of the clock to the output. This is useful for propagating

a clock and DDR data with identical delays, and for multiple clock generation, where every

clock load has a unique clock driver. This is accomplished by tying the D1 input of the

ODDR primitive High, and the D2 input Low. Xilinx recommends using this scheme to

forward clocks from the FPGA logic to the output pins.