本文转载自:十年老鸟的CSDN博客

前言

有时候我们想生成一个网表文件,但vivado默认是会生成一个dcp的文件,加密性时非常好的,但又过于黑盒子了,而通过原理图按钮只能看到原理图图形,如果将原理图生成全部是原语的文本呢

使用write_verilog命令

在tcl输入框中使用write_verilog命令

输出网表使用以下指令 :

write_verilog -help 查看write_verilog如何使用

write_verilog E:/test5.v 这样就是输出当前设计的网表了

write_verilog

Description:

Export the current netlist in Verilog format

Syntax:

write_verilog [-cell

[-write_all_overrides] [-keep_vcc_gnd] [-rename_top

[-sdf_anno

[-include_xilinx_libs] [-logic_function_stripped] [-quiet]

[-verbose]

Returns:

the name of the output file or directory

Usage:

Name Description

---------------------------------------

[-cell] Root of the design to write, e.g.

des.subblk.cpu

Default: whole design

[-mode] Values: design, pin_planning, synth_stub, sta,

funcsim, timesim

Default: design

[-lib] Write each library into a separate file

[-port_diff_buffers] Output differential buffers when writing in

-port mode

[-write_all_overrides] Write parameter overrides on Xilinx primitives

even if the override value is the same as the

default value

[-keep_vcc_gnd] Don't replace VCC/GND instances by literal

constants on load terminals. For simulation

modes only.

[-rename_top] Replace top module name with custom name e.g.

netlist

Default: new top module name

[-sdf_anno] Specify if sdf_annotate system task statement

is generated

[-sdf_file] Full path to sdf file location

Default:

[-force] Overwrite existing file

[-include_xilinx_libs] Include simulation models directly in netlist

instead of linking to library

[-logic_function_stripped] Convert INIT strings on LUTs & RAMBs to fixed

values. Resulting netlist will not behave

correctly.

[-quiet] Ignore command errors

[-verbose] Suspend message limits during command execution

Categories:

FileIO, Simulation

Description:

Write a Verilog netlist of the current design or from a specific cell of

the design to the specified file or directory. The output is a IEEE

1364-2001 compliant Verilog HDL file that contains netlist information

obtained from the input design files.

You can output a complete netlist of the design or specific cell, or output

a port list for the design, or a Verilog netlist for simulation or static

timing analysis.

Arguments:

-cell

block level of the design hierarchy. The output Verilog file or files will

only include information contained within the specified cell or module.

-mode

default, the Verilog netlist is written for the whole design. Valid mode

values are:

* design - Output a Verilog netlist for the whole design. This acts as a

snapshot of the design, including all post placement, implementation,

and routing information in the netlist.

* pin_planning - Output only the I/O ports for the top-level of the design.

* synth_stub - Output the ports from the top-level of the design for use

as a synthesis stub.

* sta - Output a Verilog netlist to be used for static timing analysis

(STA).

* funcsim - Output a Verilog netlist to be used for functional

simulation. The output netlist is not suitable for synthesis.

* timesim - Output a Verilog netlist to be used for timing simulation.

The output netlist is not suitable for synthesis.

-lib - (Optional) Create a separate Verilog file for each library used by

the design.

Note: The -library option can only be used for simulation. Vivado synthesis

will treat all Verilog files as being in the default work library.

-port_diff_buffers - (Optional) Add the differential pair buffers and

internal wires associated with those buffers into the output ports list.

This argument is only valid when -mode pin_planning or -mode synth_stub is

specified.

-write_all_overrides [ true | false ] - (Optional) Write parameter

overrides, in the design to the Verilog output even if the value of the

parameter is the same as the defined primitive default value. If the option

is false then parameter values which are equivalent to the primitive

defaults are not output to the Verilog file. Setting this option to true

will not change the result but makes the output Verilog more verbose.

-keep_vcc_gnd - (Optional) By default, when writing a nelist for

simulation, or from an IP integrator block design, the Vivado Design Suite

replaces VCC and GND primitives, and the nets they drive, with literal

constants on each of the loads on the net. The -keep_vcc_gnd option

disables this default behavior and preserves the VCC or GND primitives.

-rename_top

specified. This option only works with -mode funcsim or -mode timesim to

allow the Verilog netlist to plug into top-level simulation test benches.

-sdf_anno [ true | false ] - (Optional) Add the $sdf_annotate statement to

the Verilog netlist. Valid values are true (or 1) and false (or 0). This

option only works with -mode timesim, and is set to false by default.

-sdf_file

when writing the $sdf_annotate statement into the output Verilog file. When

not specified, the SDF file is assumed to have the same name and path as

the Verilog output specified by

SDF file must be separately written to the specified file path and name

using the write_sdf command.

-force - (Optional) Overwrite the Verilog files if they already exists.

-include_xilinx_libs - (Optional) Write the simulation models directly in

the output netlist file rather than pointing to the libraries by reference.

-logic_function_stripped - (Optional) Hides the INIT values for LUTs & RAMs

by converting them to fixed values in order to create a netlist for debug

purposes that will not behave properly in simulation or synthesis.

-quiet - (Optional) Execute the command quietly, returning no messages from

the command. The command also returns TCL_OK regardless of any errors

encountered during execution.

Note: Any errors encountered on the command-line, while launching the

command, will be returned. Only errors occurring inside the command will be

trapped.

-verbose - (Optional) Temporarily override any message limits and return

all messages from this command.

Note: Message limits can be defined with the set_msg_config command.

path is optional, but if one is not provided the Verilog file will be

written to the current working directory, or the directory from which the

Vivado tool was launched.

Examples:

The following example writes a Verilog simulation netlist file for the

whole design to the specified file and path:

write_verilog C:/Data/my_verilog.v

In the following example, because the -mode timesim and -sdf_anno options

are specified, the $sdf_annotate statement will be added to the Verilog

netlist. However, since the -sdf_file option is not specified, the SDF file

is assumed to have the same name as the Verilog output file, with an .sdf

file extension:

write_verilog C:/Data/my_verilog.net -mode timesim -sdf_anno true

Note: The SDF filename written to the $sdf_annotate statement will be

my_verilog.sdf.

In the following example, the functional simulation mode is specified, the

option to keep VCC and GND primitives in the output simulation netlist is

enabled, and the output file is specified:

write_verilog -mode funcsim -keep_vcc_gnd out.v

See Also:

* write_sdf

* write_vhdl

为了在网表中不要出现IO BUFFER,在综合属性中,需要设置一下。

其次如果不想被人看到模块层次,则将-flatten_hierarchy设置为full

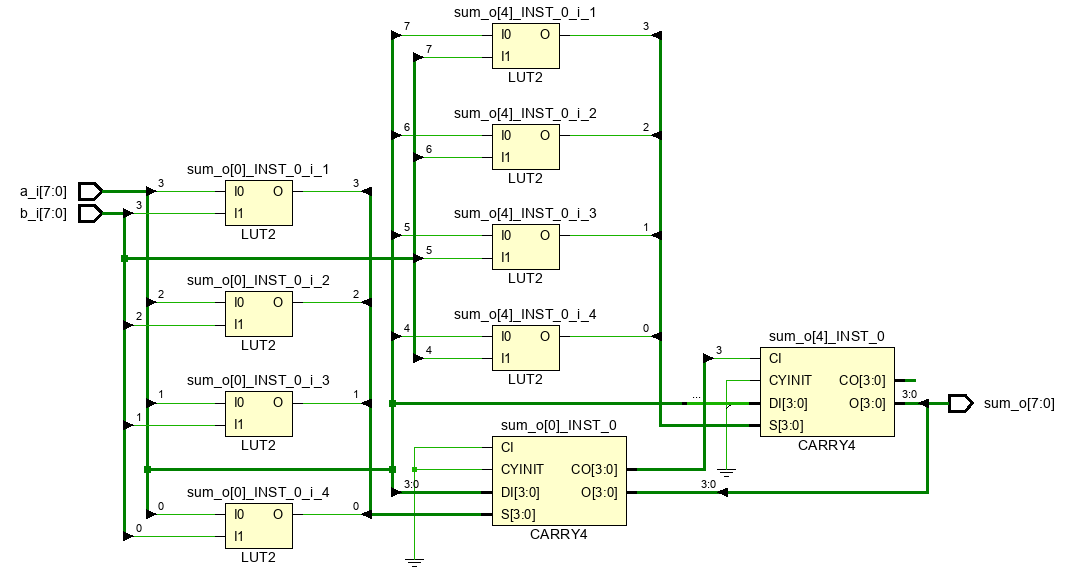

一个加法器

module test(

input [7:0]a_i,

input [7:0]b_i,

output [7:0]sum_o

);

assign sum_o = a_i + b_i;

endmodule

可得到如下网表,与上述加法器代码是等效的

module test5 (

input [7:0]a_i,

input [7:0]b_i,

output [7:0]sum_o

);

wire [7:0]a_xor_b;

wire [3:0]sum_co;

CARRY4 u0_CARRY4 (.CI(1'b0 ),.CO(sum_co[3:0]),.CYINIT(1'b0),.DI(a_i[3:0]),.O(sum_o[3:0]),.S(a_xor_b[3:0]));

CARRY4 u1_CARRY4 (.CI(sum_co[3]),.CO( ),.CYINIT(1'b0),.DI(a_i[7:4]),.O(sum_o[7:4]),.S(a_xor_b[7:4]));

LUT2 #(.INIT(4'h6)) u0_LUT2 (.I0(a_i[0]),.I1(b_i[0]),.O(a_xor_b[0] ));

LUT2 #(.INIT(4'h6)) u1_LUT2 (.I0(a_i[1]),.I1(b_i[1]),.O(a_xor_b[1] ));

LUT2 #(.INIT(4'h6)) u2_LUT2 (.I0(a_i[2]),.I1(b_i[2]),.O(a_xor_b[2] ));

LUT2 #(.INIT(4'h6)) u3_LUT2 (.I0(a_i[3]),.I1(b_i[3]),.O(a_xor_b[3] ));

LUT2 #(.INIT(4'h6)) u4_LUT2 (.I0(a_i[4]),.I1(b_i[4]),.O(a_xor_b[4] ));

LUT2 #(.INIT(4'h6)) u5_LUT2 (.I0(a_i[5]),.I1(b_i[5]),.O(a_xor_b[5] ));

LUT2 #(.INIT(4'h6)) u6_LUT2 (.I0(a_i[6]),.I1(b_i[6]),.O(a_xor_b[6] ));

LUT2 #(.INIT(4'h6)) u7_LUT2 (.I0(a_i[7]),.I1(b_i[7]),.O(a_xor_b[7] ));

endmodule