文章来源:FPGA入门到精通

本文将详细介绍Vivado软件的使用方法,帮助初学者快速掌握AMD FPGA开发。

本文将从Vivado的设计输入进行介绍,包括常用的方法、基本操作以及各种小技巧。

一、使用vivado新建或添加文件

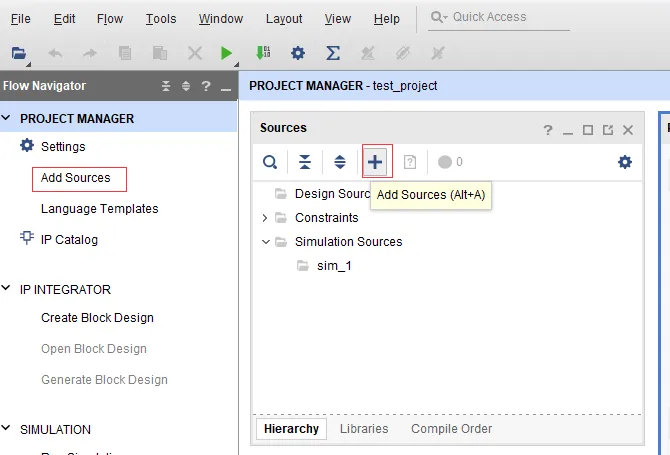

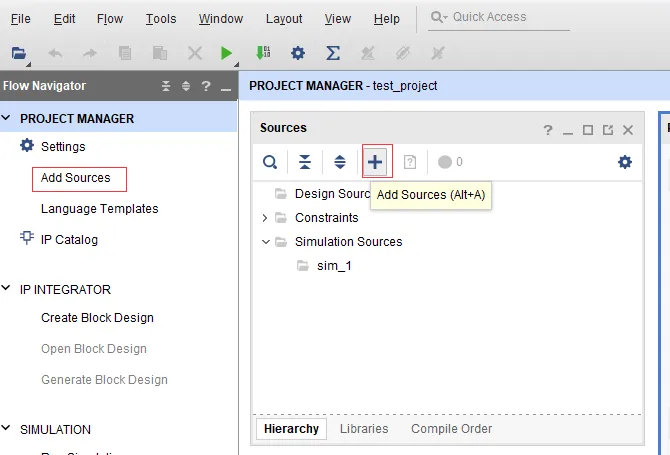

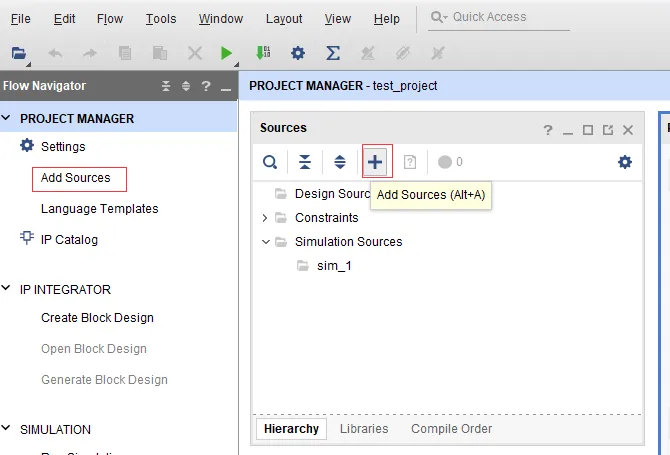

1、打开添加或新建文件界面

点击左侧导航栏【Flow Navigator】下的【Project Manager】->【AddSources】或Sources中的“+”或快捷键“ALT+A”,打开设计输入添加界面。

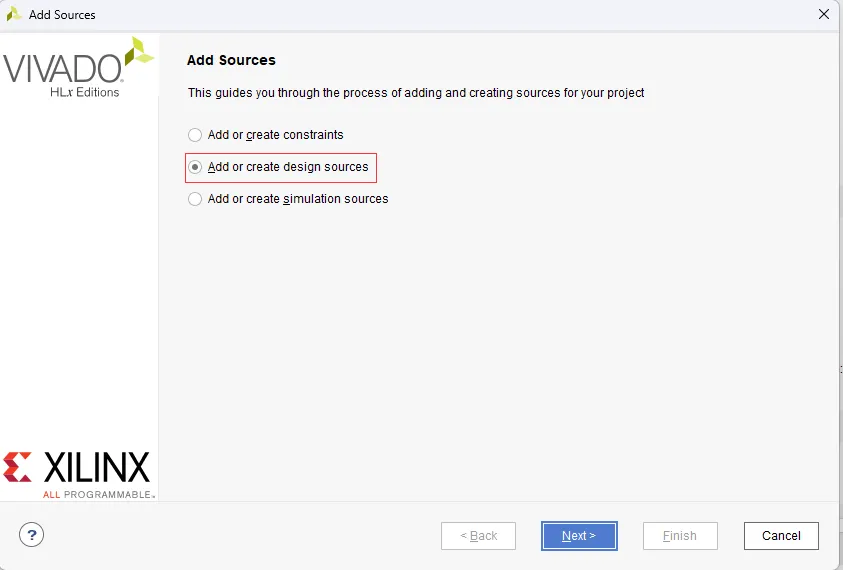

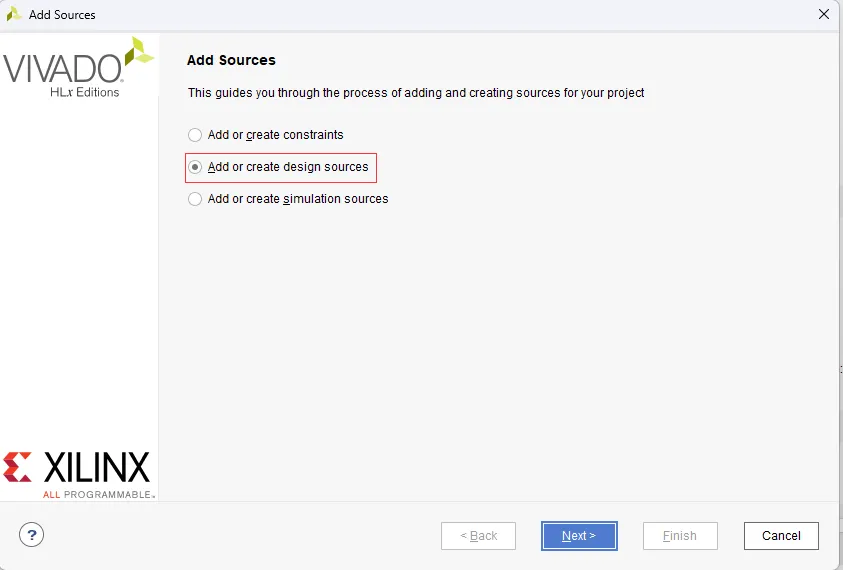

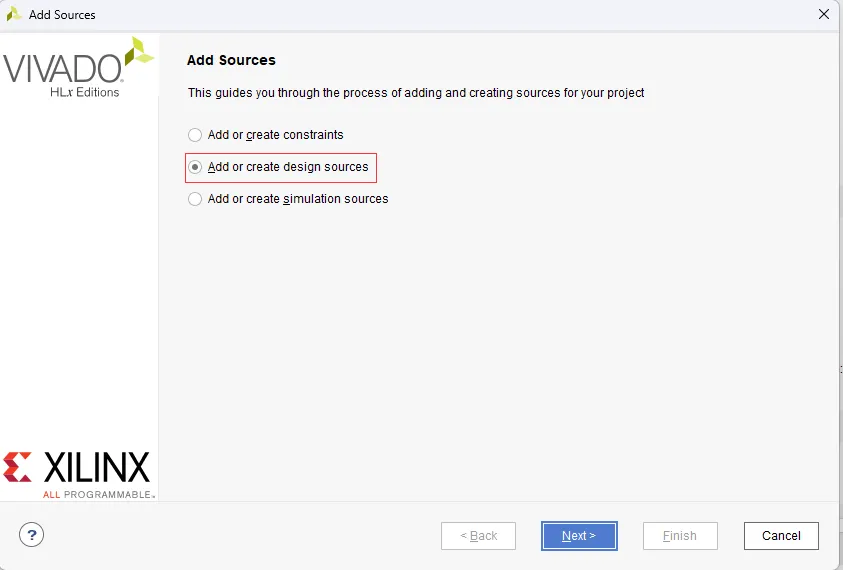

如果是添加RTL源代码文件,则选择“add or create design sources”。如果是添加约束文件,则选择“add or create cconstraints”。如果是添加仿真文件,则选择“add or create simulation sources”。

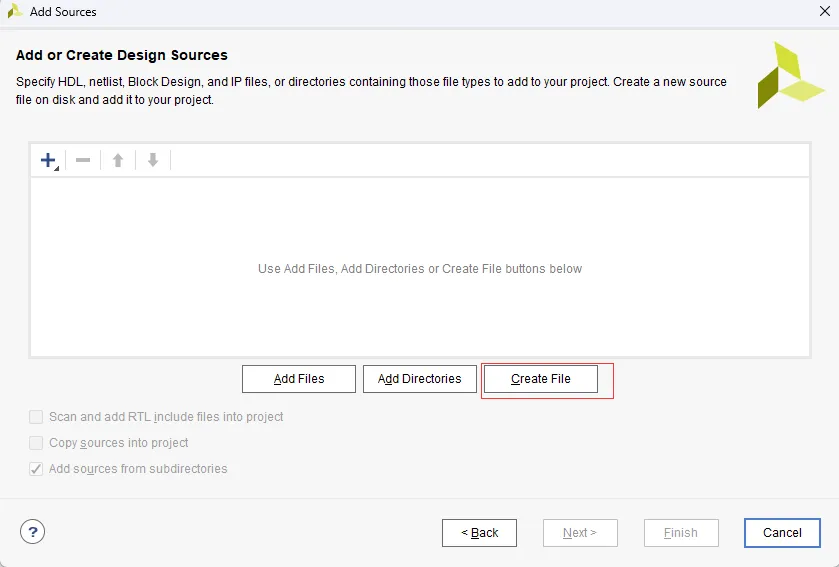

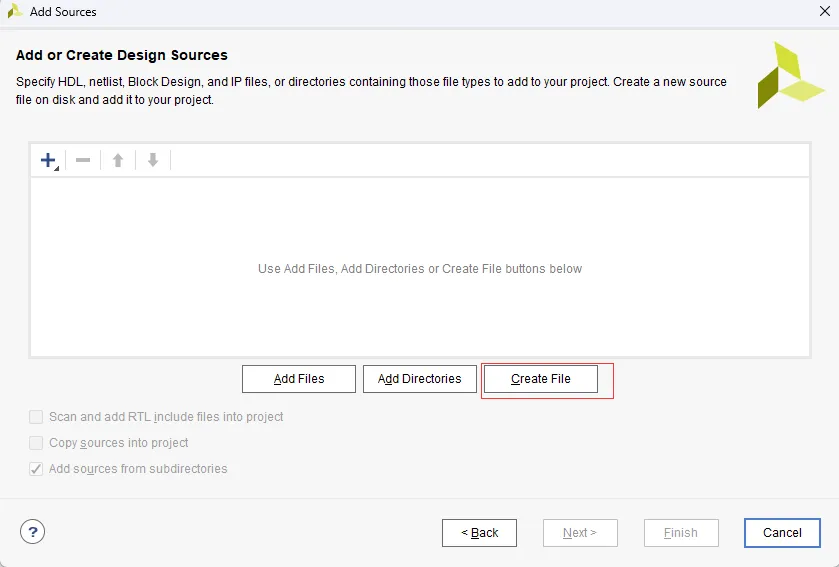

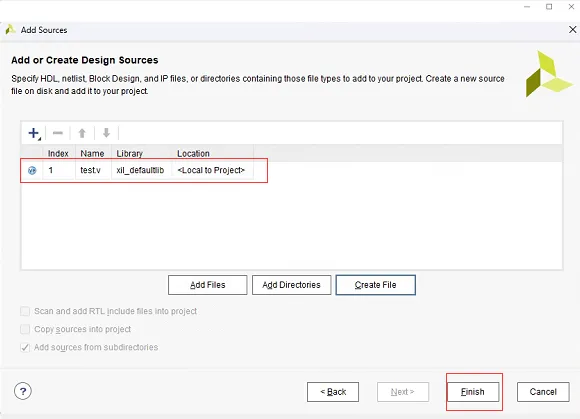

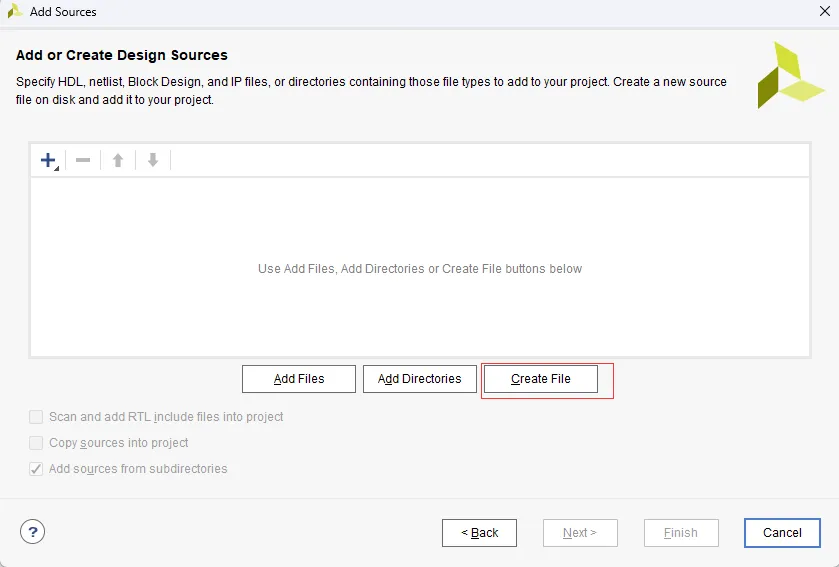

如果需要将整个文件夹添加,则点击【Add Directions】。如果创建新文件,则点击【Create File】。

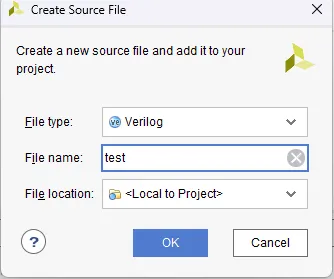

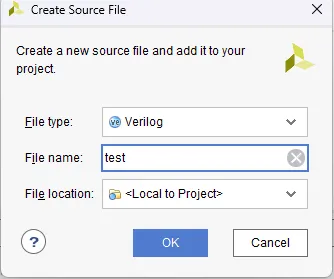

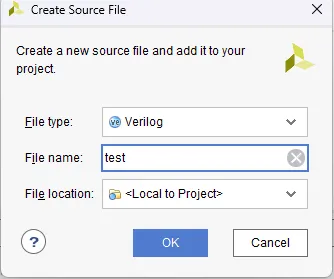

输入源文件名称,这里输入“test”,默认选择“verilog”语言类型,点击OK。

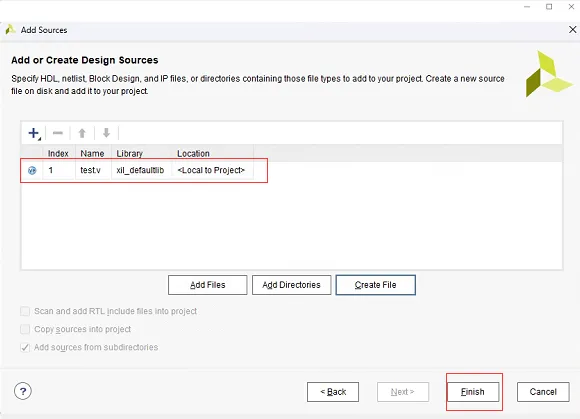

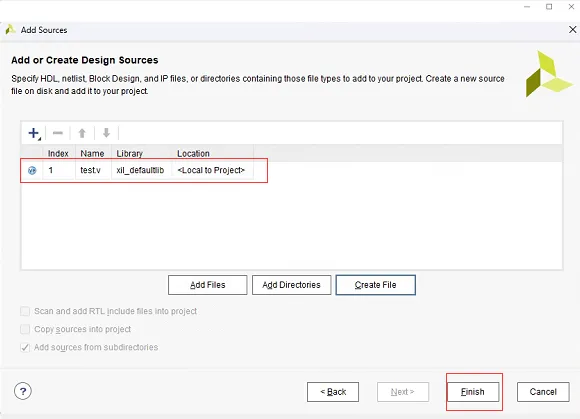

创建的源文件,会出现在文件列表中,点击Finish。

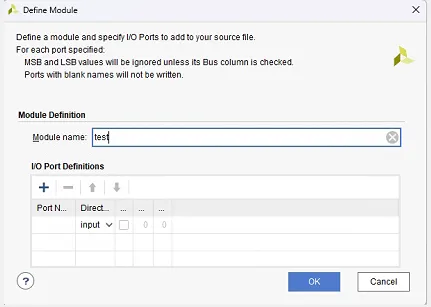

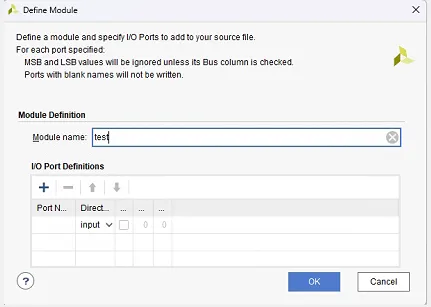

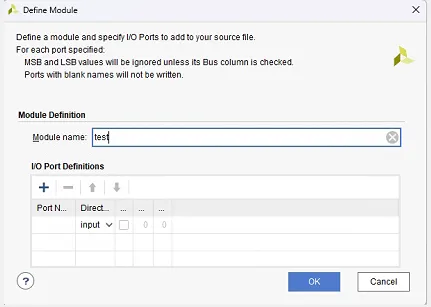

弹出模块定义界面,可以添加输入输出接口,这里我们不添加,后续在代码中手动写,点击OK。

弹出提示,点击OK即可。

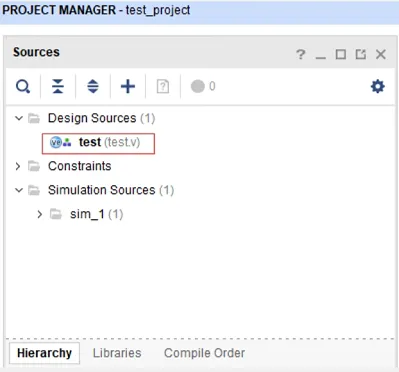

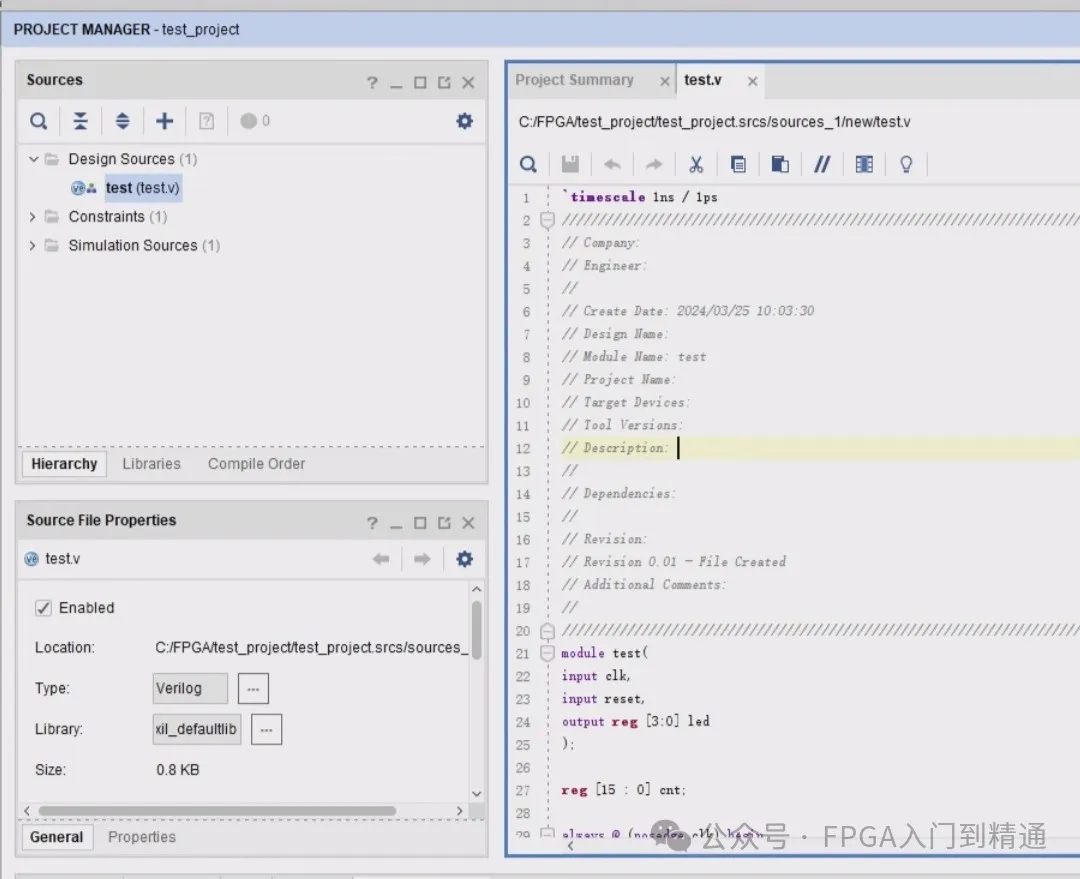

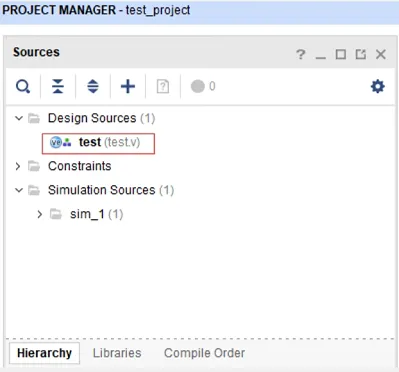

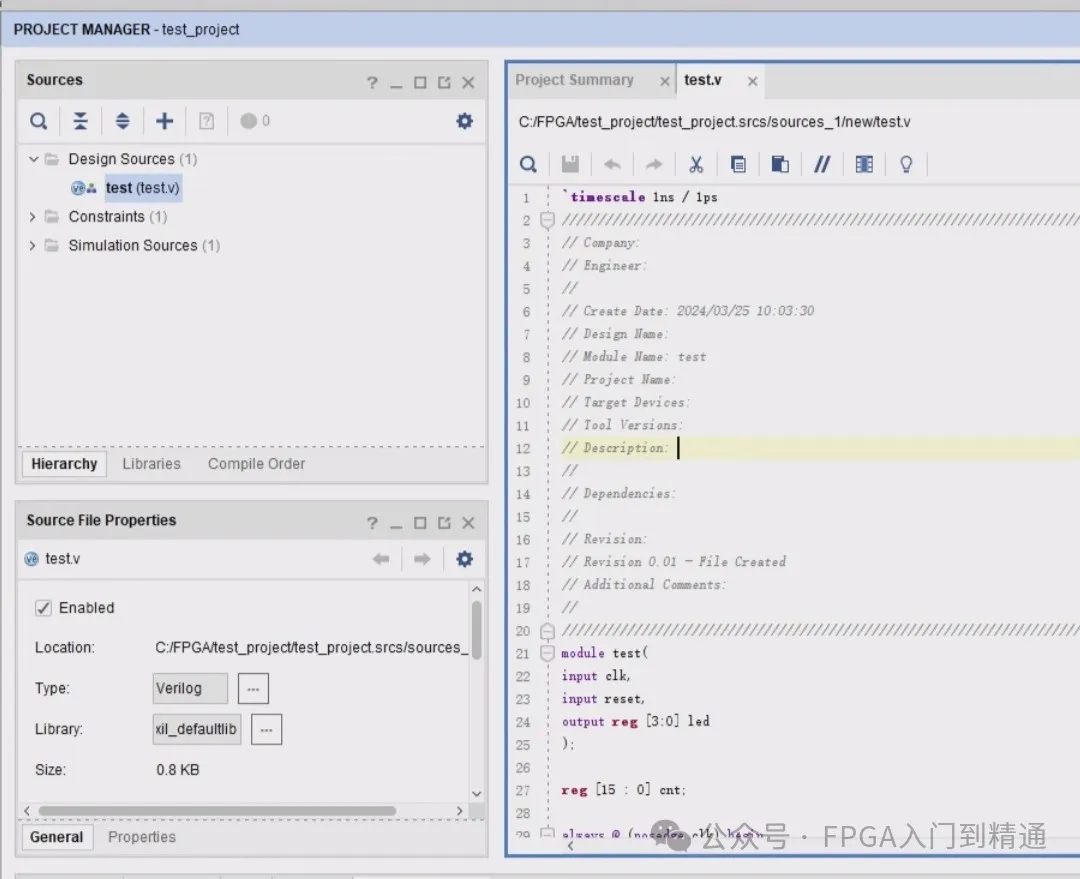

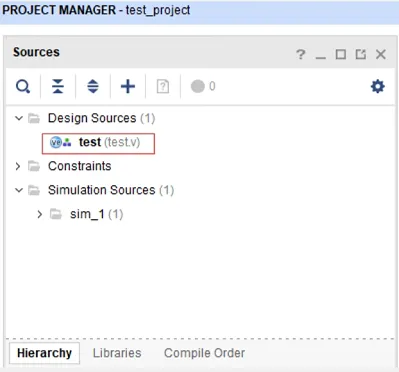

4、完成新建或添加RTL文件

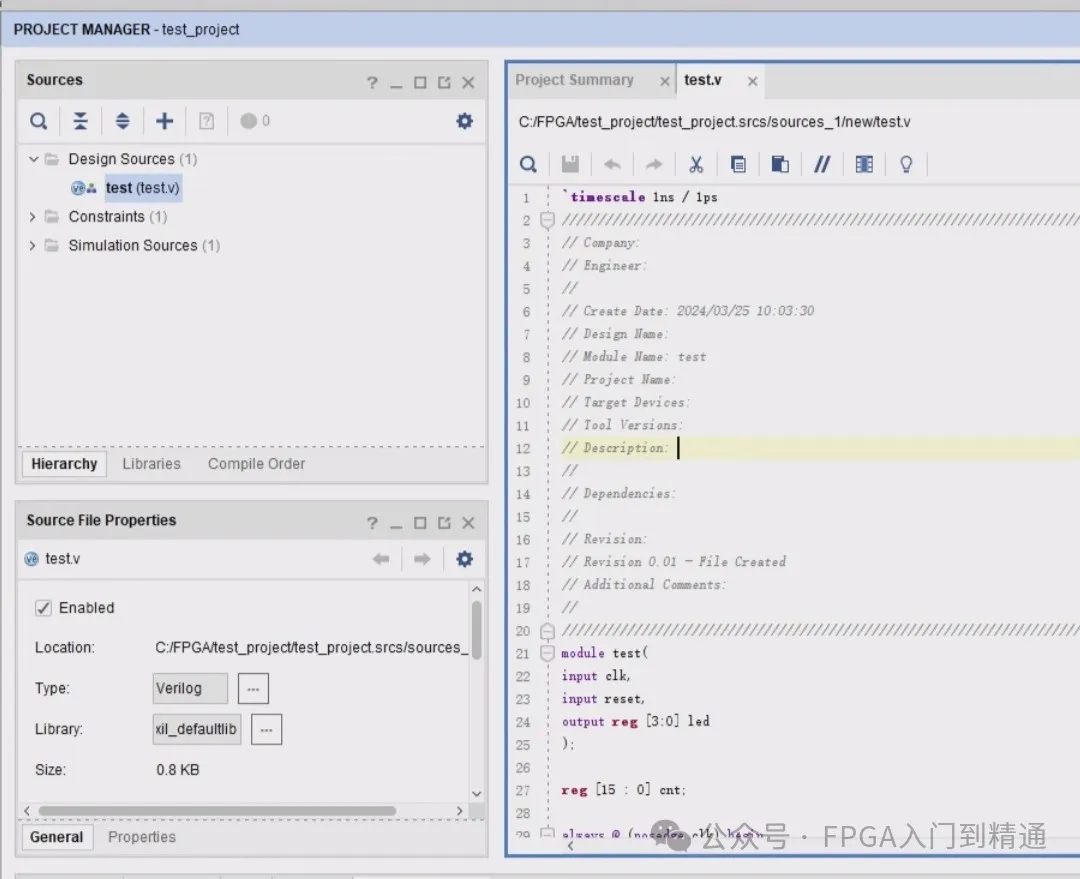

创建的文件会出现在Source窗口的Design Files中。

实际上vivado自带编辑器的使用效果一般,大家都喜欢用第三方编辑器写代码,比如visual studio code、notepad等等,有更多丰富插件,写代码体验也更好。写RTL代码或约束文件时,一般不会创建空白文件,都会把已有的RTL文件复制一份,在这个新的RTL文件基础上编写修改或编写代码。1、vivado中添加文件位置错误,比如源代码文件添加到仿真文件栏中,这时候怎么处理?方法2:鼠标右击该文件,如果文件是在【Design Sources】栏下,将会有【move to Simultion Sources】,单击这个选项可将文件移动到【Simultion Sources】;如果文件是在【Simultion Sources】栏下,将会有【move to Design Sources】,单击这个选项可将文件移动到【Design Sources】;2、如何实现在vivado中,双击文件,自动使用第三方编辑器打开?这需要将vivado设置成关联第三方编辑器,具体步骤可参考这篇文章: