本文转载自:FPGA入门到精通

本系列文章将详细介绍Vivado软件的使用方法,帮助初学者快速掌握AMD FPGA开发。

本文将详细介绍vivado仿真功能,包括如何使用、测试激励文件的撰写,以及如何调用第三方仿真测试软件。

一、仿真概述

仿真是FPGA设计流程中的重要环节,它允许设计者在实际硬件实现之前,对设计进行逻辑功能和时序行为的验证。Vivado软件中的仿真功能主要包括行为仿真(Functional Simulation)和时序仿真(Timing Simulation)。

1、行为仿真

行为仿真,又称为功能仿真,主要关注设计的逻辑功能是否正确。在此阶段,仿真器不考虑硬件的具体实现细节,如门延迟和布线延迟,只关注设计是否按照预期的逻辑行为工作。

2、时序仿真

时序仿真则关注设计在特定硬件实现条件下的时序行为。它考虑了实际硬件中的延迟因素,如门延迟和布线延迟,以验证设计是否满足时序约束。

二、功能仿真需要的文件

进行功能仿真前,需要准备以下文件:

1、设计HDL源代码

设计HDL源代码是仿真的基础,可以是VHDL或Verilog语言编写。这些源代码构成了被测试单元(Unit Under Test, UUT)。

2、测试激励代码(TestBench)

测试激励代码(TestBench)用于生成UUT的输入信号,并验证输出信号。TestBench不需要进行综合,因此具有很高的灵活性。

3、仿真模型/库

根据设计中使用的IP核或第三方模块,可能需要相应的仿真模型或库。Vivado集成了预编译的仿真模型,可以直接使用。

三、具体步骤

1、创建TestBench

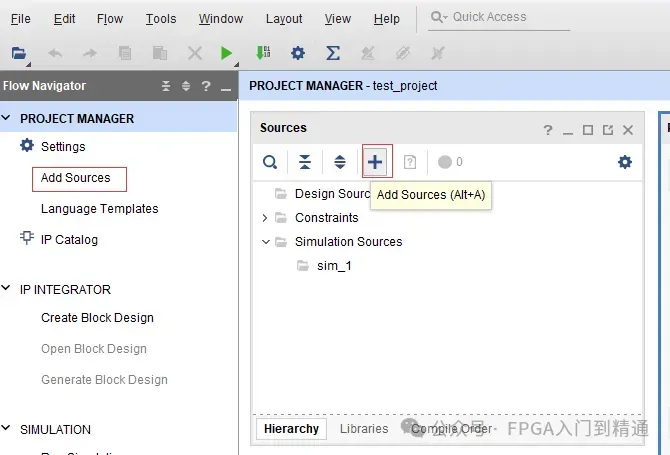

在Vivado IDE中,通过“Sources”窗口中的“+”号添加TestBench。

选择“Add or Create Simulation Sources”,点击next。

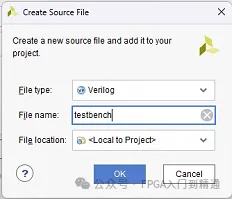

然后点击“Create File”。

输入文件名TestBench,点击OK。

最后点击finish。

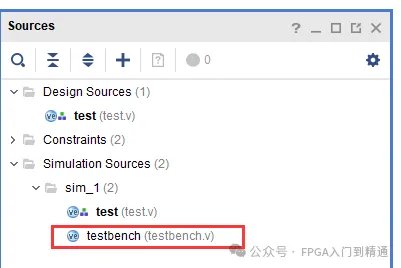

一路点击OK,点击Yes。最后在source窗口下,可看到testbench.v文件。

2、编写TestBench代码

在创建的TestBench文件中,编写测试激励代码。这通常包括初始化输入信号、生成时钟信号、监视输出信号等。

双击打开testbench.v文件,输入测试激励即可。

`timescale 1ns / 1ps // 定义时间单位和时间精度

module testbench;

// 定义测试激励信号reg clk; // 时钟信号reg reset; // 复位信号wire [3:0] led; // LED输出信号

// 实例化待测试的设计模块test uut ( .clk(clk), .reset(reset), .led(led));

initial begin // 初始化时钟和复位信号 clk = 1'b0; reset = 1'b1; // 应用复位 #20 reset = 1'b0; // 等待一段时间,观察LED信号的变化 #10000 $finish;end

// 时钟信号生成always #5 clk = ~clk; // 每隔5ns翻转时钟信号

// 监控输出信号initial begin $monitor("Time = %t, reset = %b, led = %b",$time, reset, led);end

endmodule

// 这里是待测试的设计模块module test( input clk, input reset, output reg [3:0] led); reg [15 : 0] cnt; always @ (posedge clk) begin if (reset) cnt <= 0; else cnt <= cnt + 1; end always @ (posedge clk) begin if (reset) led <= 4'b0001; else if (cnt == 16'hffff) led <= led == 4'b1000 ? 4'b0001 : led << 1; end endmodule

更多有关测试激励编写可以查看:TestBench内容编写与方法总结

3、 运行仿真

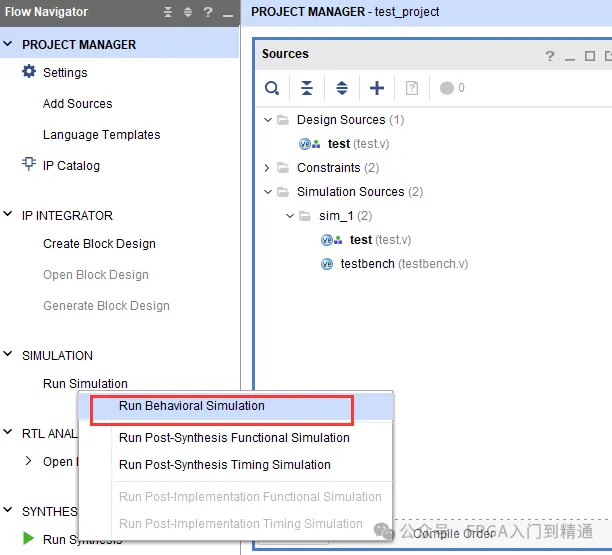

在“Flow Navigator”窗口中点击“Run Simulation”,选择合适的仿真类型(如“Run Behavioral Simulation”)并启动仿真。

常用的一般是行为功能仿真(Run Behavioral Simulation),时序仿真测试不如直接上板调试来的快。

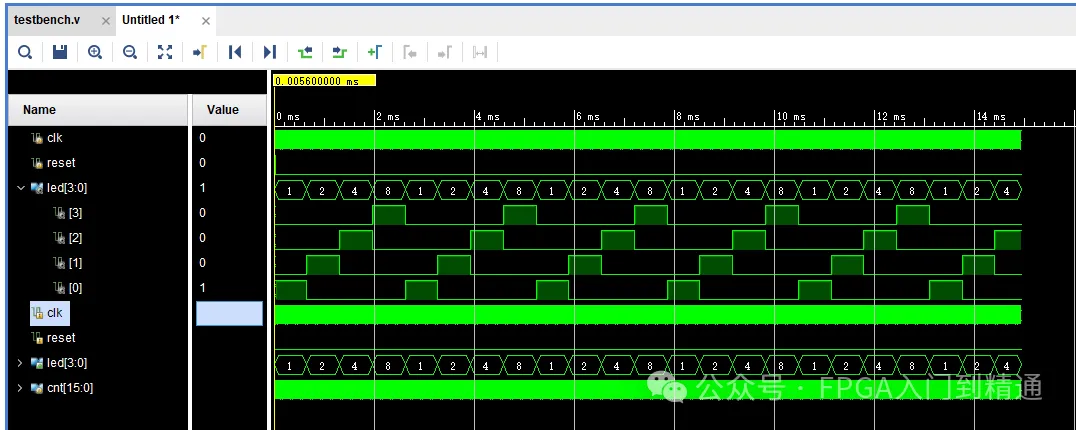

4、查看和分析结果

使用Vivado的Scope、Waveform等窗口查看和分析仿真结果。可以通过添加信号到波形窗口,保存波形配置信息,并进行波形的缩放、测量等操作。

四、高级技巧

1、波形配置信息的保存与加载

在仿真过程中,可以将波形配置信息保存为“.wcfg”文件,以便在后续的仿真中重用。

2、仿真时间的设置

可以在仿真设置中调整仿真的默认时间,以便更好地观察和分析信号的变化。

3、代码修改与重新仿真

在观察到仿真结果与预期不符时,可以对HDL源代码进行修改,并通过“Relaunch”功能重新加载并仿真,以便快速迭代和调试。

4、时钟和复位信号的生成

在TestBench中,通常会生成时钟和复位信号,以便模拟实际硬件的工作条件。

5、仿真精度的调整

根据需要,可以调整仿真的精度,如将仿真单位设置为1ns/1ps,以便更精确地观察信号的变化