作者:FPGA的现今未

最近一个朋友私信我说,看了以前的写的复位设计,在自己的项目中设计了复位同步器用来实现异步复位同步解复位,但是他在检测告警log的时候,遇到了一个非常奇怪的问题,咨询了我,我也是第一次遇到,这里记录下。

复位问题分析过程

首先他的复位方案是采用的复位同步器,正常情况下,复位同步器的电路应该是如下这样的:

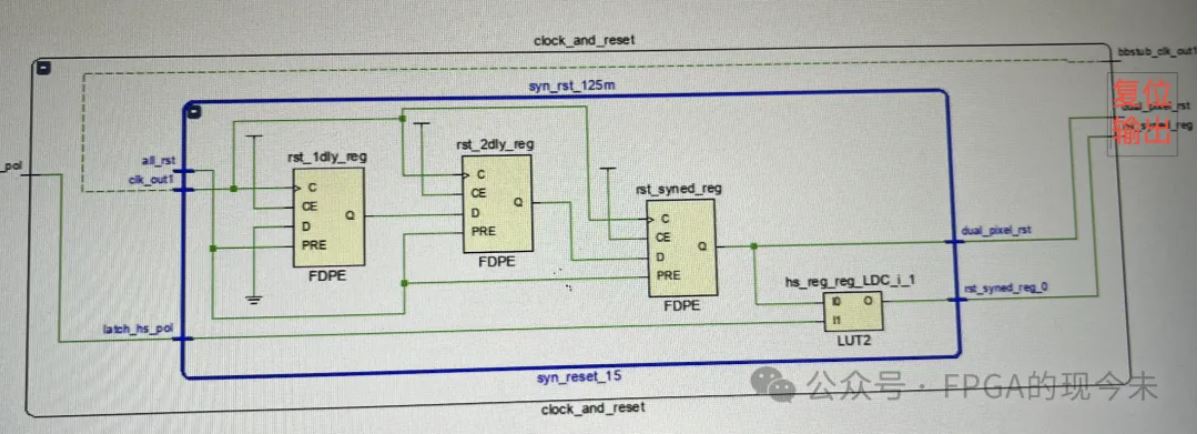

但是他的综合log中有一个告警,打开电路图,他的复位同步器是这样的,如下图所示:

发现输出了2个复位信号,其中一个复位信号还是组合逻辑输出的,这显然和设计是不一致的。仔细观察这个电路,最右边的组合逻辑有一个输入是从外部另一个模块A输入的,关系大体如下图所示。那么问题就在于模块A的信号为啥会输出到了复位同步器电路。

通过分析相关的信号和代码,找到了模块A输出到复位同步器的信号,这个信号是属于模块A的一个内部信号,并没有输出。 其代码如下图所示,当我第一次看到这个代码块的时候,也没有看出来是什么问题。但是看电路图,这个问题一定是和这段代码有关的。

always@(posedge clk_sys or posedge rst)

begin

if(rst == 1'b1) begin

latch_pol <= ~location;

end

else if((XXXX == 1'b1) && (YYYY == 1'b1)) begin

latch_pol <= ~location;

end

else if((AAA == 1'b1)&&(BBB == 1'b1)) begin

latch_pol <= location;

end

else;

end

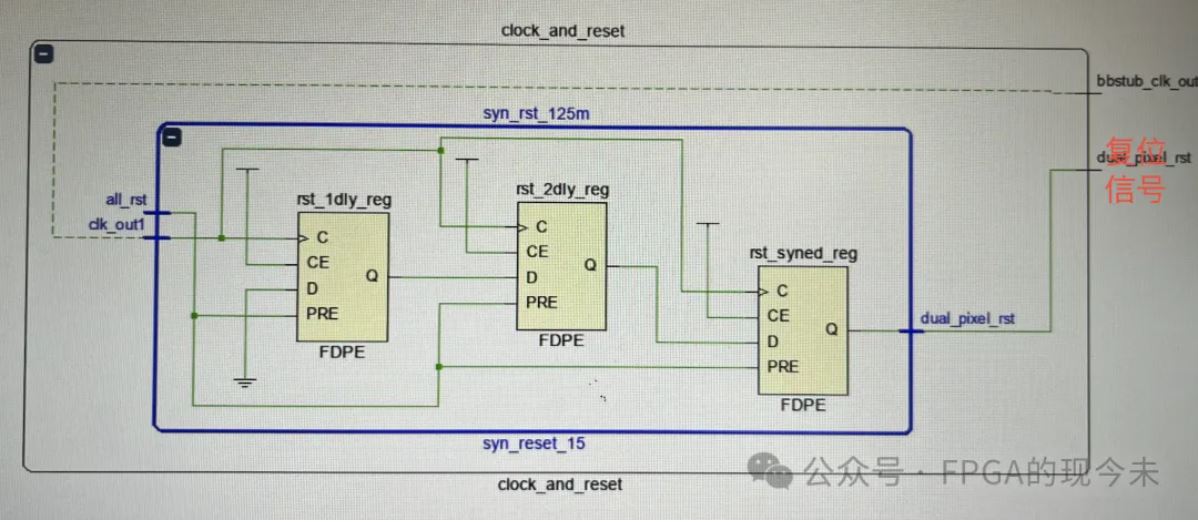

突然看到这个信号的复位值不是常量,是一个变量,会不会和这个有关?因为只有这里的复位信号和A模块输出的信号有关联。因此修改代码,将该信号的复位值修改成常量,重新综合后,问题消失,打开其电路图,如下图所示,复位同步器的电路和设计的一致。

总结

复位值必须是常量,要么是0,要么是1,也可以是parameter定义的参数,就是不能是变量。