对于Vivado Hls来说,输入包括Tesbench,C/C++源代码和Directives,相应的输出为IP Catalog,DSP和SysGen,特别的,一个工程只能有一个顶层函数用于综和,这个顶层函数下面的子函数也是可以被综合的,会生成相应的VHDL和Verilog代码,所以,C综合后的RTL代码结构通常是跟原始C描述的结构是一致的,除非是子函数功能很简单,所需要的逻辑量很小。 通常在main函数以下的函数都可以被综合,也就是说,并不是所有的C/C++都可以被综合,动态内存分配和涉及到操作系统层面的操作不可以被综合。

本文结构框架:

1.Creat New Project新建文档:

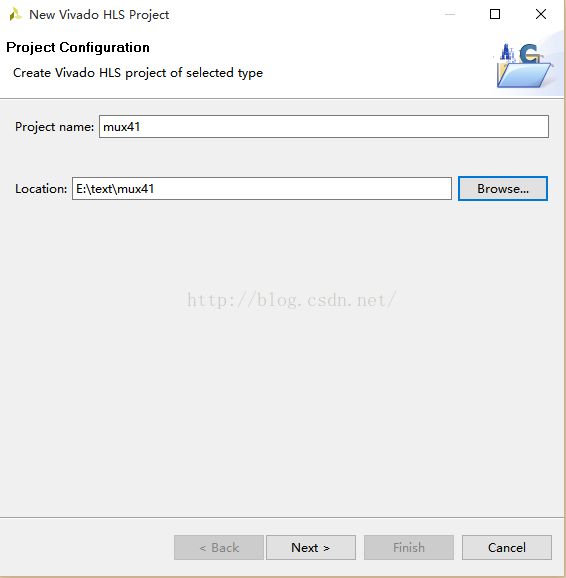

新建一个Project name,点next(这里选取简单的4选1数据选择器为例,主要是说明流程)

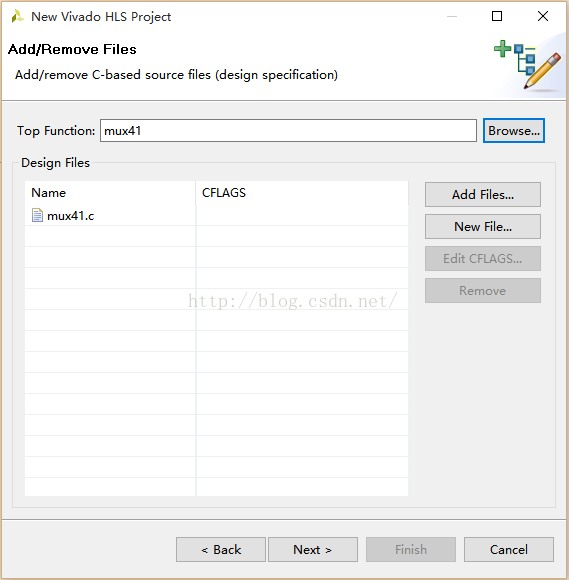

在Add Files里添加mux41.c文件,点next

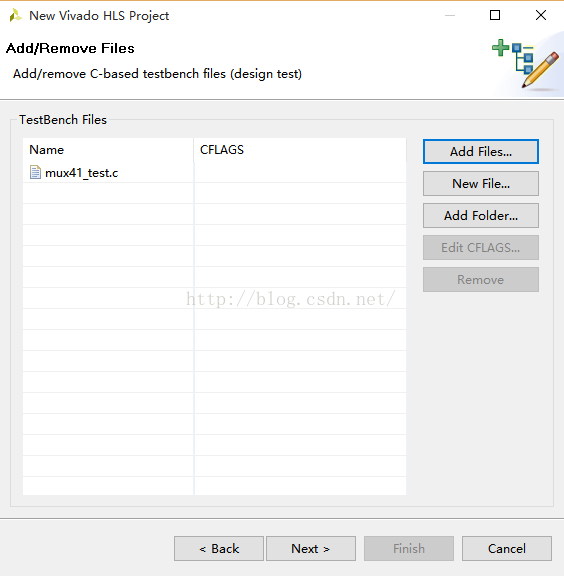

添加mux41_test测试文件,点next

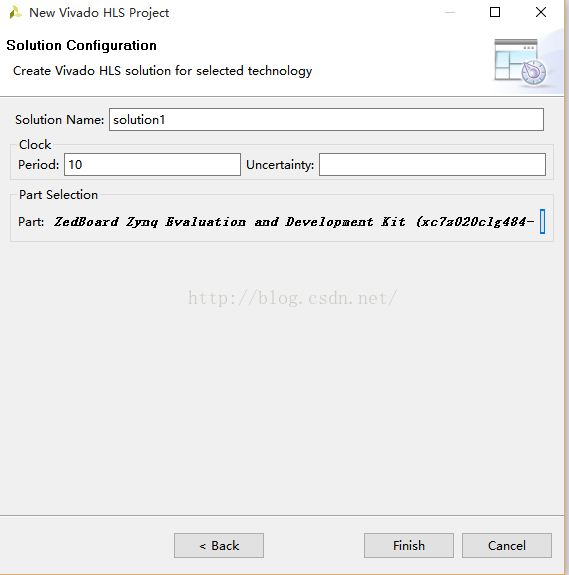

点Part,这里选择Board下面的Zedboard Zynq开发板,然后点OK和finish

注释:

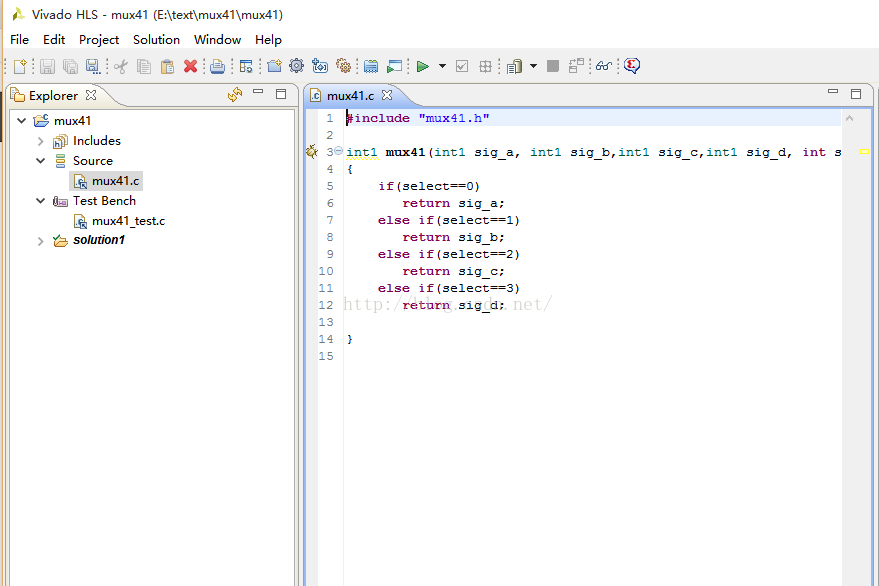

mux41.c代码:

#include "mux41.h"

int1 mux41(int1 sig_a, int1 sig_b,int1 sig_c,int1 sig_d, int select)

{

if(select==0)

return sig_a;

else if(select==1)

return sig_b;

else if(select==2)

return sig_c;

else if(select==3)

return sig_d;

}

mux41.h代码:(头文件)

#include <ap_cint.h>

mux41_tb代码:

#include <stdio.h>

#include "mux41.h"

int main(void)

{

int res1 = 0;

int res2 = 0;

int res3 = 0;

int res4 = 0;

res1=mux41(1,0,0,0,0);

res2=mux41(0,1,0,0,1);

res3=mux41(0,0,1,0,2);

res4=mux41(0,0,0,1,3);

if(res1 && res2 && res3 && res4)

printf("test passed, well done!\n");

return 0;

}2.C simulation:

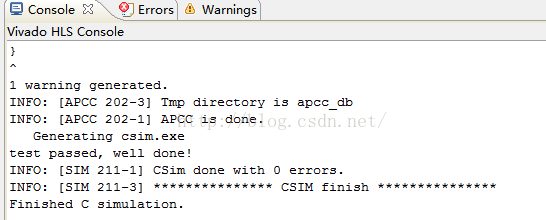

在菜单里Project>Run C simulation,C simulation可以得到csim文件

从图中看到,可以看到test passed,well done!,证明结果是正确的:

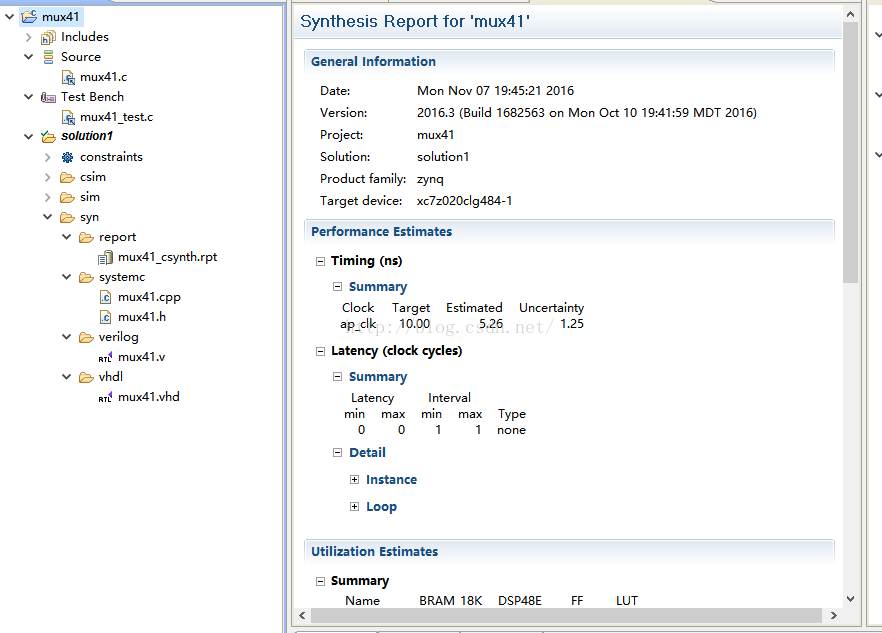

3.C systhesis:

在菜单里Solution>Run C Systhesis>Active solution,综合会得到syn文件

注意综合得到的verilog代码的可读性很差,不需要读懂,所以大多数优化都在C这个层面去做的,下面是综合后的verilog代码:

// ==============================================================

// RTL generated by Vivado(TM) HLS - High-Level Synthesis from C, C++ and SystemC

// Version: 2016.3

// Copyright (C) 1986-2016 Xilinx, Inc. All Rights Reserved.

//

// ===========================================================

`timescale 1 ns / 1 ps

(* CORE_GENERATION_INFO="mux41,hls_ip_2016_3,{HLS_INPUT_TYPE=c,HLS_INPUT_FLOAT=0,HLS_INPUT_FIXED=1,HLS_INPUT_PART=xc7z020clg484-

1,HLS_INPUT_CLOCK=10.000000,HLS_INPUT_ARCH=others,HLS_SYN_CLOCK=5.258000,HLS_SYN_LAT=0,HLS_SYN_TPT=none,HLS_SYN_MEM=0,HLS_SYN_DSP=0,HLS_SYN_FF=0,HLS_SYN_LUT=41}" *)

module mux41 (

ap_start,

ap_done,

ap_idle,

ap_ready,

sig_a,

sig_b,

sig_c,

sig_d,

select_r,

ap_return

);

parameter ap_const_lv32_0 = 32'b00000000000000000000000000000000;

parameter ap_const_lv32_1 = 32'b1;

parameter ap_const_lv32_2 = 32'b10;

input ap_start;

output ap_done;

output ap_idle;

output ap_ready;

input [0:0] sig_a;

input [0:0] sig_b;

input [0:0] sig_c;

input [0:0] sig_d;

input [31:0] select_r;

output [0:0] ap_return;

wire [0:0] tmp_fu_60_p2;

wire [0:0] tmp_1_fu_66_p2;

wire [0:0] sel_tmp1_fu_86_p2;

wire [0:0] sel_tmp2_fu_92_p2;

wire [0:0] sel_tmp_fu_78_p3;

wire [0:0] tmp_2_fu_72_p2;

wire [0:0] tmp7_fu_106_p2;

wire [0:0] sel_tmp5_fu_112_p2;

wire [0:0] p_0_fu_98_p3;

assign ap_done = ap_start;

assign ap_idle = 1'b1;

assign ap_ready = ap_start;

assign ap_return = ((sel_tmp5_fu_112_p2[0:0] === 1'b1) ? p_0_fu_98_p3 : sig_d);

assign p_0_fu_98_p3 = ((sel_tmp2_fu_92_p2[0:0] === 1'b1) ? sig_b : sel_tmp_fu_78_p3);

assign sel_tmp1_fu_86_p2 = (tmp_fu_60_p2 ^ 1'b1);

assign sel_tmp2_fu_92_p2 = (tmp_1_fu_66_p2 & sel_tmp1_fu_86_p2);

assign sel_tmp5_fu_112_p2 = (tmp7_fu_106_p2 | tmp_fu_60_p2);

assign sel_tmp_fu_78_p3 = ((tmp_fu_60_p2[0:0] === 1'b1) ? sig_a : sig_c);

assign tmp7_fu_106_p2 = (tmp_1_fu_66_p2 | tmp_2_fu_72_p2);

assign tmp_1_fu_66_p2 = ((select_r == ap_const_lv32_1) ? 1'b1 : 1'b0);

assign tmp_2_fu_72_p2 = ((select_r == ap_const_lv32_2) ? 1'b1 : 1'b0);

assign tmp_fu_60_p2 = ((select_r == ap_const_lv32_0) ? 1'b1 : 1'b0);

endmodule //mux414.RTL级仿真:

在菜单里Solution>RunC/RTL cosimulation,需要对Co-similation Dialog设置如下:

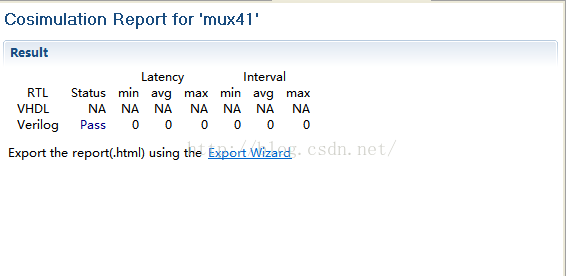

得到如下结果,我们会发现Verilog的Status是pass,证明C/RTL cosimulation成功:

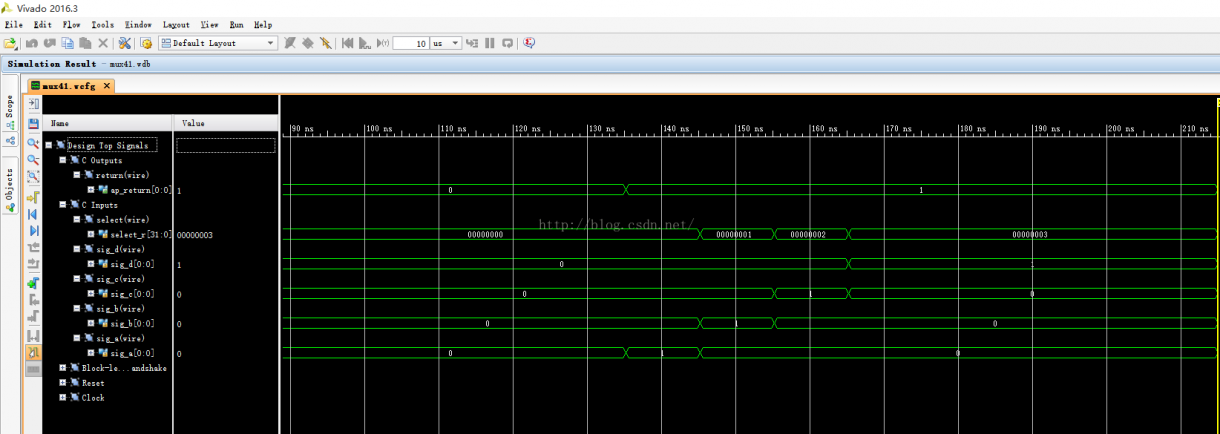

然后我们点开波形查看窗口,此时会自动打开Vivado软件,从图中看到,mux41的功能正确:

5.IP封装:

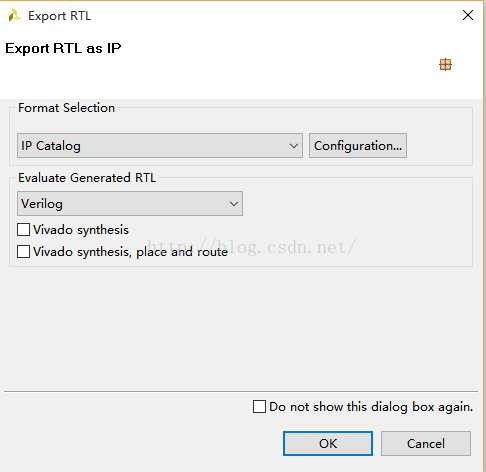

在菜单里Solution>Export TL,设置如下:

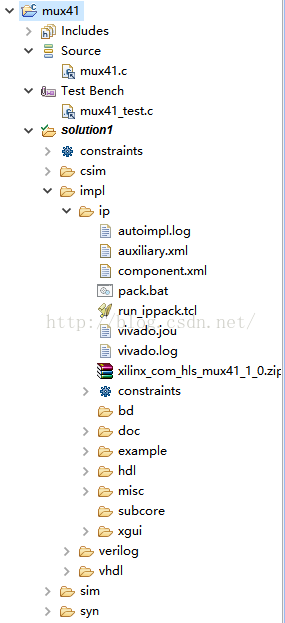

IP封装后,会得到impl文件,其中就有我们所需要的三个子文件ip,verilog,vhdl

总结:

事实上,在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。随后需要用 GCC/G++或 Visual C++ 仿真器验证设计的系统行为。一旦行为设计运行良好,对应的测试台的问题全部解决,就可以通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。有了 RTL 后,随即可以执行设计的 Verilog 或 VHDL 仿真,或使用工具的C封装器技术创建 SystemC 版本。然后可以进行System C架构级仿真,进一步根据之前创建的 C 测试平台,验证设计的架构行为和功能。设计固化后,就可以通过 Vivado 设计套件的物理实现流程来运行设计,将设计编程到器件上,在硬件中运行和/或使用 IP 封装器将设计转为可重用的 IP。随后使用 IP 集成器将 IP 集成到设计中,或在系统生成器 (System Generator) 中运行 IP。

本文转载自: https://blog.csdn.net/Gentleman_Qin/article/details/80010751