引言

在上一个视频系列中(编号 21)中,我们创建了一种设计,可将模式(使用的是 LogiCORE™ IP 视频测试模式生成器 (TPG) 的核)发送到 Zynq®-7000 SoC ZC702 评估套件的板载 HDMI 中。

但这个应用硬件设计中的分辨率固定为 800x600p(在应用中无法对其进行更改)。

在本视频系列中,我们来了解一下如何修改硬件设计和应用以支持多种视频分辨率。

教程 – 在 ZC702 评估板上支持多种 HDMI 分辨率 (TX)

注意:本教程仅适用于 Vivado Design Suite 2018.1,且仅适用于 ZC702 评估板。

构建 Vivado 工程

- 下载教程文件并解压文件夹。

- 打开 Vivado Design Suite 2018.1。

- 在 Tcl 控制台中,使用 cd 导航到解压的目录:

cd

4. 在 Tcl 控制台中,用 source 来写脚本 tcl:

source ./create_proj.tcl

注意:构建设计需要有效的测试模式生成器许可证。

添加配置接口 (AXI4-Lite)

5. 双击视频定时控制器 (VTC) IP 打开其配置 GUI。

6. 启用“Include AXI4-Lite Interface”。此操作会允许我们从处理器设置 VTC IP,并允许我们从软件应用进行配置。

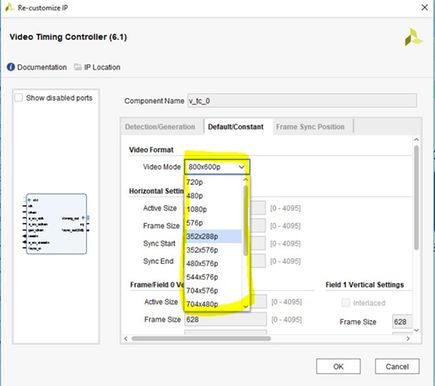

7. 单击 Default/Constant 标签,然后展开 Video Mode 选项。您可以看到 VTC IP 中包含的所有预设分辨率。

在这个视频系列中,我们只支持 800x600p、1024x768p 和 720p(1280x720p)。

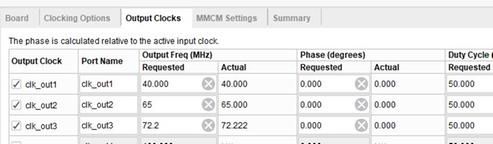

我们在网上可以找到这些分辨率的像素时钟,1024x768p 适用于 65 MHz,而 1280x720p 适用于 72.2 MHz。

(请注意,800x600 所需的时钟为 40 MHz)。

8. 保持视频模式为 800x600p。

9. 单击“OK”关闭 VTC IP 的配置 GUI。

10. 在块设计上单击“Run Connection Automation”。

11. 确保选中“All Automation”,然后单击“OK”。

Vivado 会自动地将 VTC IP 连接到 Zynq 处理器。

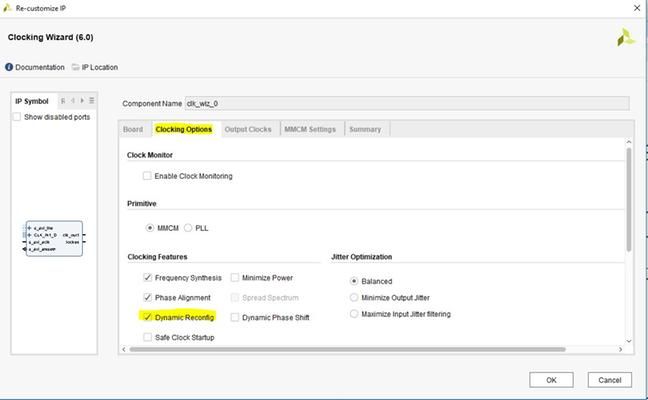

12. 双击时钟向导 (clk_wiz_0) 打开其配置 GUI。

13. 单击“Clocking Option”标签并启用“Dynamic Reconfig”。

14. 在“Output Clocks"标签中,确保将 clk_out1 设置为“40MHz”,然后启用 clk_out2 和 clk_out3 并将其频率设置为“65MHz”和“72.2MHz”。

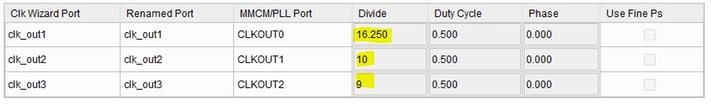

15. 转到“MMCM Setting”标签,然后检查 3 个时钟的 MMCM 配置分频值。

16. 单击“Allow Override Mode”以保留 MMCM 设置。

17. 返回到“Output Clocks”标签并禁用 clk_out2 和 clk_out3。

我们将仅使用 clk_out1,更改其 Divide 设置以更改其频率。

18. 单击“OK”关闭“Clocking Wizard”的配置 GUI。

19. 在块设计上,单击“Run Connection Automation”,确保已启用“All Automation”选项,然后单击“OK”。

20. 验证块设计 (BD)。您应该不会收到重大警告或错误信息。保存 BD。

21. 在“Sources”窗口中,右键单击 BD 并选择“Generate Output Products”。

22. 输出产品生成结束后,在源窗口中右键单击 BD,然后单击“Create HDL wrapper”。

23. 运行 Vivado 综合和 Vivado 实现,然后生成比特流。

创建软件开发套件 (SDK) 应用

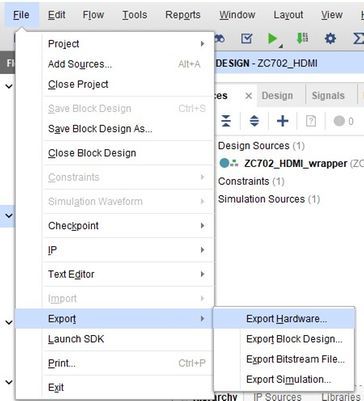

24. 将硬件导出到 SDK。单击“File > Export > Export Hardware”。

25. 确保已启用“Include Bitstream”并将导出位置更改为

26. 关闭 Vivado。

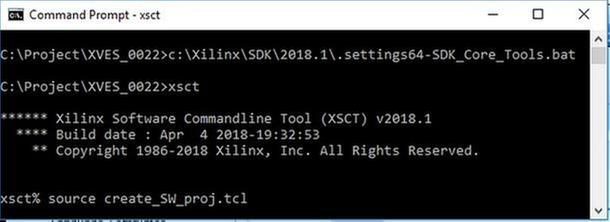

27. 启动赛灵思软件命令行工具 (XSCT) 2018.1。

“Start > All Programs > Xilinx Design Tools > Xilinx Software Command Line Tool 2018.1”。

使用命令 xsct(需要设置 SDK 2018.1 的环境变量)

28. 在 xsct中,cd 到解压文件夹的路径,然后输入下列命令:

source create_SW_proj.tcl

29. 打开 SDK 并选择 XVES_0024/sdk_workspace 作为工作空间。

此应用基于之前视频系列的应用。请注意,在此版本中,应用启动时会在代码中启用 VTC 生成器。

测试应用

30. 构建 tpg_hdmi_zc702_app 应用。

31. 确保将 ZC702 连接到 UART、JTAG 和 HDMI。

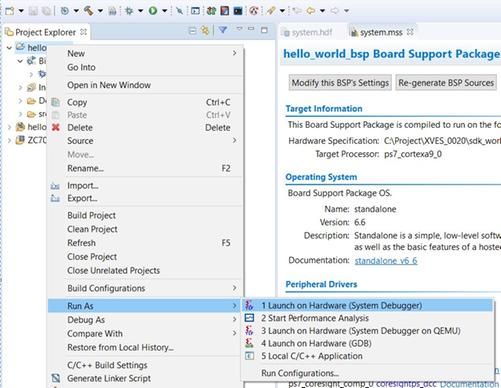

32. 单击“Xilinx > Program FPGA”,然后,选择程序。

33. 在 SDK 中,在项目资源管理器中,右键单击 tpg_hdmi_zc702_app 应用,然后选择“Run As >Launch on Hardware”(系统调试器)。

注意:此步骤假定您的电路板是在本地连接而不是通过服务器连接的。

您应该会看到显示器上显示的图案带有绿色移动框。

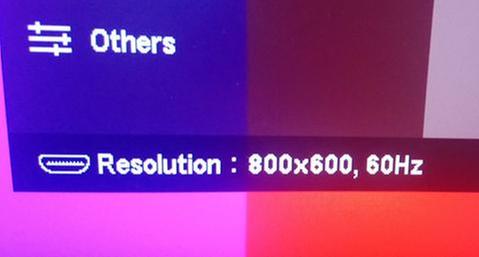

如果您进入显示器菜单,您会看到它准确无误地显示的 800x600@60Hz 图像。

更新应用以使用其他输出分辨率

您首先需要更改时钟向导的设置。您需要在时钟向导中更改的唯一参数是寄存器 0x208 中的 CLKOUT0 DIV。

请注意,寄存器的位 [17:8] 表示 DIV 值的小数部分,位 [7:8] 表示整数部分。

对于 65 MHz,要将 DIV 设置为 10,寄存器值将为 0x08。 对于 40 MHz,要将 DIV 设置为 16.250,寄存器值将为 0xFA10。

34. 将以下代码添加到应用 (tpg_hdmi_ZC702.c):

/* Clocking Wizard Configuration */

//Configure the CLKOUT0 DIV

Xil_Out32(ClkWiz_CfgPtr->BaseAddr + 0x208, 0x000A);

/* End of clocking wizard configuration */

然后,您需要通过设置时钟向导的寄存器 0x25C 中的值 0x1 来加载时钟配置。

35. 要设置应用,请添加以下代码:

/* Clocking Wizard Configuration */

//Configure the CLKOUT0 DIV

Xil_Out32(ClkWiz_CfgPtr->BaseAddr + 0x208, 0x000A);

Xil_Out32(ClkWiz_CfgPtr->BaseAddr + 0x25C, 0x3);

/* End of clocking wizard configuration */

36. 将应用中的 TPG 输出分辨率更改为 1024x768。

//Configure the TPG

app_hdmi_conf_tpg(&tpg_inst, 768, 1024, 0x2, XTPG_BKGND_COLOR_BARS);

最后,您需要更改 VTC 的配置。

37. 要设置应用,请添加以下代码:

请注意,VMODE_XGA 代表 1024x768 的视频分辨率(XVTC_VMODE_SVGA 适用于 800x600、XVTC_VMODE_720P 适用于 720P)

/* VTC Configuration */

XVtc_ConvVideoMode2Timing(&VtcInst,XVTC_VMODE_XGA,&XVtc_Timingconf);

XVtc_SetGeneratorTiming(&VtcInst, &XVtc_Timingconf);

XVtc_RegUpdate(&VtcInst);

/* End of VTC Configuration */

38. 重新构建应用、重新对 PL 进行编程(Xilinx>Program)并重新启动应用。

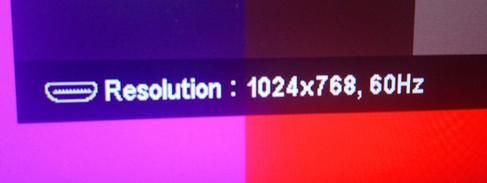

现在,检测器菜单应该会按预期指示输出分辨率为 1024x768 了。

39. 要显示 720p 输出,请尝试更改应用。

请注意,本教程中介绍的如何使用时钟向导的方法,只是更改视频时钟的一种方法。ZC702 套件内置有可编程时钟,因此也可用于此目的。

文章转载自:赛灵思中文社区论坛