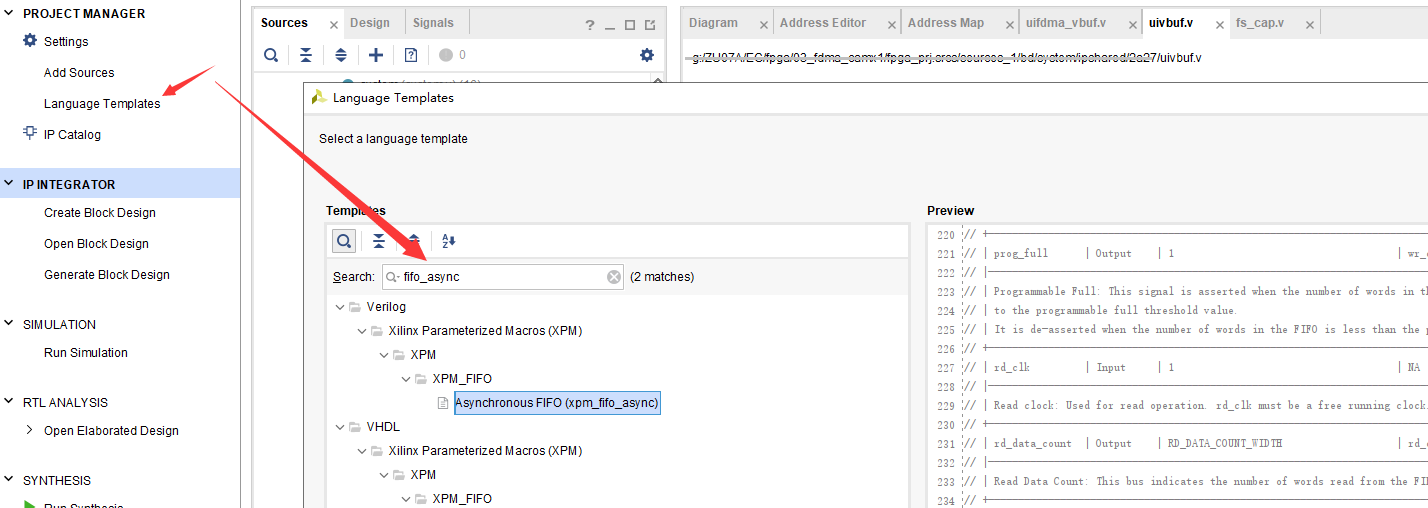

使用Xilinx源语来描述FIFO具有很多好处,可以通过Xilinx Vivado 工具的Langguage Templates查看源语定义。

xpm_fifo_async #(

.CDC_SYNC_STAGES(2), // DECIMAL

.DOUT_RESET_VALUE("0"), // String

.ECC_MODE("no_ecc"), // String

.FIFO_MEMORY_TYPE("auto"), // String

.FIFO_READ_LATENCY(1), // DECIMAL

.FIFO_WRITE_DEPTH(2048), // DECIMAL

.FULL_RESET_VALUE(0), // DECIMAL

.PROG_EMPTY_THRESH(10), // DECIMAL

.PROG_FULL_THRESH(10), // DECIMAL

.RD_DATA_COUNT_WIDTH(1), // DECIMAL

.READ_DATA_WIDTH(32), // DECIMAL

.READ_MODE("std"), // String

.RELATED_CLOCKS(0), // DECIMAL

.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.USE_ADV_FEATURES("0707"), // String

.WAKEUP_TIME(0), // DECIMAL

.WRITE_DATA_WIDTH(32), // DECIMAL

.WR_DATA_COUNT_WIDTH(1) // DECIMAL

)

xpm_fifo_async_inst (

.almost_empty(almost_empty), // 1-bit output: Almost Empty : When asserted, this signal indicates that

// only one more read can be performed before the FIFO goes to empty.

.almost_full(almost_full), // 1-bit output: Almost Full: When asserted, this signal indicates that

// only one more write can be performed before the FIFO is full.

.data_valid(data_valid), // 1-bit output: Read Data Valid: When asserted, this signal indicates

// that valid data is available on the output bus (dout).

.dbiterr(dbiterr), // 1-bit output: Double Bit Error: Indicates that the ECC decoder detected

// a double-bit error and data in the FIFO core is corrupted.

.dout(dout), // READ_DATA_WIDTH-bit output: Read Data: The output data bus is driven

// when reading the FIFO.

.empty(empty), // 1-bit output: Empty Flag: When asserted, this signal indicates that the

// FIFO is empty. Read requests are ignored when the FIFO is empty,

// initiating a read while empty is not destructive to the FIFO.

.full(full), // 1-bit output: Full Flag: When asserted, this signal indicates that the

// FIFO is full. Write requests are ignored when the FIFO is full,

// initiating a write when the FIFO is full is not destructive to the

// contents of the FIFO.

.overflow(overflow), // 1-bit output: Overflow: This signal indicates that a write request

// (wren) during the prior clock cycle was rejected, because the FIFO is

// full. Overflowing the FIFO is not destructive to the contents of the

// FIFO.

.prog_empty(prog_empty), // 1-bit output: Programmable Empty: This signal is asserted when the

// number of words in the FIFO is less than or equal to the programmable

// empty threshold value. It is de-asserted when the number of words in

// the FIFO exceeds the programmable empty threshold value.

.prog_full(prog_full), // 1-bit output: Programmable Full: This signal is asserted when the

// number of words in the FIFO is greater than or equal to the

// programmable full threshold value. It is de-asserted when the number of

// words in the FIFO is less than the programmable full threshold value.

.rd_data_count(rd_data_count), // RD_DATA_COUNT_WIDTH-bit output: Read Data Count: This bus indicates the

// number of words read from the FIFO.

.rd_rst_busy(rd_rst_busy), // 1-bit output: Read Reset Busy: Active-High indicator that the FIFO read

// domain is currently in a reset state.

.sbiterr(sbiterr), // 1-bit output: Single Bit Error: Indicates that the ECC decoder detected

// and fixed a single-bit error.

.underflow(underflow), // 1-bit output: Underflow: Indicates that the read request (rd_en) during

// the previous clock cycle was rejected because the FIFO is empty. Under

// flowing the FIFO is not destructive to the FIFO.

.wr_ack(wr_ack), // 1-bit output: Write Acknowledge: This signal indicates that a write

// request (wr_en) during the prior clock cycle is succeeded.

.wr_data_count(wr_data_count), // WR_DATA_COUNT_WIDTH-bit output: Write Data Count: This bus indicates

// the number of words written into the FIFO.

.wr_rst_busy(wr_rst_busy), // 1-bit output: Write Reset Busy: Active-High indicator that the FIFO

// write domain is currently in a reset state.

.din(din), // WRITE_DATA_WIDTH-bit input: Write Data: The input data bus used when

// writing the FIFO.

.injectdbiterr(injectdbiterr), // 1-bit input: Double Bit Error Injection: Injects a double bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.injectsbiterr(injectsbiterr), // 1-bit input: Single Bit Error Injection: Injects a single bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.rd_clk(rd_clk), // 1-bit input: Read clock: Used for read operation. rd_clk must be a free

// running clock.

.rd_en(rd_en), // 1-bit input: Read Enable: If the FIFO is not empty, asserting this

// signal causes data (on dout) to be read from the FIFO. Must be held

// active-low when rd_rst_busy is active high.

.rst(rst), // 1-bit input: Reset: Must be synchronous to wr_clk. The clock(s) can be

// unstable at the time of applying reset, but reset must be released only

// after the clock(s) is/are stable.

.sleep(sleep), // 1-bit input: Dynamic power saving: If sleep is High, the memory/fifo

// block is in power saving mode.

.wr_clk(wr_clk), // 1-bit input: Write clock: Used for write operation. wr_clk must be a

// free running clock.

.wr_en(wr_en) // 1-bit input: Write Enable: If the FIFO is not full, asserting this

// signal causes data (on din) to be written to the FIFO. Must be held

// active-low when rst or wr_rst_busy is active high.

);

使用XILINX源语来描述FIFO具有很多好处,可以通过XILINX VIVADO 工具的Langguage Templates查看源语定义。

xpm_fifo_async #(

.CDC_SYNC_STAGES(2), // DECIMAL

.DOUT_RESET_VALUE("0"), // String

.ECC_MODE("no_ecc"), // String

.FIFO_MEMORY_TYPE("auto"), // String

.FIFO_READ_LATENCY(1), // DECIMAL

.FIFO_WRITE_DEPTH(2048), // DECIMAL

.FULL_RESET_VALUE(0), // DECIMAL

.PROG_EMPTY_THRESH(10), // DECIMAL

.PROG_FULL_THRESH(10), // DECIMAL

.RD_DATA_COUNT_WIDTH(1), // DECIMAL

.READ_DATA_WIDTH(32), // DECIMAL

.READ_MODE("std"), // String

.RELATED_CLOCKS(0), // DECIMAL

.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.USE_ADV_FEATURES("0707"), // String

.WAKEUP_TIME(0), // DECIMAL

.WRITE_DATA_WIDTH(32), // DECIMAL

.WR_DATA_COUNT_WIDTH(1) // DECIMAL

)

xpm_fifo_async_inst (

.almost_empty(almost_empty), // 1-bit output: Almost Empty : When asserted, this signal indicates that

// only one more read can be performed before the FIFO goes to empty.

.almost_full(almost_full), // 1-bit output: Almost Full: When asserted, this signal indicates that

// only one more write can be performed before the FIFO is full.

.data_valid(data_valid), // 1-bit output: Read Data Valid: When asserted, this signal indicates

// that valid data is available on the output bus (dout).

.dbiterr(dbiterr), // 1-bit output: Double Bit Error: Indicates that the ECC decoder detected

// a double-bit error and data in the FIFO core is corrupted.

.dout(dout), // READ_DATA_WIDTH-bit output: Read Data: The output data bus is driven

// when reading the FIFO.

.empty(empty), // 1-bit output: Empty Flag: When asserted, this signal indicates that the

// FIFO is empty. Read requests are ignored when the FIFO is empty,

// initiating a read while empty is not destructive to the FIFO.

.full(full), // 1-bit output: Full Flag: When asserted, this signal indicates that the

// FIFO is full. Write requests are ignored when the FIFO is full,

// initiating a write when the FIFO is full is not destructive to the

// contents of the FIFO.

.overflow(overflow), // 1-bit output: Overflow: This signal indicates that a write request

// (wren) during the prior clock cycle was rejected, because the FIFO is

// full. Overflowing the FIFO is not destructive to the contents of the

// FIFO.

.prog_empty(prog_empty), // 1-bit output: Programmable Empty: This signal is asserted when the

// number of words in the FIFO is less than or equal to the programmable

// empty threshold value. It is de-asserted when the number of words in

// the FIFO exceeds the programmable empty threshold value.

.prog_full(prog_full), // 1-bit output: Programmable Full: This signal is asserted when the

// number of words in the FIFO is greater than or equal to the

// programmable full threshold value. It is de-asserted when the number of

// words in the FIFO is less than the programmable full threshold value.

.rd_data_count(rd_data_count), // RD_DATA_COUNT_WIDTH-bit output: Read Data Count: This bus indicates the

// number of words read from the FIFO.

.rd_rst_busy(rd_rst_busy), // 1-bit output: Read Reset Busy: Active-High indicator that the FIFO read

// domain is currently in a reset state.

.sbiterr(sbiterr), // 1-bit output: Single Bit Error: Indicates that the ECC decoder detected

// and fixed a single-bit error.

.underflow(underflow), // 1-bit output: Underflow: Indicates that the read request (rd_en) during

// the previous clock cycle was rejected because the FIFO is empty. Under

// flowing the FIFO is not destructive to the FIFO.

.wr_ack(wr_ack), // 1-bit output: Write Acknowledge: This signal indicates that a write

// request (wr_en) during the prior clock cycle is succeeded.

.wr_data_count(wr_data_count), // WR_DATA_COUNT_WIDTH-bit output: Write Data Count: This bus indicates

// the number of words written into the FIFO.

.wr_rst_busy(wr_rst_busy), // 1-bit output: Write Reset Busy: Active-High indicator that the FIFO

// write domain is currently in a reset state.

.din(din), // WRITE_DATA_WIDTH-bit input: Write Data: The input data bus used when

// writing the FIFO.

.injectdbiterr(injectdbiterr), // 1-bit input: Double Bit Error Injection: Injects a double bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.injectsbiterr(injectsbiterr), // 1-bit input: Single Bit Error Injection: Injects a single bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.rd_clk(rd_clk), // 1-bit input: Read clock: Used for read operation. rd_clk must be a free

// running clock.

.rd_en(rd_en), // 1-bit input: Read Enable: If the FIFO is not empty, asserting this

// signal causes data (on dout) to be read from the FIFO. Must be held

// active-low when rd_rst_busy is active high.

.rst(rst), // 1-bit input: Reset: Must be synchronous to wr_clk. The clock(s) can be

// unstable at the time of applying reset, but reset must be released only

// after the clock(s) is/are stable.

.sleep(sleep), // 1-bit input: Dynamic power saving: If sleep is High, the memory/fifo

// block is in power saving mode.

.wr_clk(wr_clk), // 1-bit input: Write clock: Used for write operation. wr_clk must be a

// free running clock.

.wr_en(wr_en) // 1-bit input: Write Enable: If the FIFO is not full, asserting this

// signal causes data (on din) to be written to the FIFO. Must be held

// active-low when rst or wr_rst_busy is active high.

);

UG974中有关于xpm_fifo_async的具体描述,在配套工程的uisrc/doc路径下,已经提供了下载好的“ug974-vivado-ultrascale-libraries.pdf”。

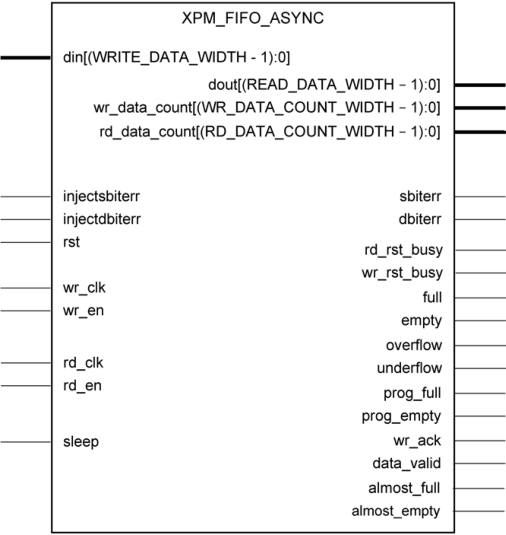

接口描述如下(摘录于ug974):

|

Port |

Direction |

Function

|

|

almost_empty |

Output |

Almost Empty : When asserted,this signal indicates that only one more read can be performed before the FIFO goes to empty. |

|

almost_full |

Output |

Almost Full: When asserted, this signal indicates that only one more write can be performed before the FIFO is full. |

|

data_valid |

Output |

Read Data Valid: When asserted,this signal indicates that valid data is available on the output bus (dout). |

|

dbiterr |

Output |

Double Bit Error: Indicates that the ECC decoder detected a double-bit error and data in the FIFO core is corrupted. |

|

Din[WRITE_DATA_WIDTH-1 :0] |

Input |

Write Data: The input data bus used when writing the FIFO. |

|

dout |

Output |

Read Data: The output data bus is driven when reading the FIFO |

|

empty |

Output |

Empty Flag: When asserted, this signal indicates that the FIFO is empty. Read requests are ignored when the FIFO is empty, initiating a read while empty is not destructive to the FIFO. |

|

full |

Output |

Full Flag: When asserted, this signal indicates that the FIFO is full. Write requests are ignored when the FIFO is full, initiating a write when the FIFO is full is not destructive to the contents of the FIFO. |

|

injectdbiterr |

Input |

Double Bit Error Injection: Injects a double bit error if the ECC feature is used on block RAMs or UltraRAM macros. |

|

injectsbiterr |

Input |

Single Bit Error Injection: Injects a single bit error if the ECC feature is used on block RAMs or UltraRAM macros. |

|

overflow |

Output |

Overflow: This signal indicates that a write request (wren) during the prior clock cycle was rejected, because the FIFO is full. Overflowing the FIFO is not destructive to the contents of the FIFO. |

|

prog_empty |

|

Programmable Empty: This signal is asserted when the number of words in the FIFO is less than or equal to the programmable empty threshold value. It is de-asserted when the number of words in the FIFO exceeds the programmable empty threshold value. |

|

prog_full |

|

Programmable Full: This signal is asserted when the number of words in the FIFO is greater than or equal to the programmable full threshold value. It is de-asserted when the number of words in the FIFO is less than the programmable full threshold value. |

|

rd_clk |

Input |

Read clock: Used for read operation. rd_clk must be a free running clock. |

|

rd_data_coun[RD_DATA_COUNT_WIDTH-1:0] |

Output |

Read Data Count: This bus indicates the number of words read from the FIFO. |

|

rd_en |

Input |

Read Enable: If the FIFO is not empty, asserting this signal causes data (on dout) to be read from the FIFO. Must be held active-low when rd_rst_busy is active high. |

|

rd_rst_busy |

Output |

Read Reset Busy: Active-High indicator that the FIFO read domain is currently in a reset state. |

|

rst |

Input |

Reset: Must be synchronous to wr_clk. Must be applied only when wr_clk is stable and free-running. |

|

sbiterr |

Output |

Single Bit Error: Indicates that the ECC decoder detected and fixed a single-bit error. |

|

sleep |

Input |

Dynamic power saving: If sleep is High, the memory/fifo block is in power saving mode. |

|

underflow |

Output |

Underflow: Indicates that the read request (rd_en) during the previous clock cycle was rejected because the FIFO is empty.Under flowing the FIFO is not destructive to the FIFO. |

|

wr_ack |

Output |

Write Acknowledge: This signal indicates that a write request(wr_en) during the prior clock cycle is succeeded. |

|

wr_clk |

Input |

Write clock: Used for write operation. wr_clk must be a free running clock. |

|

wr_data_coun[WR_DATA_COUNT_WIDTH-1:0] |

Output |

Write Data Count: This bus indicates the number of words written into the FIFO. |

|

wr_en |

Input |

Write Enable: If the FIFO is not full, asserting this signal causes data (on din) to be written to the FIFO. Must be held active-low when rst or wr_rst_busy is active high. |

|

wr_rst_busy |

Output |

Write Reset Busy: Active-High indicator that the FIFO write domain is currently in a reset state. |

接口参数描述如下:

|

Attribute |

Allowed Values |

Default |

Description |

|

CDC_SYNC_STAGES |

2 to 8 |

2 |

Specifies the number of synchronization stages on the CDC path Must be < 5 if FIFO_WRITE_DEPTH = 16 |

|

DOUT_RESET_VALUE |

String |

"0" |

Reset value of read data path. |

|

ECC_MODE |

"no_ecc", "en_ecc" |

"no_ecc" |

• "no_ecc" - Disables ECC • "en_ecc" - Enables both ECC Encoder and Decoder |

|

FIFO_MEMORY_TYPE |

"auto", "block", "distributed" |

"auto" |

Designate the fifo memory primitive(resource type) to use. • "auto" - Allow Vivado Synthesis to choose • "block" - Block RAM FIFO • "distributed" - Distributed RAM FIFO |

|

FIFO_READ_LATENCY |

0 to 10 |

1 |

Number of output register stages in the read data path. If READ_MODE = "fwft", then the only applicable value is 0. |

|

FIFO_WRITE_DEPTH |

16 to 4194304 |

2048 |

Defines the FIFO Write Depth, must be power of two. • In standard READ_MODE, the effective depth = FIFO_WRITE_DEPTH - 1 • In First - Word - Fall – Through READ_MODE, the effective depth =FIFO_WRITE_DEPTH + 1 |

|

FULL_RESET_VALUE |

0 to 1 |

0 |

Sets full, almost_full and prog_full to FULL_RESET_VALUE during reset |

|

PROG_EMPTY_THRESH |

3 to 4194301 |

10 |

Specifies the minimum number of read words in the FIFO at or below which prog_empty is asserted. • Min_Value = 3 + (READ_MODE_VAL * 2) • Max_Value = (FIFO_WRITE_DEPTH - 3) -(READ_MODE_VAL * 2) If READ_MODE = "std", then READ_MODE_VAL = 0; Otherwise READ_MODE_VAL = 1. NOTE: The default threshold value is dependent on default FIFO_WRITE_DEPTH value. If FIFO_WRITE_DEPTH value is changed, ensure the threshold value is within the valid range though the programmable flags are not used. |

|

PROG_FULL_THRESH |

5 to 4194301 |

10 |

Specifies the maximum number of write words in the FIFO at or above which prog_full is asserted. • Min_Value = 3 + (READ_MODE_VAL* 2 * (FIFO_WRITE_DEPTH/ FIFO_READ_DEPTH)) + CDC_SYNC_STAGES • Max_Value = (FIFO_WRITE_DEPTH- 3) - (READ_MODE_VAL *2 * (FIFO_WRITE_DEPTH /FIFO_READ_DEPTH)) If READ_MODE = "std", then READ_MODE_VAL = 0; Otherwise READ_MODE_VAL = 1. NOTE: The default threshold value is dependent on default FIFO_WRITE_DEPTH value. If FIFO_WRITE_DEPTH value is changed, ensure the threshold value is within the valid range though the programmable flags are not used. |

|

RD_DATA_COUNT_WIDTH |

1 to 23 |

1 |

Specifies the width of rd_data_count FIFO_READ_DEPTH = FIFO_WRITE_DEPTH *WRITE_DATA_WIDTH / READ_DATA_WIDTH |

|

READ_DATA_WIDTH |

1 to 4096 |

32 |

Defines the width of the read data port, dout |

|

READ_MODE |

"std", "fwft" |

"std" |

• "std" - standard read mode • "fwft" - First - Word - Fall – Through read mode |

|

RELATED_CLOCKS |

0 to 1 |

0 |

Specifies if the wr_clk and rd_clk are related having the same source but different clock ratios |

|

USE_ADV_FEATURES |

String |

"0707" |

Enables data_valid, almost_empty,rd_data_count, prog_empty, underflow,wr_ack, almost_full, wr_data_count, prog_full,overflow features. • Setting USE_ADV_FEATURES[0] to 1 enables overflow flag; Default value of this bit is 1 • Setting USE_ADV_FEATURES[1] to 1 enables prog_full flag; Default value of this bit is 1 • Setting USE_ADV_FEATURES[2] to 1 enables wr_data_count; Default value of this bit is 1 • Setting USE_ADV_FEATURES[3] to 1 enables almost_full flag; Default value of this bit is 0 • Setting USE_ADV_FEATURES[4] to 1 enables wr_ack flag; Default value of this bit is 0 • Setting USE_ADV_FEATURES[8] to 1 enables underflow flag; Default value of this bit is 1 • Setting USE_ADV_FEATURES[9] to 1 enables prog_empty flag; Default value of this bit is 1 • Setting USE_ADV_FEATURES[10] to 1 enables rd_data_count; Default value of this bit is 1 • Setting USE_ADV_FEATURES[11] to 1 enables almost_empty flag; Default value of this bit is 0 • Setting USE_ADV_FEATURES[12] to 1 enables data_valid flag; Default value of this bit is 0 |

|

WAKEUP_TIM |

0 to 2 |

|

• 0 - Disable sleep • 2 - Use Sleep Pin |

|

WR_DATA_COUNT_WIDTH |

1 to 23 |

1 |

Specifies the width of wr_data_count |

|

WRITE_DATA_WIDTH |

1 to 4096 |

32 |

Defines the width of the write data port, din |

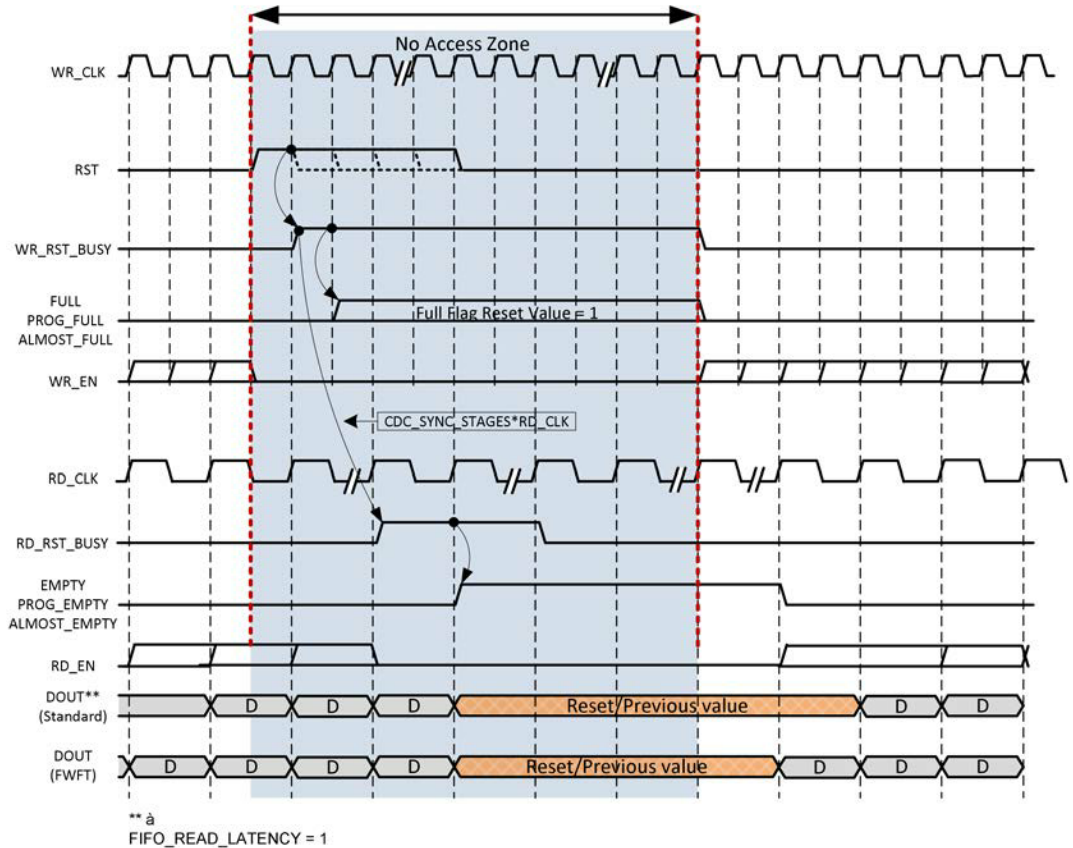

FIFO复位时序图:

本文只用到"fwft" - First - Word - Fall – Through read mode这种模式

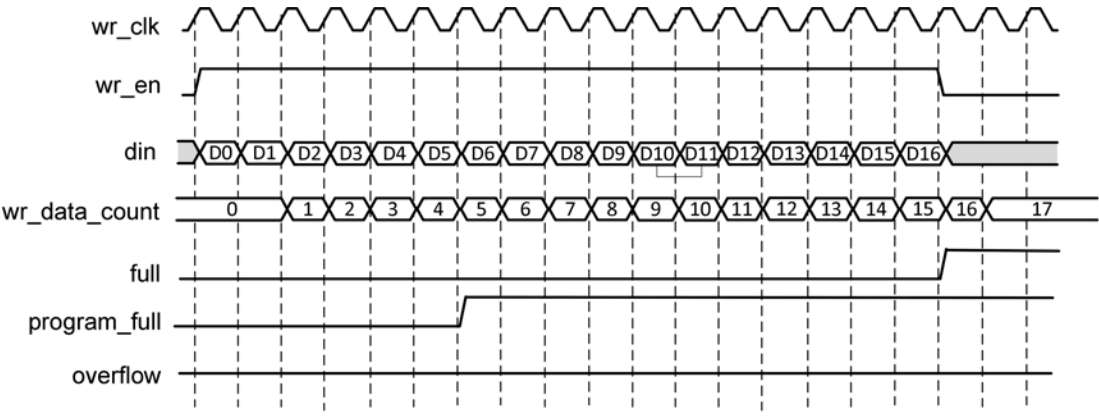

写时序图:READ_MODE=FWFT, FIFO_WRITE_DEPTH=16, PROG_FULL_THRESH=7

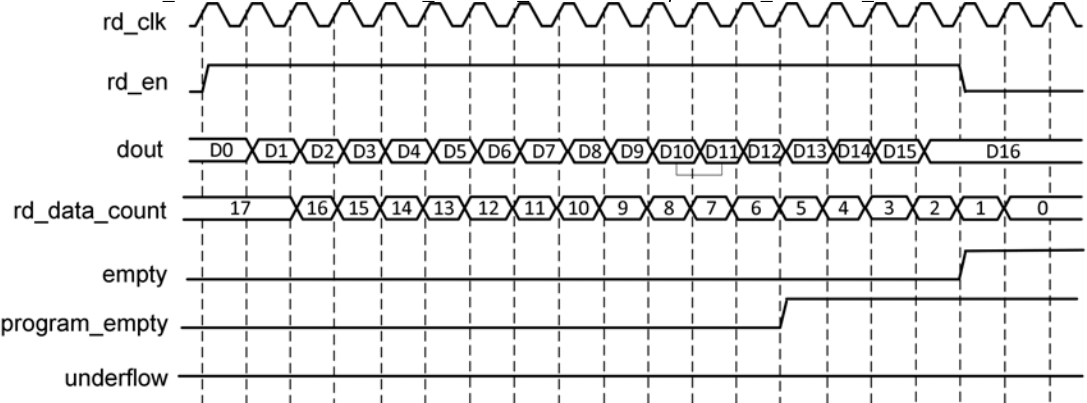

读时序图:READ_MODE=FWFT, FIFO_WRITE_DEPTH=16, PROG_EMPTY_THRESH=5

参数计算

function integer clog2;

input integer value;

begin

value = value-1;

for (clog2=0; value>0; clog2=clog2+1)

value = value>>1;

end

endfunction

localparam WFIFO_DEPTH = FIFO_DEPTH;

localparam W0_WR_DATA_COUNT_WIDTH = clog2(WFIFO_DEPTH)+1;

localparam W0_RD_DATA_COUNT_WIDTH = clog2(WFIFO_DEPTH/4)+1;

localparam RFIFO_DEPTH = FIFO_DEPTH/4;

localparam R0_WR_DATA_COUNT_WIDTH = clog2(FIFO_DEPTH/4)+1;

localparam R0_RD_DATA_COUNT_WIDTH = clog2(FIFO_DEPTH)+1;

文章转载自:米联客