本文转载自:半导体产业纵横微信公众号

AMD将推出smartNIC SoC,基于台积电7nm工艺。

AMD正迎来它的辉煌。在其发布的Q2季度财报中,AMD实现连续8个季度的增长,季度营收首次突破60亿美元。

AMD首席执行官苏姿丰表示:“AMD的高性能和自适应计算解决方案涵盖了从云计算,PC机到通信和智能终端等一系列应用场景。我们的解决方案正发挥越来越大的作用,不断塑造定义未来计算的近乎每一项服务和产品的能力。我们完成对赛灵思具有转型意义的收购扩展了领先的计算引擎产品组合,这为AMD提供了重要机会。随着我们的高性能和自适应产品在3000亿美元多样化市场中占据更大份额,我们将实现收入持续强劲增长,并向股东提供令人信服的回报。”

AMD将于2H22在台积电开始增加5nm订单

据业内消息人士称,AMD 有望在 2022 年下半年成为台积电 5nm 工艺平台的第二大客户,因为台积电将增加代工厂的 5nm 晶圆开工量。

AMD透露,它计划在 8 月 30 日举行一场直播活动,以揭示下一代基于 Zen 4 的 Ryzen 7000 CPU 细节。

消息人士称,即将推出的 AMD Zen 4 Ryzen 7000 系列桌面处理器将采用台积电的 5nm 工艺技术制造。消息人士称,该代工厂还签约为 Ryzen 7000 CPU 制造 6nm I/O 芯片。

AMD 还计划在 2022 年第四季度推出由台积电制造的 5nm EPYC Genoa 处理器。5nm EPYC(霄龙)服务器处理器系列将扩展到包括名为 Bergamo 的云优化处理器,预计将于 2023 年发布。

消息人士指出,AMD 正在开发另外两个基于 Zen 4 的 EPYC CPU 系列——针对技术计算和数据库进行优化的 EPYC Genoa-X,以及专注于电信的 EPYC Siena,两者都计划在 2023 年推出。这两个系列都将采用台积电的 5nm 工艺制造。

此外,AMD 将在明年上半年推出两款基于 Zen 4 的笔记本处理器系列。其中,即将推出的专为游戏笔记本电脑设计的 Phoenix APU 将基于台积电的 4nm 工艺节点构建。

AMD 继续使用台积电的 7nm 工艺节点制造代号为 Barcelo Refresh 的主流笔记本 APU。该代工厂还与制造 AMD 的 Mendocino APU 签订了合同,该 APU 专为 Chromebook 和 Windows 笔记本电脑等设备而设计,采用 6nm 工艺技术。

消息人士称,AMD 已经是台积电由 N6 组成的 7nm 工艺平台的最大客户。处理器供应商也是纯代工厂的前三大客户之一。

AMD拒绝就“市场猜测”置评。

AMD 将推出smartNIC SoC

AMD刚刚完成对 FPGA 供应商Xilinx(2022 年 2 月)和 DPU 供应商Pensando(2022 年 5 月)的收购,在 Hot Chips 上分享了 400 Gig Adaptive smartNIC SoC。在日益拥挤和模糊的 smartNIC/DPU 领域, smartNIC SoC是另一个竞争者。

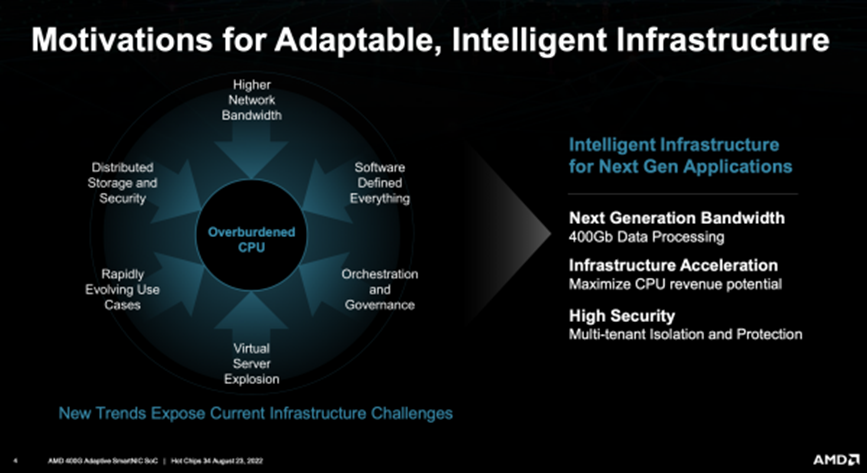

Jaidep Dastidar从Xilinx加入AMD,他提出了这些设备类型的动机,与Nvidia、英特尔和其他公司近年来的演示非常相似。主机CPU需要完成对于网络、存储、安全任务的处理。由于性能和带宽需求的增加、资源的分解以及软件定义一切的兴起,这使情况变得复杂。

Dastidar说:“转向智能网卡和DPU是源于业界向软件定义网络的发展。与此同时,随着速度和馈送的不断推进,网络带宽迅速增加了25、50、100、200 gig。虚拟化的水平也得到了扩展,其中虚拟机单个数字(VM)已经上升到10;而随着集成化的发展,CPU需要同时处理1000个虚拟实体。这些都导致了 CPU 负担过重的。因此,smartNIC 和 DPU 应运而生,因为它们有助于从主机CPU卸载这些工作负载,然后主机CPU可以重新专注于多租户云应用程序。”

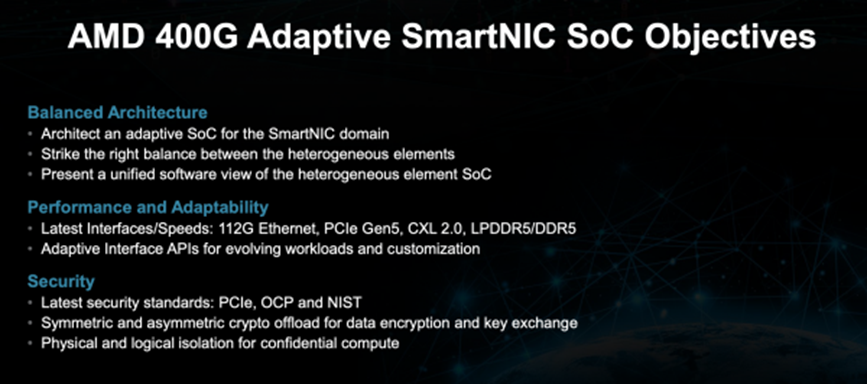

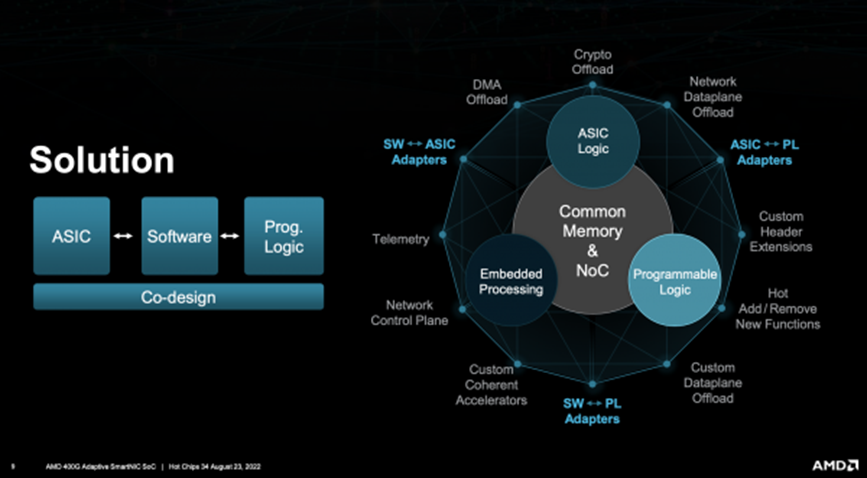

AMD正在将其 smartNIC 推广为一种灵活高效的SoC,它在适当的情况下利用固定逻辑 ASIC 技术、可编程逻辑 (FPGA) 和嵌入式处理器内核。当然,AMD 将自己定位为所有三种技术(ASIC、FPGA 和 CPU/内核)的强大供应商。

与其他公司一样,AMD 也在其系统中加入了先进的安全管理。用例可能非常多样,涵盖网络管理、存储管理和安全性,值得注意的是这其中对 CXL 2.0 的支持。

Dastidar说:“CXL 绝对是一项新兴技术。在这种设备中,既可以缓存主机内存,也可以拥有加速的设备附加内存。通过可编程逻辑,可以提供更多的灵活性。以便将smartNIC连接为传统的PCIe端点。”

Dastidar介绍了AMD的设计思路:AMD采用传统的硬件-软件协同设计范例,并将其扩展到硬件-软件-可编程逻辑协同设计。

从上图可以看到,在顶部,AMD将 ASIC 逻辑应用在它最擅长的地方:加密卸载、DMA 卸载,甚至是完整的网络数据平面卸载。然后,在顺时针方向上,AMD添加了 ASIC 到可编程逻辑适配器。继续顺时针方向,可以完全热添加或删除可编程逻辑中的新加速器功能。

当客户有需要与嵌入式处理子系统交互的可编程逻辑代理时,AMD有软件到可编程逻辑适配器接口,这样客户就可以创建与嵌入式处理器子系统进行交互的一致IO代理。

在遥测功能方面,Dastidar表示,虽然遥测数据是 SoC 范围的,但嵌入式处理子系统是“收集所有遥测数据、合成数据、然后将其上传到云管理平面的最佳位置。”SoC将采用台积电的7nm工艺制造,由功能块组成。虽然 Dastidar提供了大量有关功能和支持的特性的材料,但并未提及所需的编程工具是什么。

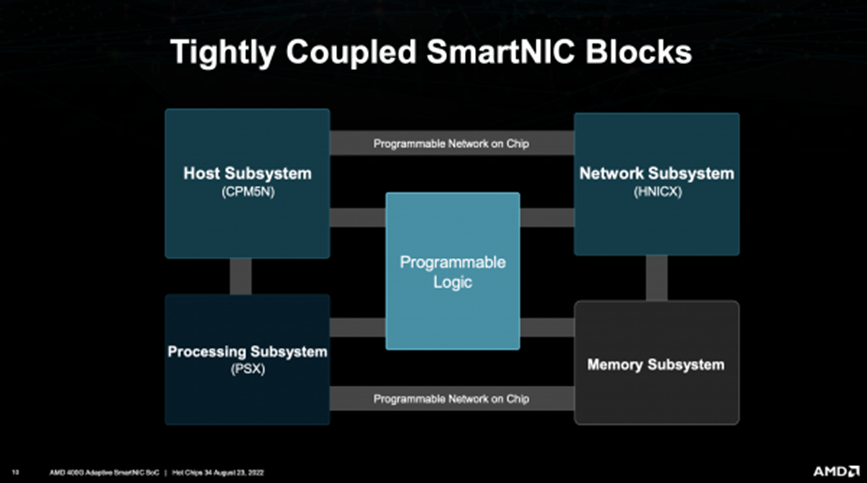

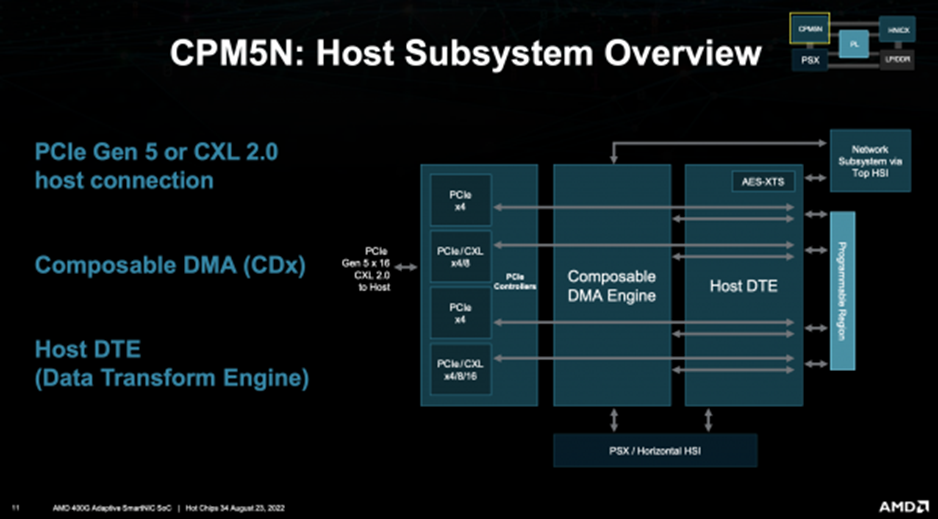

如上图所示,AMD 已将这些设计理念映射到自适应 SoC 内的特定子系统中。主机子系统包含主机连接和主机域加速。包含网络连接和网络域加速的网络子系统。处理子系统包含所有嵌入式处理核心。

Dastidar说:“虽然这里以视觉方式显示,但可编程逻辑元件和内存子系统可以视为具有芯片普遍连接和访问的芯片普遍资源。编程片上网络进一步增强了这种连接允许子系统到子系统的数据移动,任何子系统都可以访问一个公共内存位置。”

“主机连接可以是到smartNIC的单主机PCIe Gen 5 x16连接。或者,它可以一直连接到 smartNIC 的四主机 4x Gen 5 x4 连接。此外,控制器支持 CXL 2.0,它们可以支持第一类、第二类或第三类 CXL 设备。现在,PCIe 控制器已升级到最新的 PCIe ECN 安全标准。例如,PCIe CMA(组件测量和身份验证)、PCIe DOE(设备对象交换)、PCIe IDE(完整性和数据加密)和控制器还支持 TDX,它允许受信任的 VM 以机密计算方式与端点通信。”Dastidar说。

免责声明:本文转载于网络,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。