作者:Nathan Xu,AMD工程师

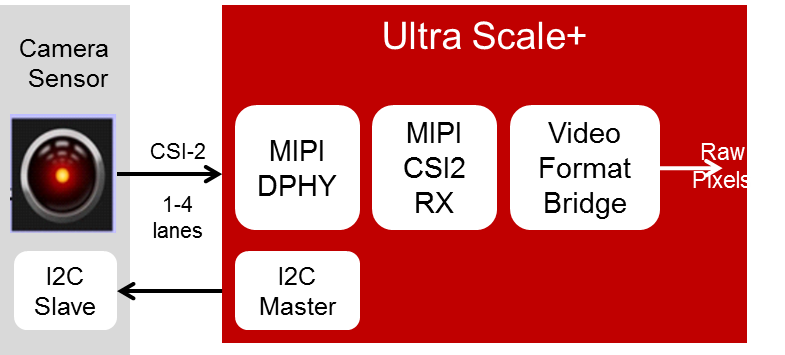

MIPI CSI-2 RX Subsystem IP实现MIPI CSI-2 v2.0协议以及底层的MIPI D-PHY v2.0协议, 这个IP是用来抓取来自MIPI CSI-2 摄像头的视频流, 把该视频流输出到AXI4-stream的接口, 进行下一步处理.

下面是MIPI CSI-2 RX Subsystem IP典型的应用示例:

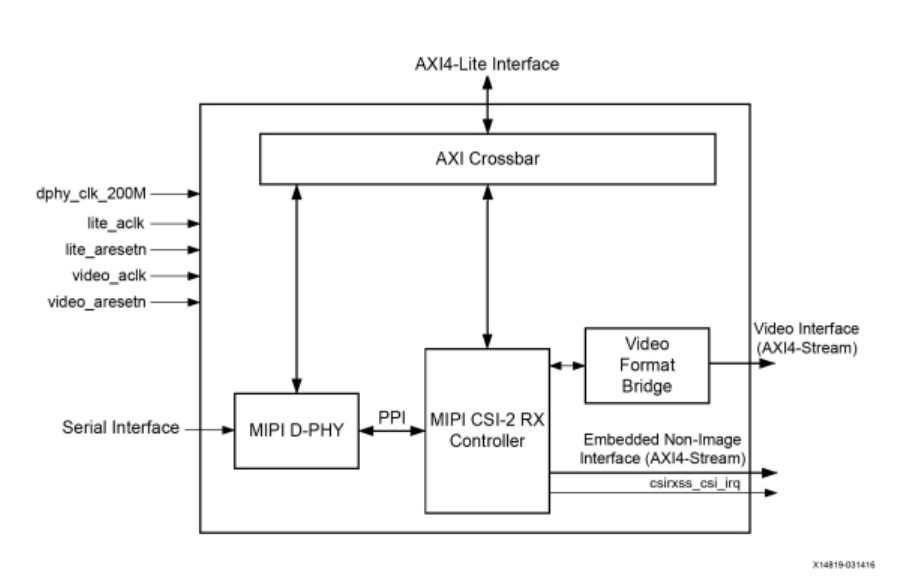

该IP是由MIPI D-PHY和MIPI CSI-2 controller, 以及VFB(Video format bridge)组成, 其中VFB可选. 下面是该IP的简略系统框图:

该IP支持7-series, UltraScale+, Zynq-7000, MPSoC, RFSoC, Versal. 对于UltraScale+, MPSoC, RFSoC, 在HP IO bank, 有可以支持MIPI_DPHY_DCI的I/O, 该I/O standard可以在同一个I/O上在low-power mode(0-1.2V single ended)和high speed mode(0.1-0.3v)之前切换。

对于Versal, 在其XPIO bank, 也有支持MIPI_DPHY_DCI I/O standard的I/O, 因此符合MIPI协议的sensor可以直接与FPGA的这些IO连接。

需要注意的是, 因为, MIPI_DPHY_DCI 无论对于input还是output, Vcco的要求都是1.2v, 见FPGA的手册, 如果sensor需要的电压是1.8v, 那么这时候, 对于那些控制信号, 因为有电压差异, 所以需要level shift。

下面是一个例子, sensor需要的VDDIO是1.8v(见sensor的手册), FPGA与sensor连接的简略框图, 左边是FPGA I/O bank, 右边是Sensor.x

对于7 series和zynq-7000的支持, 因为FPGA没有支持MIPI协议的I/O, 因此, 需要用到XAPP894实现PHY, 当然, 如果用户直接用MIPI CSI-2 RX Subsystem该IP, 因为该IP支持 7 series, 不需要考虑PHY实现。

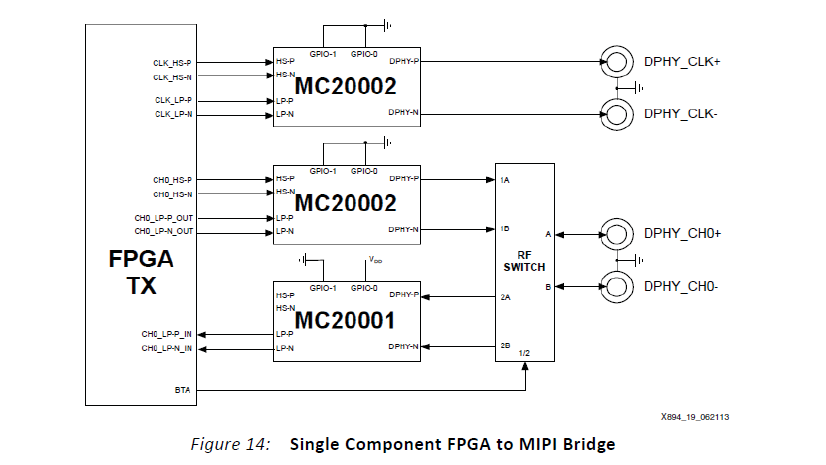

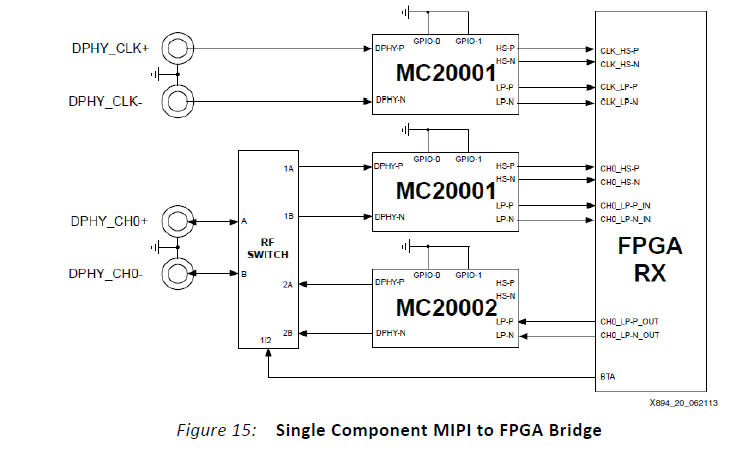

如果目标器件是Spartan, 该IP不支持. 那么用户需要用到XAPP894实现PHY, XAPP894提供的两种方式实现DPHY IO, Compatible Solution和Compliant Solution.

Compatible Solution:

Compliant Solution:

Compatible solution适用于不超过800Mbps的应用, 不管是哪种实现方式, 需要做board level SI simulation。

对于7series以及其他MIPI CSI-2 RX Subsystem支持的这些器件. 需要注意I/O pin以及bank的要求。

7 series:

Non-continuous IO usage is allowed for D-PHY TX and RX interfaces but not recommended.

Restrict the IO selection within the single IO bank.

Select SRCC/MRCC pins for D-PHY RX clock lane.

Ultrascale+:

RX clock lane pins must be DBC, QBC and GC_QBC pins.

Select the IO pins continuously without leaving any IO pairs in the middle of D-PHY interface.

D-PHY IP uses IO in Native mode. Using the left out IO’s in the nibble is not recommended, in case if its inevitable refer to “Mixing Native and Non-Native Mode I/O in a Nibble” section in UltraScale Architecture SelectIO Resources User Guide (UG571).

HSSIO internally uses few IO under certain IO selection scenarios for Strobe propagation and this can be avoided by selecting IO continuously. Pin(s) used for Strobe propagation will be DBC, QBC or GC_QBC and it will restrict you to implement the multiple D-PHY interfaces.

All the lanes of a particular MIPI D-PHY instance need to be in the same HP IO bank, which the Pin Assignment tab of XGUI automatically controls for UltraScale+ devices.

In case of multiple D-PHY instances sharing clocking resources, all such instances also need to be in the same HP IO bank.

Versal:

Select any XPIO Bank.

RX clock lane pins must be "XCC", "GC/XCC" pins.

Non-continuous IO usage is allowed for D-PHY TX and RX interfaces but not recommended.

While Selecting the data lane pins for RX it should follow the inter Nibble & inter byte

clocking.

评论

你好,文中提到对于7系列和Z7系列,不需要考虑PHY

你好,文中提到对于7系列和Z7系列,不需要考虑PHY IO的实现。事实上7和Z7的LVDS的电气层不兼容MIPI的HS,在RX功能下,需要用到XAPP894中的方案。

请确认下,谢谢