作者:陈晨,文章来源:亚科鸿禹

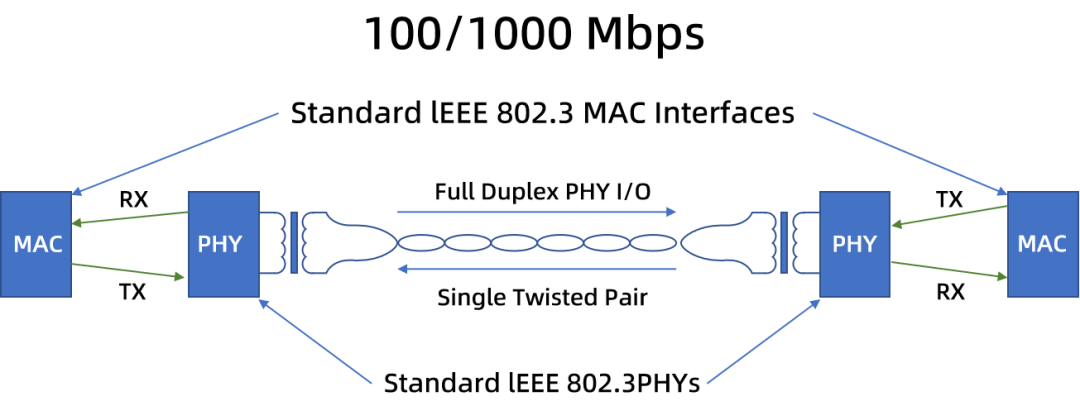

以太网协议是现代通信技术中常见的通信协议,计算机与互联网实现信息交流共享必备通信接口之一,以太网通信协议由IEEE和ISO于1985年共同推出,也被称为IEEE 802.3标准,标准规定包括物理层的连线、电子信号和介质访问层协议等。以太网数据通信具有价格低廉、稳定可靠、传输速度快、传输距离远等特点,利用以太网设备可以通过TCP/IP协议进行数据的传输,无需转换传输协议。作为当今最为通用的通信协议标准之一,适用于各种网络通信场景下的应用连接。人工智能、车载通信、多媒体等SoC芯片大多都会将以太网接口作为数据通信必不可少的通信方式。

随着应用需求的增加和科技的发展,以太网也由最开始的2.94Mbit/s逐渐发展至如今的标准以太网(10Mbit/s)、快速以太网(100Mbit/s)、千兆以太网(1000Mbit/s)、甚至速率更高的以太网(10Gbit/s)。其中,千兆以太网凭借其低成本,强抗干扰性,高通信速率、高性能等特点脱颖而出,逐渐发展成为主流网络技术。

千兆以太网技术是建立在基础以太网标准之上的技术,兼容标准以太网与快速以太网,并利用了原以太网标准所规定的全部技术规范,包括相同的帧格式、帧结构、网络协议、全/半双工工作方式、流控模式以及布线系统,不改变传统以太网的桌面应用、操作系统。

亚科鸿禹VeriTiger®系列原型验证平台千兆以太网解决方案

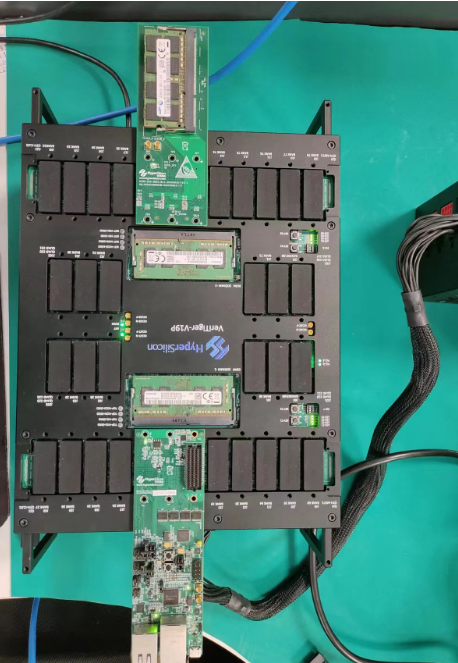

VeriTiger®系列原型验证平台千兆以太网解决方案的硬件环境由VeriTiger®原型验证母板(如图1所示)、配套以太网相关功能子卡(如图2所示)、数据传输连接线组成,通过子卡提供真实的外设来构建设计原型,进行功能验证并提供深度调试。

为满足不同芯片设计的数据通信场景,缩短原型验证平台的搭建时间,实现快速数据传输,提升验证效率,千兆以太网解决方案利用Xilinx提供的AXI_1G/2.5G Ethernet SubSystem IP核来实现MAC功能,替代MAC接口,大大简化硬件电路设计,是适合用于进行验证数据通信功能的解决方案。亚科鸿禹VeriTiger®原型验证系统为各类SoC设计的数据通信提供高性能千兆以太网解决方案。

“千兆以太网” 解决方案:

通过亚科鸿禹自研的HSPI2-UTEH、HYDX-DDR3子卡完成原型验证环境创建,启动工程验证。HSPI2-UTEH为以太网子卡,外置KSZ8091RNB,DP83867IR两款PHY芯片,可支持MII、GMII、RGMII、RMII模式下的以太网通信。子卡的GMII网口为千兆MII接口,采用8位数据接口,工作时钟为125MHz,传输速率可达到1000Mbps,同时兼容MII所规定的10/100 Mbps工作方式。HYDX-DDR3为内存子卡,支持64BIT、32BIT。该方案通过调用Xilinx提供的AXI_1G/2.5G Ethernet SubSystem IP,包含IEEE802.3标准中描述的功能。

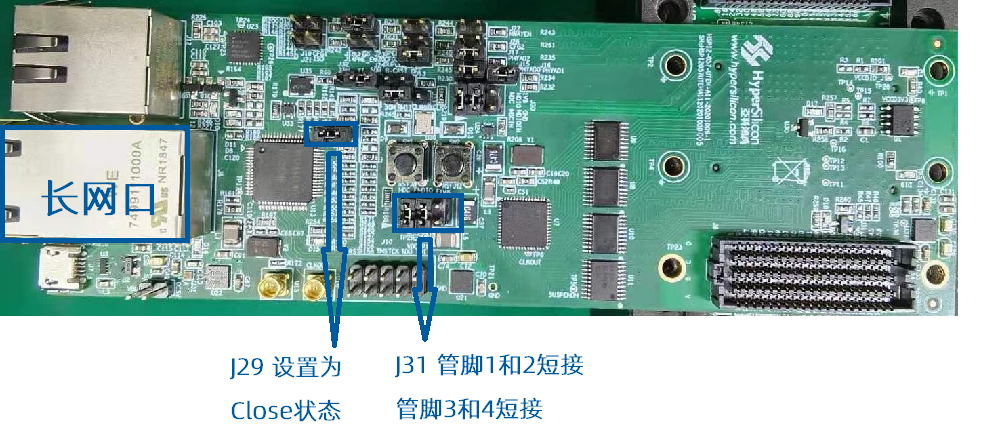

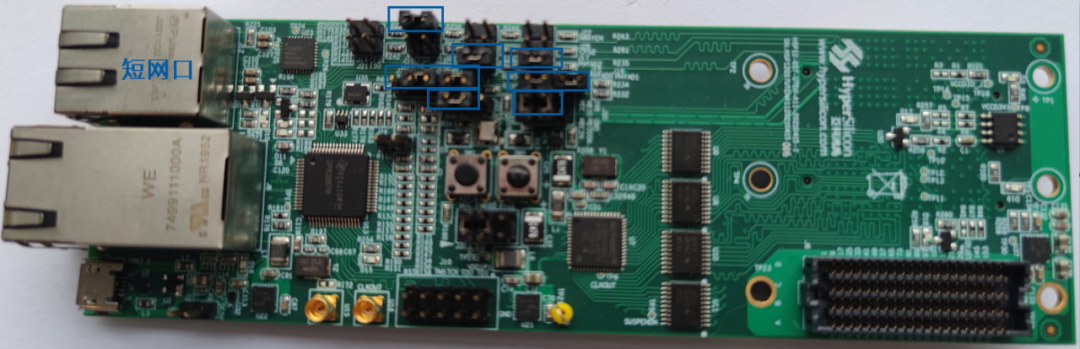

硬件连接时,需插入HSPI2-UTEH子卡至原型验证系统的插座处,并用网线连接以太网子卡的长网口和PC端网口,设置J29为Close状态,短接J31的1、2管脚,3、4管脚,即可实现GMII模式下的数据通信。(如图3所示)

图 3 GMII模式的子卡连接图

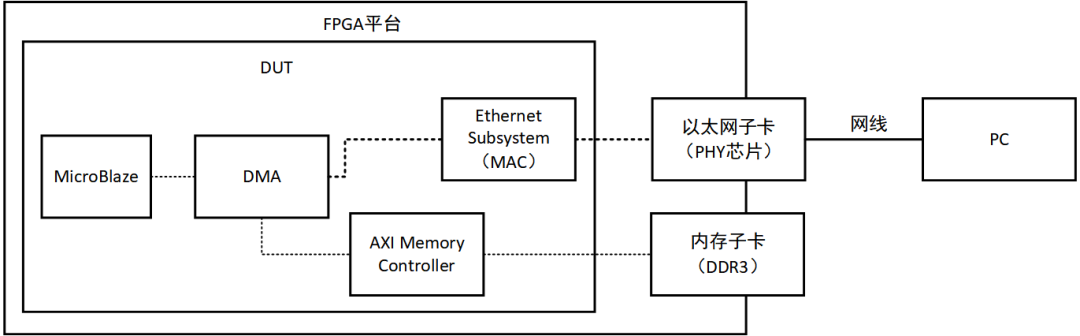

工程整体结构如图4所示:

图4 工程整体结构图

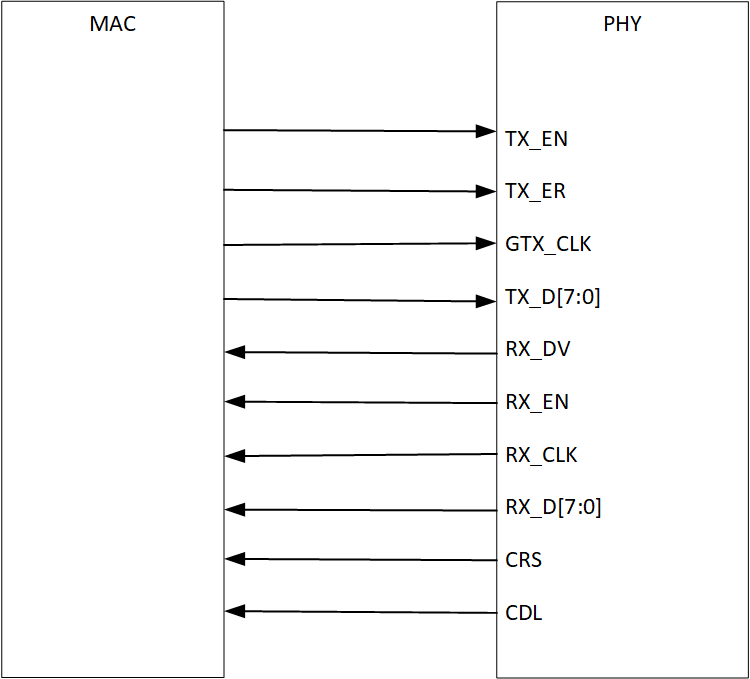

GMII模式下,PHY芯片侧的接口信号如图5所示:

图5 GMII模式下接口信号图

1. TX_EN:发送数据使能信号,高电平有效;

2. TX_ER:发送错误信号,高电平有效;

3. GTX_CLK:发送时钟信号,频率为 125MHz;

4. TX_D:发送数据8Bit,FPGA通过该数据线将需要发送的数据发送给PHY芯片;

5. RX_DV:接收使能信号,高电平有效;

6. RX_CLK:接收时钟信号,125MHz;

7. RX_ER:接收错误信号,高电平有效;

8. RX_D:接收数据8Bit,8位带宽,FPGA通过该数据线从PHY芯片接收数据;

发送或接收数据时,采用8位数据接口,工作时钟为125MHz,传输速率可达到1000Mbps。解决方案中,PC端发送数据时,数据先传输至PHY芯片,此时,Ethernet Subsystem接收此信息,向MicroBlaze发送中断,随后,MicroBlaze控制DMA将数据搬运至DDR中。PC端接收数据时,也由MicroBlaze控制DMA搬运数据至PC端。

方案适用于验证:

数据高传输速率的SoC设计。

图 6 VeriTiger®原型验证千兆以太网解决方案硬件环境

亚科鸿禹除千兆以太网解决方案外,也支持标准以太网和快速以太网解决方案,可实现RGMII模式、MII模式以及GMII模式下的数据通信。

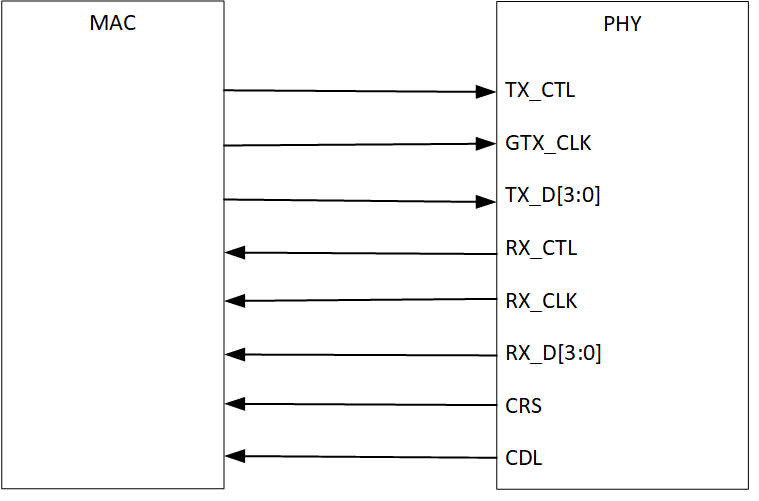

RGMII模式下

设置J29插座为OPEN状态,其余硬件连接与GMII模式保持一致。RGMII模式下,发送或接收数据时,采用4位数据带宽,比较大的区别是,将RX_DV和RX_ER信号集成到了RX_CTL上,时钟上升沿采集信号RX_DV,下降沿采集信号RX_DV^RX_ER(异或);将TX_EN和TX_ER信号集成到TX_CTL上,时钟上升沿采集信号TX_EN,下降沿采集TX_EN^TX_ER(异或),如图7所示。由于下降沿采集的是异或结果,所以一般情况下,RX_CTL信号为高电平有效,为保证正确采集数据,PHY芯片需要将接收到的GTX_CLK信号延迟约1/4个时钟周期。

图7 RGMII模式下接口信号图

MII模式下

硬件连接与GMII模式无区别,但发送或接收数据时,PHY芯片接口处RX_D与TX_D采用4位数据接口。工作时钟为25MHz,传输速率可达100Mbps,工作时钟为2.5MHz,传输速率可达10Mbs。并且,GTX_CLK不由MAC侧产生,而是由PHY芯片侧产生,如图8所示。

图8 MII模式下接口信号图

RMII模式下

硬件连接与GMII模式区别较大,需将网线端插至短网口,并插上跳线帽,如图9所示。

图 9 RMII模式下的子卡连接图

发送或接收数据时,采用2位数据带宽,参考时钟通常由外部晶振提供给MAC侧或者PHY芯片,CRS和RX_DV复用一个端口,如图10所示。

图10 RMII模式下接口信号图

随着需求的多样化,千兆以太网的应用随之多样化,使用以太网解决方案,有助于用户快速搭建环境,进行管脚约束,完成芯片设计验证。

亚科鸿禹VeriTiger®原型验证系统可实现众多协议验证的解决方案,配合自研软件ProtoWizard®可以对FPGA系统进行时钟电压的配置,bit文件的烧录以及统一的子卡管理,从而提升FPGA原型验证工作效率。

欢迎联系我司销售部门获取产品资料、对接项目需求:hypersilicon@hypersilicon.com 。

关于亚科鸿禹

无锡亚科鸿禹电子有限公司,成熟的一站式SoC/ASIC仿真验证产品及解决方案供应商,国内最早从事FPGA原型验证和硬件仿真加速器工具的研发与应用团队之一。率先推出国内首款桌面级硬件仿真加速器产品,实现该领域技术破冰。在华大九天的全面支持下,着力部署 “FPGA 原型验证矩阵”、“企业级硬件仿真加速器”、“ESL高阶设计语言编译和仿真工具”、“逻辑综合器”等多款数字前端核心 EDA 工具的研发与市场推广,致力于成为“中国领先的数字前端 EDA 工具供应商”,助力国产数字 EDA 全流程自主可控。

公司总部位于江苏无锡,在北京、深圳、合肥设有3个研发中心,上海、西安、成都设有办事处,拥有近两百人的人才团队,由具有20余年国际仿真验证从业背景的领域专家领衔,核心成员平均超过15年国内外知名EDA企业从业经验。公司与清华大学、合肥工业大学、江南大学等知名高校在EDA技术研发和人才培养方面保持长期产学研合作,共同推动国产EDA产业进程,助力中国半导体产业发展。公司的VeriTiger®系列原型验证产品和HyperSemu®硬件仿真加速器广泛服务于国内外知名集成电路设计企业、院校和研究所,应用于5G、人工智能、自动驾驶、AIoT、存储等前沿领域,全球累计用户超500家。