来源:内容由半导体行业观察(ID:icbank)编译自HPCwire,谢谢。

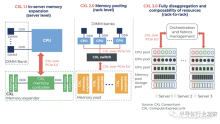

几年后,服务器看起来可能会不一样,因为内存、存储和加速器会移动到单独的机箱中。称为 CXL 的互连使这成为可能。

该技术的升级版规范 3.1 版于本周发布。增量更新提供了更快、更安全的计算环境和更强大的技术基础,将数据中心转变为巨型服务器。

新规格将支持DDR6内存,目前该内存仍在开发中。DDR 标准制定组织 JEDEC 尚未广泛讨论 DDR6。

Intel 和 AMD 服务器芯片目前支持 DDR5,但尚未引导芯片组支持 DDR6。大多数硬件和云提供商都支持 CXL。

CXL 3.1 是对一年多前推出的 CXL 3.0 的增量改进。CXL 协议是系统中芯片、内存和存储之间的通信链路。

CXL 3.0 规范基于 PCIe 6.0,数据传输速度高达每秒 64 GB。它比其前身 CXL 2.0 快两倍,CXL 2.0 基于 PCIe 5.0,并且正在进入服务器系统。

随着人工智能等技术的普及,CXL 已成为芯片组的重要组成部分。机器学习应用程序需要大量内存和带宽。CXL 允许跨服务器共享存储和内存。

CXL 3.1 协议可以开放更多点对点通信,将内存和存储分解到单独的盒子中。通过传统网络和互连技术进行分解已经讨论了十年,但 CXL 提供了提供广泛的计算资源所需的可扩展性。

其一,CXL 3.1 规范提供了支持新型内存的机会,并且还可以更有效地将数据重新路由到内存和加速器。

一项重要的进步涉及将结构上的内存资源集中在一个全局地址下。该功能称为全局集成内存,对于在内存和其他资源之间建立更快的连接非常重要。

加速器还能够直接与内存资源通信。基于端口的路由的新功能有助于更快地访问内存资源。

CXL 3.1 还提供了在受保护环境中执行数据的挂钩。该技术的推出是为了支持机密计算,该技术已在英特尔的 Sapphire Rapids 中采用 TDX 指令,并在 AMD 的芯片中作为 SNP-SEV 功能引入。

新规范定义了一个安全协议,当数据在内存、处理器和存储之间移动时,该协议扩展了安全环境。

该协议将检测需要对连接进行身份验证才能打开硬件库来访问代码或信息的环境。该信息可能位于处理器、内存或存储设备上。英特尔、微软和其他公司有不同类型的认证方法来验证尝试在安全环境中访问数据的连接。

CXL 联盟宣布发布 Compute Express Link 3.1 规范

CXL 联盟是一个开发和推广开放式相干互连的行业标准机构,今天宣布发布 Compute Express Link™ (CXL™) 3.1 规范,该规范改进了结构可管理性CXL 超越机架并启用分解系统。CXL 3.1 规范以之前的迭代为基础,旨在优化资源利用率、根据需要创建可信计算环境、扩展内存共享和池以避免内存滞留,并促进加速器之间的内存共享。

CXL 联盟主席 Larrie Carr 表示:“CXL 3.1 规范纳入了 CXL 社区要求的新功能,以创建分类系统并跟上高性能计算工作负载的要求。” “在我们成员的支持下,我们继续开发和推广 CXL 技术,以实现异构内存和计算解决方案的可互操作生态系统。”

CXL 3.1 规范功能的亮点:

原文链接:https://www.design-reuse.com/news/55218/cxl-consortium-compute-express-l...