文章来源:本文由半导体产业纵横(ID:ICVIEWS)编译自tomshardware

AMD 在加利福尼亚州圣何塞举行的 Advancing AI 活动期间推出了 Instinct MI300X AI 加速器和 Instinct MI300A(全球首款数据中心 APU),希望可以充分利用蓬勃发展的生成式 AI 和 HPC 市场。AMD 使用最先进生产技术打造了 MI300 系列,并采用“3.5D”封装等新技术来生产两款芯片,据称这两款产品在各种人工智能工作负载中提供了超越英伟达的性能。AMD 并未透露其新芯片的定价,但这些产品目前正在向众多 OEM 合作伙伴发货。

Instinct MI300 是一种改变游戏规则的设计:数据中心 APU 混合了总共 13 个小芯片,其中许多是 3D 堆叠的,以创建一个具有 24 个 Zen 4 CPU 内核并融合了 CDNA 3 图形引擎和 8 个堆栈的芯片HBM3。总体而言,该芯片拥有 1530 亿个晶体管,是 AMD 迄今为止制造的最大芯片。AMD 声称该芯片在某些工作负载中的性能比英伟达H100 GPU 高出 4 倍,并宣称其每瓦性能是其两倍。

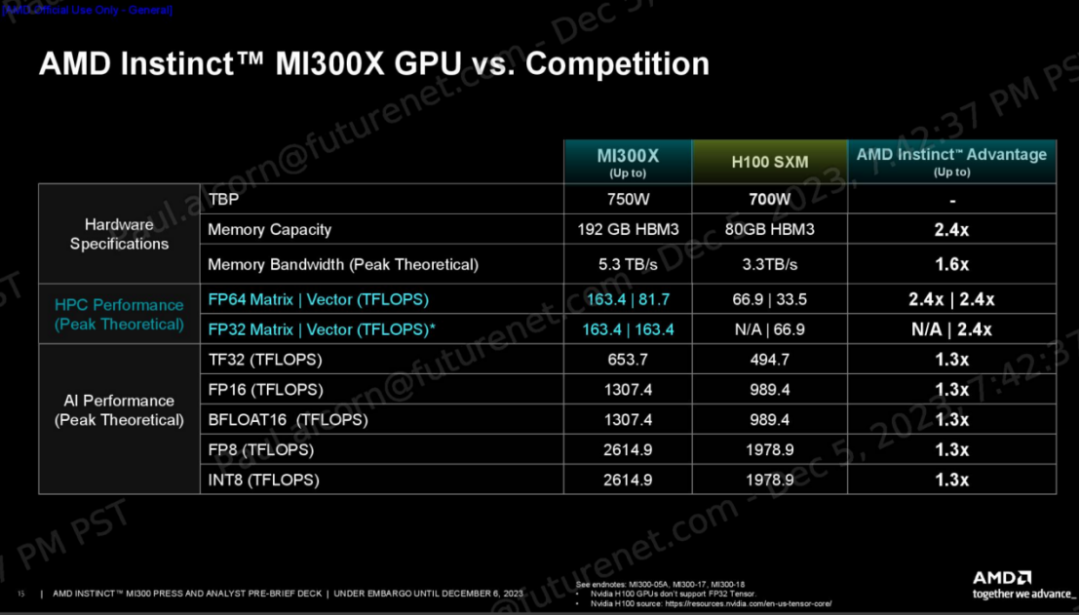

AMD 表示,其 Instinct MI300X GPU 在人工智能推理工作负载中的性能比英伟达H100 高出 1.6 倍,并在训练工作中提供类似的性能,从而为业界提供了急需的英伟达GPU 的高性能替代品。此外,这些加速器的 HBM3 内存容量是英伟达GPU 的两倍以上(每个 192 GB 令人难以置信),使其 MI300X 平台能够支持每个系统两倍以上的 LLM 数量,并运行比英伟达H100 HGX 更大的模型。

AMD Instinct MI300X

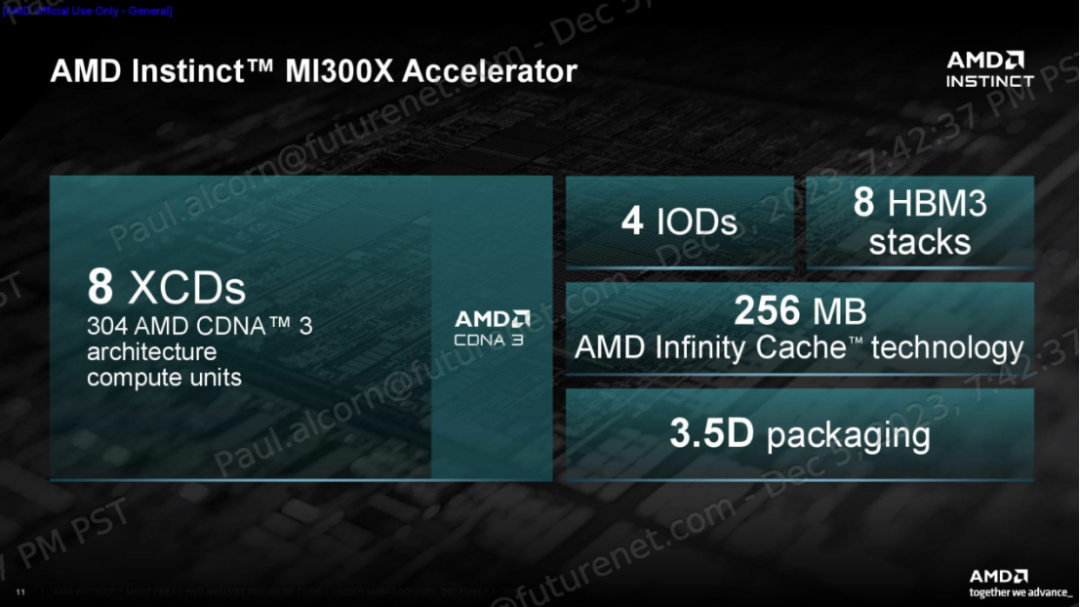

MI300X 代表了 AMD 基于小芯片的设计方法的顶峰,将八个 12Hi 堆栈的 HBM3 内存与八个 3D 堆栈的 5nm CDNA 3 GPU 小芯片(称为 XCD)融合在四个底层 6nm I/O 芯片上,这些芯片使用 AMD 现已成熟的技术进行连接混合键合技术。

来源:AMD

来源:AMD

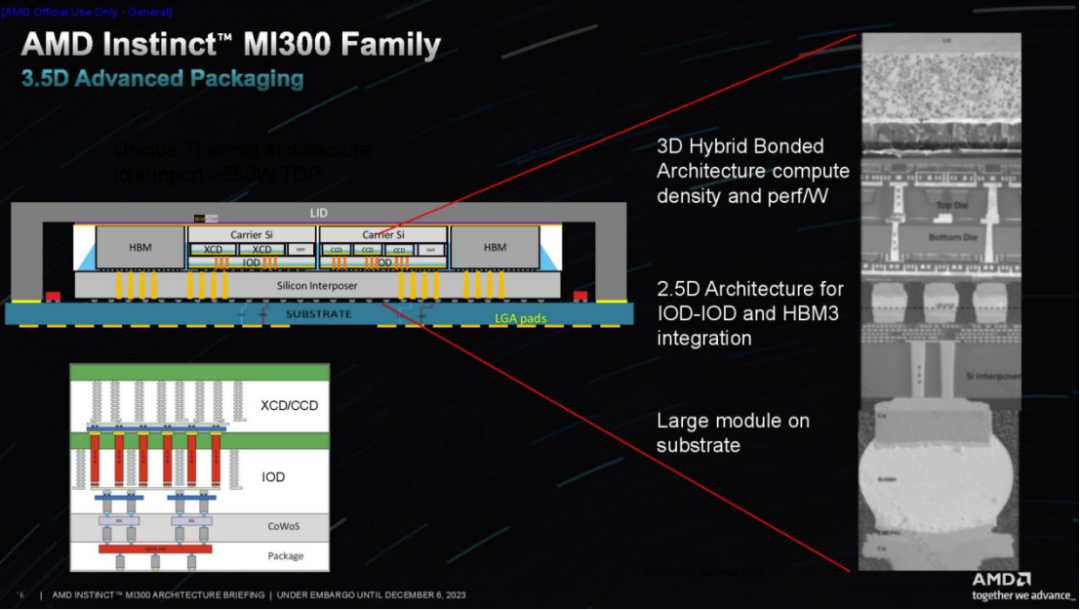

其结果是一个 750W 加速器,拥有 304 个计算单元、192GB HBM3 容量和 5.3 TB/s 带宽。该加速器还具有 256MB Infinity Cache,用作共享 L3 缓存层,以促进小芯片之间的通信。AMD 将其将小芯片绑定在一起的封装技术称为“3.5D”,表示 3D 堆叠 GPU 和 I/O 芯片通过混合键合融合在一起,并与模块其余部分的标准 2.5D 封装(水平连接)相结合。我们将更深入地研究下面的架构组件。

MI300X 加速器设计为在 AMD 的生成式 AI 平台中以八组为一组工作,通过 Infinity Fabric 互连的 GPU 之间的吞吐量为 896 GB/s。该系统拥有 1.5TB 的 HBM3 内存总量,可提供高达 10.4 Petaflops 的性能 (BF16/FP16)。该系统基于开放计算项目 (OCP) 通用基板 (UBB) 设计标准构建,从而简化了采用过程,特别是对于超大规模企业。

与英伟达的 H100 HGX 平台 (BF16/FP16) 相比,AMD 的 MI300X 平台的内存容量增加了 2.4 倍,计算能力据称提高了 1.3 倍,同时保持了相当的聚合双向和单节点环形带宽。AMD 为 MI300X 平台配备了 400GbE 网络并支持多种网卡,而英伟达则倾向于使用自己收购 Mellanox 后的网络产品。

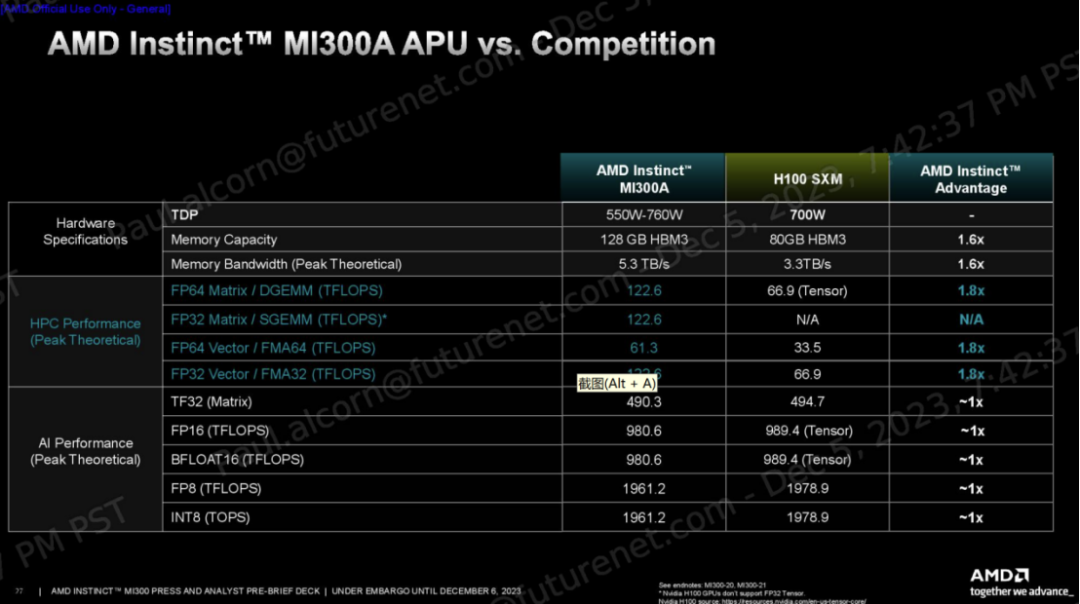

一如既往,我们应该谨慎对待供应商基准。AMD 分享了一系列性能指标,显示其针对 HPC 工作负载的 FP64 和 FP32 向量矩阵峰值理论吞吐量高达 H100 的 2.4 倍,TF32、FP16、BF16、FP8 和 INT8 峰值理论吞吐量高达 1.3 倍对于 AI 工作负载,所有预测都没有稀疏性(不过 MI300X 确实支持稀疏性)。

MI300X 的大内存容量和带宽非常适合推理。AMD 使用 1760 亿参数的 Flash Attention 2 模型声称在吞吐量方面比英伟达H100 具有 1.6 倍的性能优势,并使用 700 亿参数的 Llama 2 模型来强调 1.4 倍的聊天延迟优势(从2K 序列长度/128 个令牌工作负载的开始到结束)。

AMD 的 MI300X 平台在 300 亿参数 MPT 训练工作负载中提供的性能与 H100 HGX 系统大致相同,但需要注意的是,此测试并不是加速器的一对一比较。相反,该测试让八个加速器组相互竞争,因此平台级功能更像是一个限制因素。无论哪种情况,这种性能都会很快引起受到英伟达GPU 短缺困扰的行业的兴趣。

说到平台能力,AMD还声称MI300X平台的内存容量优势可以容纳比H100系统多两倍的30B参数训练模型和70B参数推理模型。此外,MI300X平台最多可支持70B训练和290B参数推理模型,这两个模型都是H100 HGX支持的模型的两倍。

当然,英伟达即将推出的 H200 GPU在内存容量和带宽方面将更具竞争力,而计算性能将与现有的 H100 保持相似。英伟达要到明年才会开始发货 H200,因此与 MI300X 的竞争仍然存在。

AMD 本能 MI300A

AMD Instinct MI300A 是全球首款数据中心 APU,这意味着它将 CPU 和 GPU 结合在同一个封装中。它将直接与英伟达的 Grace Hopper Superchips竞争,后者的 CPU 和 GPU 位于单独的芯片封装中,可以协同工作。MI300A 已经在El Capitan 超级计算机中取得了显著的胜利,AMD 已经将该芯片运送给其合作伙伴。

MI300A 使用与 MI300X 相同的基本设计和方法,但替换为三个 5nm 核心计算芯片 (CCD),每个核心具有八个 Zen 4 CPU 核心,与 EPYC 和 Ryzen 处理器上的相同,从而取代了两个 XCD GPU 小芯片。

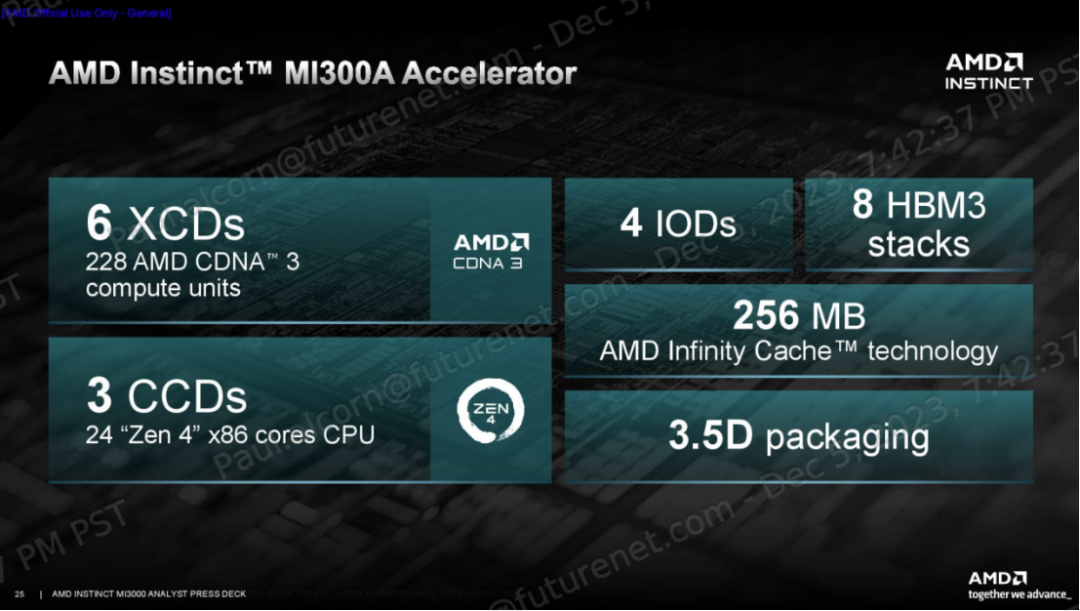

这使得 MI300A 配备了 24 个线程 CPU 内核和分布在 6 个 XCD GPU 小芯片上的 228 个 CDNA 3 计算单元。与 MI300X 一样,所有计算小芯片均采用混合键合方式与四个底层 I/O 芯片 (IOD) 进行 3D 堆叠,以实现远超标准芯片封装技术所能实现的带宽、延迟和能源效率。

AMD 通过使用 8 个 8Hi HBM3 堆栈(而不是 MI300X 中使用的 8 个 12Hi 堆栈)来削减内存容量,从而将容量从 192GB 削减至 128GB。然而,内存带宽仍为 5.3 TB/s。AMD表示,减少内存容量的决定并不是由于功率或热量限制;相反,它针对目标 HPC 和 AI 工作负载定制芯片。无论如何,128GB 的容量和 5.3 TB/s 的吞吐量仍然是英伟达H100 SXM GPU 提供的 1.6 倍。

MI300A 的默认 TDP 为 350W,但可配置为最高 760W。AMD 根据使用情况在芯片的 CPU 和 GPU 部分之间动态分配功率,从而优化性能和效率。AMD 尽可能巧妙地重复利用:MI300A 插入 AMD 的标准 LGA6096 插槽,就像 EPYC Genoa 处理器一样,但该插槽的 SH5 版本与使用 SP5 的 AMD EPYC 处理器在电气上不兼容。

内存空间在 CPU 和 GPU 之间共享,从而消除了数据传输。该技术通过消除单元之间的数据传输来提高性能和能源效率,同时还减少编码负担。与 MI300X 一样,该芯片具有中央 256MB 无限缓存,有助于确保流经芯片的数据的带宽和延迟。

AMD 声称 FP64 Matrix/DGEMM 和 FP64/FP32 Vector TFLOPS 比 H100 高出 1.8 倍。该公司还声称 TF32、FP16、BF16、FP8 和 INT8 与 H100 相同。

AMD 声称,在 OpenFOAM HPC测试中,其 MI300A 比英伟达的 H100 快 4 倍,但这种比较并不理想:H100 是 GPU,而 MI300A 中的混合 CPU 和 GPU 计算在这种内存密集型中提供了固有的优势,有时是串行工作负载,通过其共享内存寻址空间。与英伟达Grace Hopper GH200 Superchip 进行比较会更好,后者也将 CPU 和 GPU 以紧密耦合的方式结合在一起,但 AMD 表示,它找不到任何公开列出的英伟达GH200 的 OpenFOAM 结果。

AMD 确实提供了与英伟达GH200 的每瓦性能比较数据,以强调 2 倍的优势,这些结果基于有关 H200 的公开信息。AMD 还强调了与 H100 在 Mini-Nbody、HPCG 和 Gromacs 基准测试中的比较,声称分别领先 1.2 倍、1.1 倍和 1.1 倍。同样,对于这组基准测试,与 GH200 进行比较会更理想。

AMD Instinct MI300X 和 MI300A 架构

我们介绍了上面设计的基础知识,这些细节为理解下面的部分提供了重要的视角。

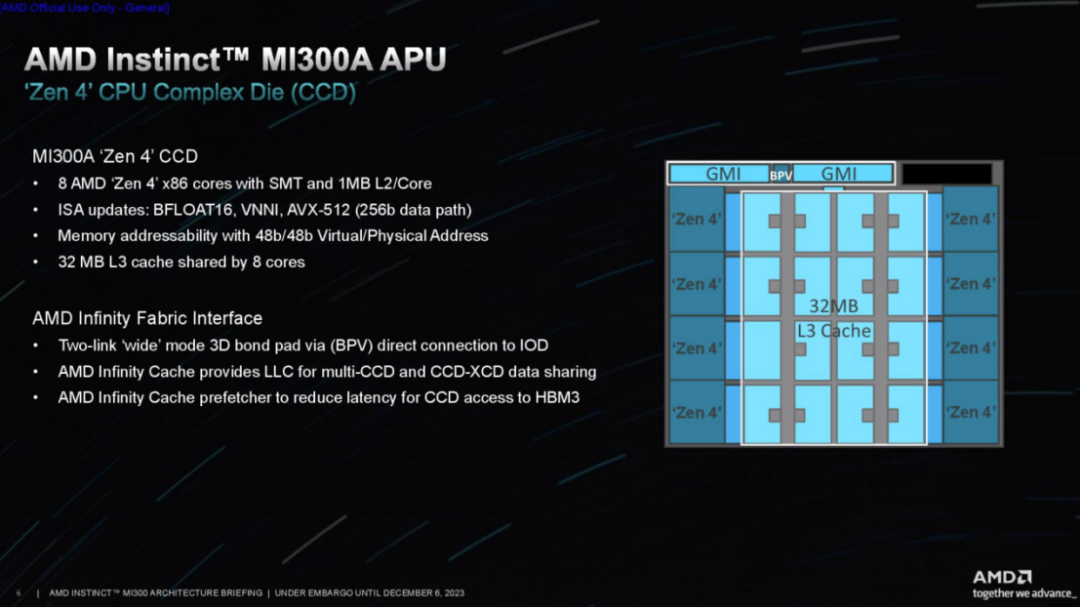

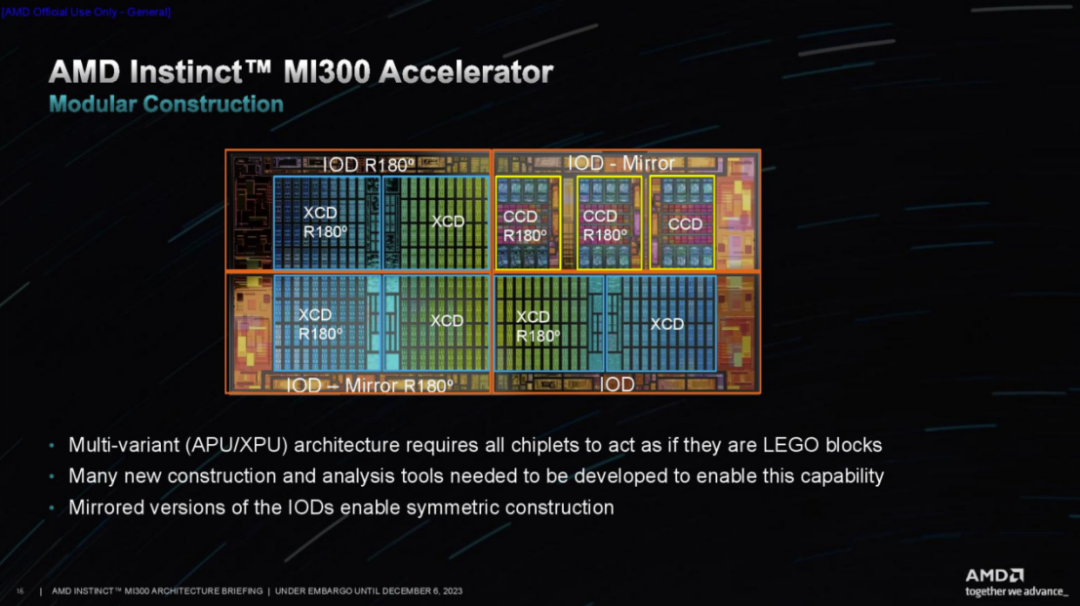

AMD 利用台积电的 3D 混合键合 SoIC(集成电路上硅)技术,在四个底层 I/O 芯片之上对各种计算元件进行 3D 堆叠,无论是 CPU CCD(核心计算芯片)还是 GPU XCD。每个 I/O 芯片可以容纳两个 XCD 或三个 CCD。每个 CCD 与现有 EPYC 芯片中使用的 CCD 相同,每个 CCD 拥有八个超线程 Zen 4 核心。MI300A 使用了其中的三个 CCD 和六个 XCD,而 MI300X 使用了八个 XCD。

HBM 堆栈使用采用 2.5D 封装技术的标准中介层进行连接。AMD 将 2.5D 和 3D 封装技术相结合,使该公司创造了“3.5D”封装的绰号。每个 I/O 芯片都包含一个 32 通道 HBM3 内存控制器,用于托管 8 个 HBM 堆栈中的两个,从而为该设备提供了总共 128 个 16 位内存通道。MI300X 采用 12Hi HBM3 堆栈,容量为 192GB,而 MI300A 使用 8Hi 堆栈,容量为 128GB。

AMD 还增加了 256MB 的无限缓存总容量,分布在所有四个 I/O 芯片上,通过预取器缓存数据流量,从而提高命中率和电源效率,同时减少总线延迟。这为 CPU 增加了新级别的缓存(概念上是共享 L4),同时为 GPU 提供共享 L3 缓存。Infinity Fabric NoC(片上网络)被称为 AMD Infinity Fabric AP(高级封装)互连,用于连接 HBM、I/O 子系统和计算。

该芯片总共具有 128 个 PCIe 5.0 连接通道,分布在四个 I/O 芯片上。它们被分为两组:一组是四个 x16 PCIe 5.0 + 第四代 Infinity Fabric 链路的组合,而另一组则有四个专门用于 Infinity Fabric 的 x16 链路。后者仅用于将 MI300 相互连接(跨套接字流量)。

MI300X 纯粹用作端点设备,它连接到外部 CPU。相比之下,MI300A 由于其本机 CPU 内核而采用自托管,因此 PCIe 根复合体必须充当主机。为了适应这两种场景,AMD 定制的 MI300 I/O 芯片支持来自同一 PCIe 5.0 根复合体的两种模式,该根复合体是该公司 IP 产品组合的新成员。

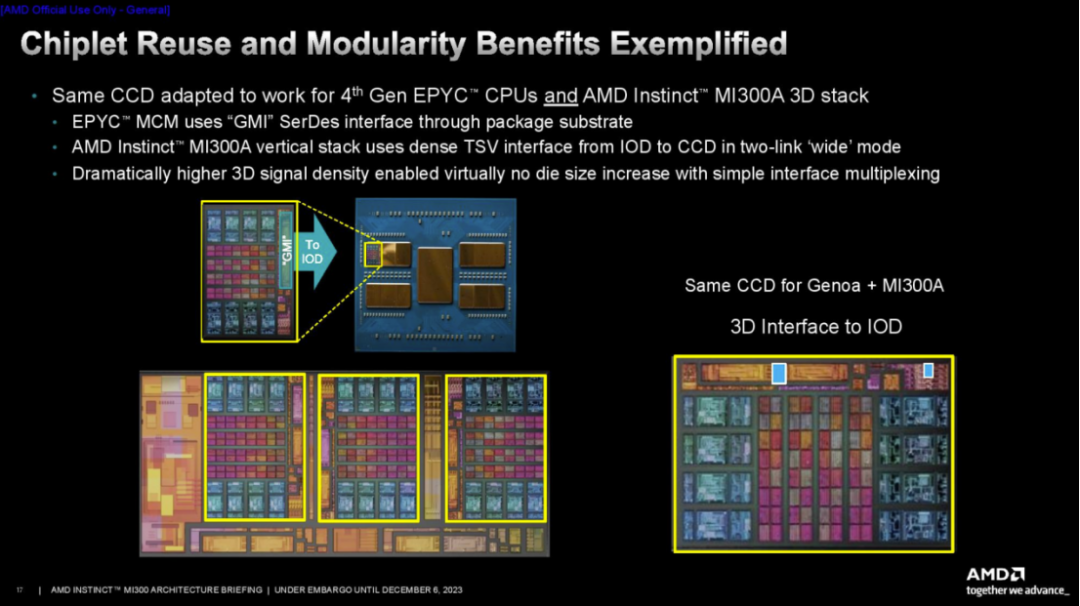

AMD 的 CPU CCD 通过 3D 混合键合到底层 I/O 芯片,需要新的接口。虽然这与 EPYC 服务器处理器中的 CCD 相同,但这些芯片通过利用标准 2.5D 封装的GMI3(全局内存互连 3)接口进行通信。对于 MI300,AMD 添加了一个新的焊盘通孔接口,可绕过 GMI3 链路,从而提供垂直堆叠芯片所需的 TSV(通过硅通孔)。该接口在双链路宽模式下运行。

5nm XCD GPU 芯片标志着 AMD GPU 设计的全面芯片化。与 MI200 中使用的小芯片表现为两个独立的设备不同,MI300 小芯片表现为一个单片 GPU。

每个 XCD 有 40 个物理 CDNA3 计算单元,但只有 38 个被激活(这有助于解决良率问题)。每个 38-CU 小芯片都有 4MB 共享 L2 (16x 256KB)。XCD 和 IOD 具有硬件辅助机制,可将作业分解为更小的部分、分派它们并保持它们同步,从而减少主机系统开销。这些单元还具有硬件辅助的缓存一致性。

每个 I/O 芯片上连接有两个 XCD,然后连接到两个 HBM3 堆栈。这允许 GPU 与两个连接的堆栈进行私密通信,以缓解带宽、延迟和一致性问题。然而,每个 XCD 都可以与任何内存堆栈通信。

当然,寻址远程堆栈会带来延迟损失。内存事务传输得越远,就会产生越长的延迟。AMD 指出,直接连接到 IOD 和 XCD 的 HBM 是零跳事务,而访问 IOD 上的不同内存堆栈是两跳跳转。最后,访问相邻 IOD 上的内存堆栈是三跳跳转。两跳跳跃的代价是延迟增加大约 30%,而三跳跳跃则增加 60% 的延迟。

幻灯片显示了 NoC 的可用带宽,封装垂直部分的 I/O 芯片之间的带宽为 1.2 TB/s/dir,而水平数据路径提供的带宽略多,为 1.5 TB/s/dir。带宽,以帮助容纳来自 I/O 设备的额外流量,从而允许 I/O 流量与内存流量分开处理。封装右侧和左侧的 PCIe 复合体为每个 I/O 芯片提供 64 GB/s/dir 的吞吐量。在包的顶部和底部,您可以看到每个 HBM 堆栈提供 665 GB/s 的吞吐量。

AMD 有多种分区方案,可将计算单元划分为不同的逻辑域,就像 EPYC 处理器的 NPS 设置一样。这允许将不同的 XCD 分成不同的组以优化带宽,从而最大限度地提高性能并限制“NUMAness”的影响。多种配置范围从将单元寻址为一个逻辑设备到将它们寻址为八个不同的设备,以及多种中间选项,为各种工作负载提供了足够的灵活性。

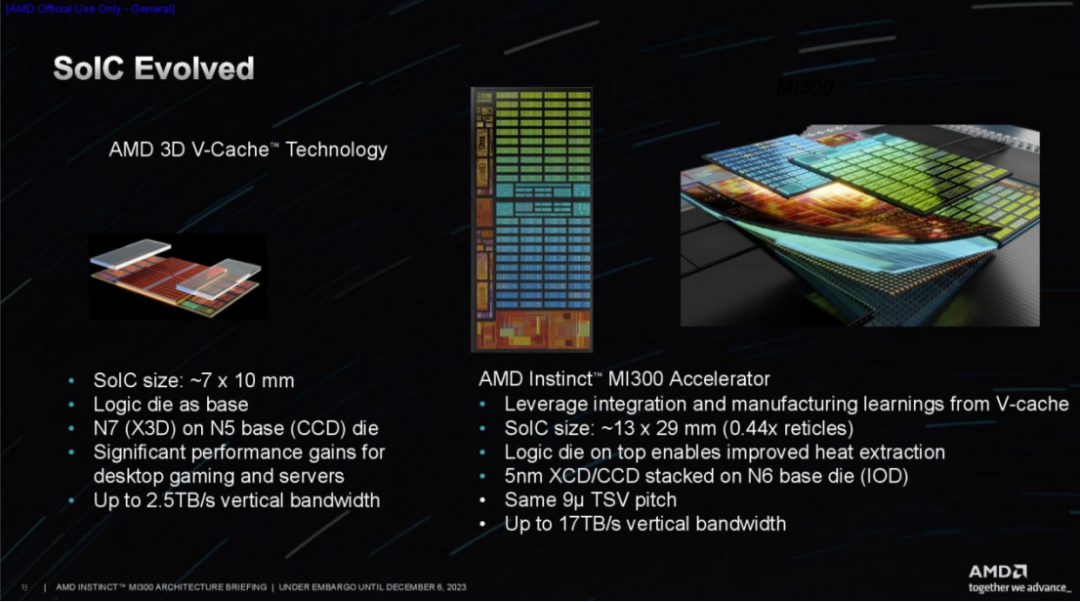

AMD 确定 3D 混合键合 (SoIC) 是在计算单元和 I/O 芯片之间提供足够带宽的唯一现实途径。公司在该技术方面拥有丰富的经验;它已经应用于数百万个配备 3D V-Cache 的 PC 处理器中。

该公司在这种现已成熟的混合键合技术方面积累的长期经验使其有信心在 MI300 处理器中继续采用该技术。与由 3D V-Cache 和标准型号组成的 AMD 消费类 PC 芯片系列相比,MI300 处理器代表该公司首次在整个产品堆栈中完全依赖该技术。

总体而言,SoC 连接可在各种 3D 堆叠单元中提供高达 17 TB/s 的垂直带宽。SoIC 尺寸为 13x29mm。

最后一张幻灯片中的剖面图展示了 3.5D 包装方法的复杂性和美丽。它说明了如何从底部使用有机基板、上方具有金属布线和 TSV 的 CoWos 无源硅中介层,以及采用混合键合(9 微米间距)的 3D 堆叠 IOD 和 XCD 来构建封装。将有机基板与硅中介层(底部)配合的巨大铜凸块突出了 3D 堆叠部分的顶部和底部芯片(靠近顶部)之间几乎不可见的混合键合连接是多么小和密集。

混合键合技术需要减薄芯片以暴露 TSV,以便它们可以配对。因此,AMD 必须在封装顶部采用硅垫片以保持结构完整性,就像其他配备 3D V-Cache 的处理器一样。

AMD 高级副总裁、AMD 公司院士兼产品技术架构师 Sam Naffziger 向我们介绍了团队在设计阶段遇到的一些挑战。

巧妙的IP重用一直是AMD小芯片战略的基石,MI300也不例外。MI300 团队没有资源为 MI300 构建全新的 CPU CCD,因此他们要求该公司的 CCD 团队在设计阶段的早期将 3D 接口 (TSV) 添加到 EPYC CCD。令人惊讶的是,工程团队找到了一种将连接塞入现有 GMI 接口之间的方法。

在第一张幻灯片中,您可以看到两个小蓝点代表 TSV 的总面积,而点两侧的大橙色矩形块是用于 2.5D 封装的标准 GMI3 接口。这说明了 SoIC 技术的密度和面积效率是多么令人难以置信。AMD 还添加了一些门、开关和多路复用器,以允许信号从 GMI3 接口重新路由到 3D 接口。

AMD 创建了 I/O 芯片的镜像版本,以确保它们可以旋转到正确的位置,同时确保 XCD 中的内存控制器和其他接口仍然正确对齐。工程团队对称地设计了接口/信号和电源连接,从而允许小芯片旋转,如第二张图所示。

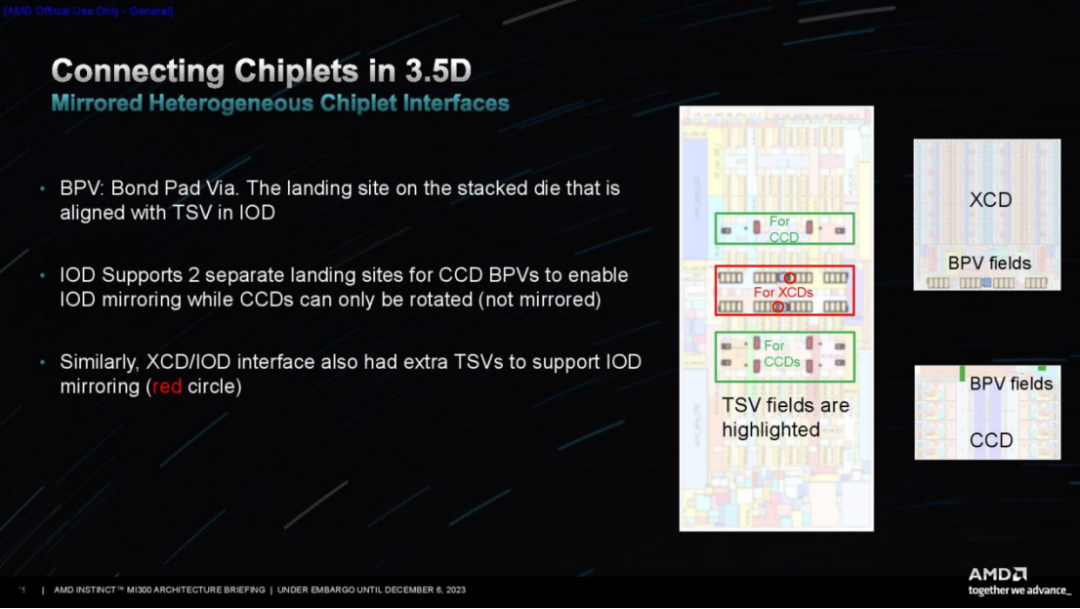

然而,虽然 AMD 专门为 MI300 从头开始设计了 I/O 芯片,但该团队必须采用 EPYC 的现有 CCD 设计。他们不想为 CCD 创建镜面掩模组,这在此类设计中通常是必需的,以确保正确的接口对齐,因为这会增加设计的成本和复杂性。然而,其中两个 CCD 需要旋转 180 度才能确保正确对齐。然而,CCD的外部接口设计不对称,因此带来了挑战。

如幻灯片所示,AMD 通过在 I/O 芯片上的键合焊盘通孔 (BPV) 连接点添加一些冗余来克服这一挑战,从而允许 CCD 仅旋转而不是镜像。

不过,电力输送仍然是一个挑战。TSV 是非常小的铜插头,AMD 需要为位于 I/O 芯片顶部的计算芯片提供数百安培的电源。细小的 TSV 不太适合这项工作,因此它们需要大量的连接来供电。AMD 设计了一种新的电网来克服这个问题,它满足了 IR 压降目标,并且没有超过电流密度限制。

最后,由于 3D 堆叠设计,该设计提出了一些新的热挑战。通过热建模,AMD 确定了两种类型的极端操作条件:内存密集型和 GPU 密集型。然后利用其基于使用模式在单元之间动态转移功率的行之有效的策略来帮助缓解这些问题。

因此,一个令人难以置信的处理器诞生了。AMD的MI300在相当长的一段时间内对英伟达在AI和HPC工作负载方面的性能主导地位提出了第一次真正的挑战,AMD坚称自己有能力满足需求。在 GPU 短缺的时代,这是一种竞争优势,并且肯定会刺激行业的快速发展。AMD 现在正在向其合作伙伴运送 MI300 处理器。