软件工具: Vivado

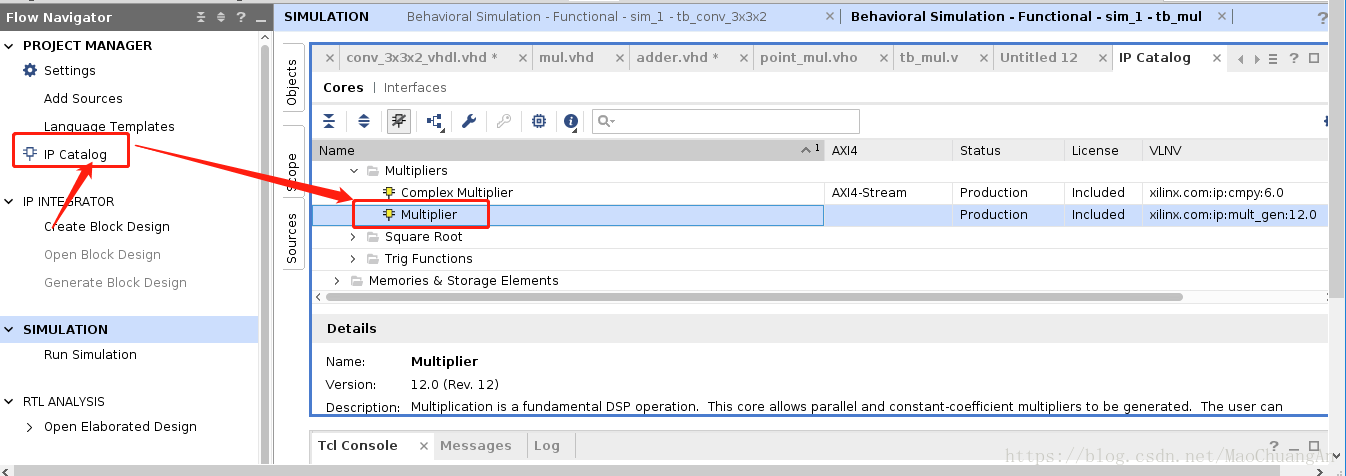

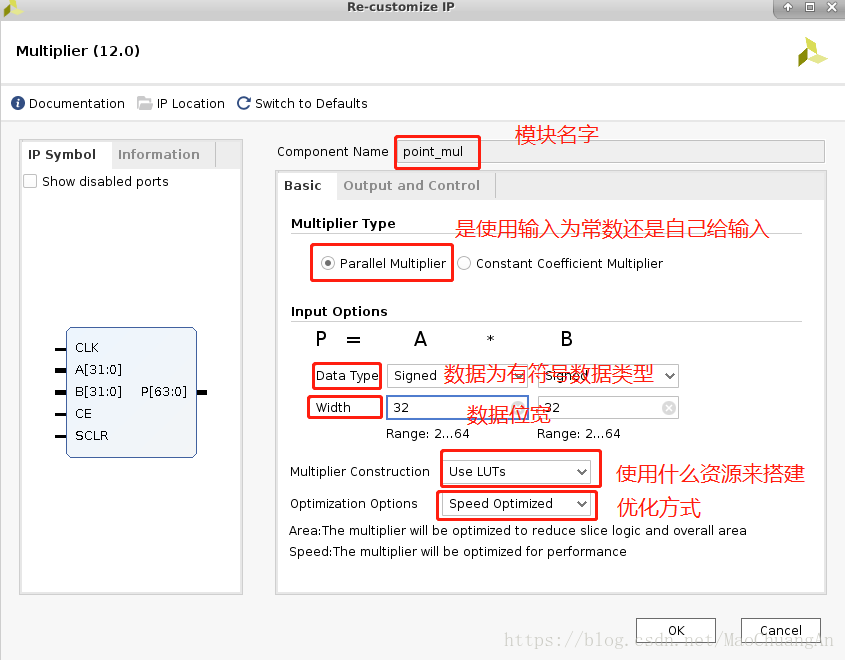

一、配置Multipiler

按照以下进行配置。

重点说一下流水线级数,这里选择5,说明时钟使能后5个周期可以输出结果。

二、编写代码

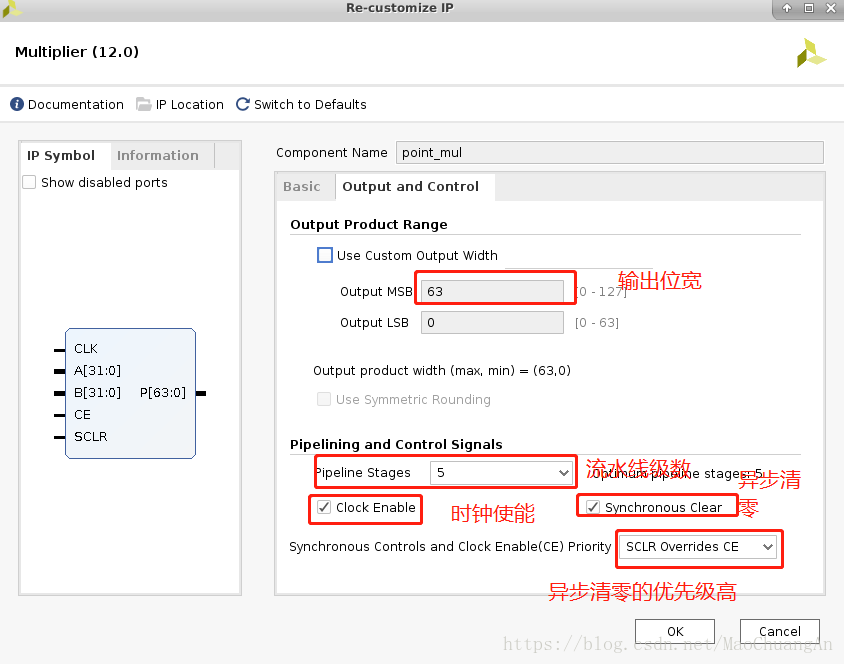

生成的模块:

COMPONENT point_mul

PORT (

CLK : IN STD_LOGIC;

A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

CE : IN STD_LOGIC;

SCLR : IN STD_LOGIC;

P : OUT STD_LOGIC_VECTOR(63 DOWNTO 0)

);

END COMPONENT;

-------------------------------------------------------------

顶层模块:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity mul is

Port (

CLK : IN STD_LOGIC;

A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

CE : IN STD_LOGIC;

SCLR : IN STD_LOGIC;

P : OUT STD_LOGIC_VECTOR(63 DOWNTO 0)

);

end mul;

architecture Behavioral of mul is

COMPONENT point_mul

PORT (

CLK : IN STD_LOGIC;

A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

CE : IN STD_LOGIC;

SCLR : IN STD_LOGIC;

P : OUT STD_LOGIC_VECTOR(63 DOWNTO 0)

);

END COMPONENT;

begin

inst_mul: point_mul

port map(

CLK => CLK,

A => A,

B => B,

CE => CE,

SCLR => SCLR,

P => p

);

end Behavioral;

测试模块:

`timescale 1ns / 1ps

module tb_mul;

parameter ClockPeriod = 10;

reg CLK;

reg [31:0] A;

reg [31:0] B;

reg CE;

reg SCLR;

wire [63:0] P;

initial

begin

CLK = 1;

A = 0;

B = 0;

CE = 0;

SCLR = 1;

#100;

SCLR = 0;

CE = 1;

A = 10;

B = 10;

#100;

CE = 0;

end

always #(ClockPeriod/2) CLK = ~CLK;

mul uut(

.CLK(CLK),

.A(A),

.B(B),

.CE(CE),

.SCLR(SCLR),

.P(P)

);

endmodule

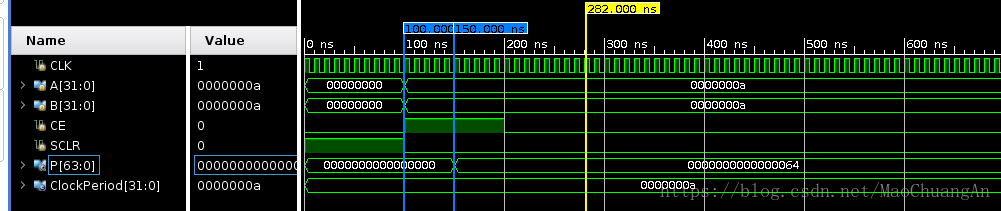

结果:

输入为A和B。分别是16进制的0000000a。可以看到P在CE使能后5个周期输出了结果。之所以是五个周期,是因为在设置时设置了5个周期的流水线。

---------------------

作者:为中国IC之崛起而读书

来源:CSDN

原文:https://blog.csdn.net/MaoChuangAn/article/details/82999909