作者:小青菜哥哥

原文链接: https://blog.csdn.net/XiaoQingCaiGeGe/article/details/104844062

声明:本文由原创博主授权转发,如需转载请联系博主

Xilinx公司的JESD204 IP核能够实现复杂的JESD204B协议,支持的速度范围为1Gbps~12.5Gbps。该IP核可以被配置成发送器或者接收器,不能配置成同时收发。目前该IP核仅支持vivado软件,不支持ISE,且仅支持xilinx公司的7系列及其以上系列的FPGA硬件。该IP核的主要特性包括以下几点:

1. 全面支持JESD204B协议

2. 一个IP核可以支持最多8个lane,多个IP核级联最多支持32个lane

3. 支持初始化链路对齐(Initial Lane Alignment)

4. 支持扰码/解扰功能(scrambling)

5. 每个数据帧(frame)的数据量范围1~256字节(octet)

6. 每个多帧(multiframe) 的数据量范围1~32帧(frame)

7. 支持子类0、1和2

8. 包含了物理层和数据链路层功能

9. 基于AXI4-lite协议的通用IP核配置接口

10. 基于AXI4-Stream协议的数据接口

JESD204 IP核利用FPGA内部的专用高速串行收发器(GTX、GTH、GTP或GTY)来实现1~8路、1~12.5Gbps的JESD204B接口协议。该IP核既可以配置成发送器来与DAC进行数据通信,也可以配置成接收器来与ADC通信,且还可以多核级联使用来实现超过8路的数据通信。

该IP核只能在vivado工具软件里使用,且仅提供了基于verilog语言的开发例程,对于普通应用来说,用户可以基于该例程进行二次开发,减轻开发难度。

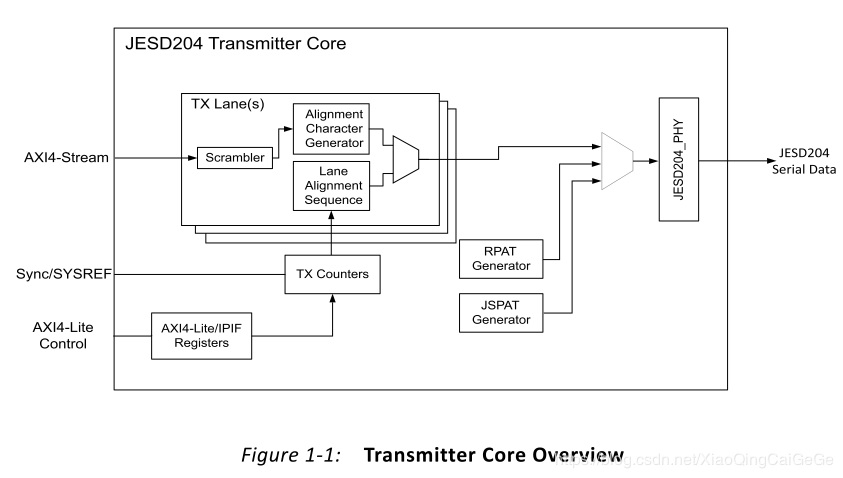

发送器

IP核配置成发送器向DAC传输数据时,其结构如下图所示,主要包含的模块有:

1. AXI4-Stream数据接口

2. TX发送逻辑:扰码逻辑、对齐字符插入逻辑以及初始化链路对齐序列生成逻辑

3. TX计数器:控制逻辑、SYNC/SYSREF接口以及状态机逻辑

4. JESD204 PHY(主要为MGT模块)

5. RPAT以及JSPAT测试数据生成器

6. AXI4-lite配置管理接口

接收器

IP核配置成接收器与ADC通信时,其结构如下图所示,主要包含的模块有:

1. AXI4-Stream数据接口

2. RX发送逻辑:ILA识别逻辑、解扰码逻辑、对齐字符监测和替换逻辑

3. 本地多帧时钟(LMFC)状态机和SYNC/SYSREF接口

4. JESD204 PHY(主要为MGT模块)

5. 差错计数器(监测每条lane的数据)

6. AXI4-lite控制管理接口

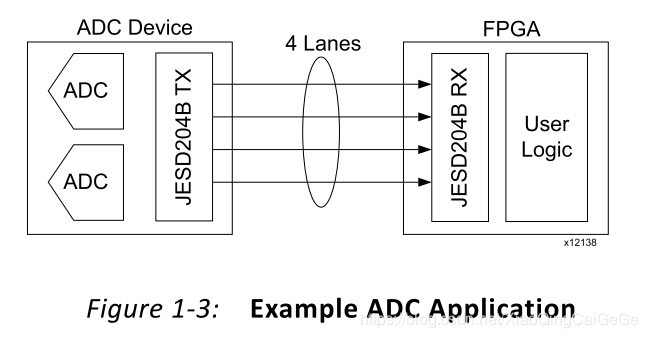

如下图所示为JESD204 IP核例化为4通道接收器时与ADC芯片的应用,使用IP核后,用户只需要进行应用层逻辑开发:

如下图所示为JESD204 IP核例化为4通道发送器时与DAC芯片的应用:

注意

JESD204 IP核需要有xilinx官方的license才能使用,license需要找官方或者代理机构购买,也可以通过其它渠道得到~~~。License分为3种:

仿真license

Vivado自带JESD204 IP核的仿真license,安装完vivado后,只能调用JESD204 IP核进行仿真,不含布局布线等功能。

有时效的完整license

该license支持JESD204 IP核综合、布局布线、生成bit文件、下载到FPGA测试等全部功能,但有时效性,有效期一般为3个月,该license供用户全面评估JESD204 IP核的功能。登入xilinx官网的JESD204 产品页面可以免费申请该license。

完整license

联系xilinx官方或其代理商购买完整的license后,可以任意使用JESD204 IP核提供的所有功能。

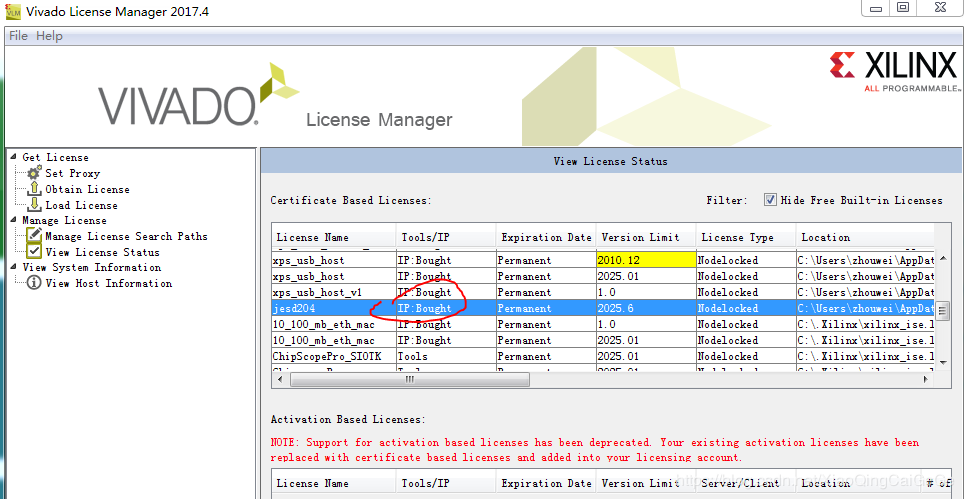

如下图所示为购买完整的JESD204 IP核license并载入vivado开发软件后,在vivado license manager页面下的状态,可以看到其显示为IP:Bought(已购买)。这样JESD204 IP核的功能就可以完全使用了。