西门子发布 Veloce CS,解锁三款新品助推硬件加速仿真和原型验证

judy 在 周三, 04/24/2024 - 14:33 提交

Veloce CS 可在所有平台复用,实现无缝迁移,将系统工作负载的执行和调试速度加快 10 倍

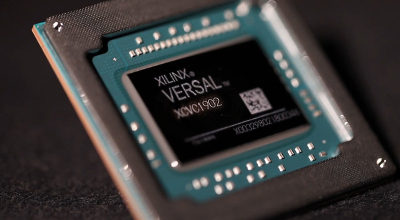

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

Veloce CS 可在所有平台复用,实现无缝迁移,将系统工作负载的执行和调试速度加快 10 倍

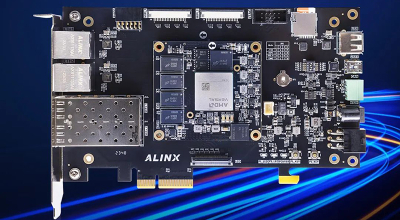

使用IBERT测试误码率和眼图必须有个收发环通的硬件,开发板上有2个SFP光纤接口,本实验把2个光接口收发两两连接,形成2个收发环通链路。

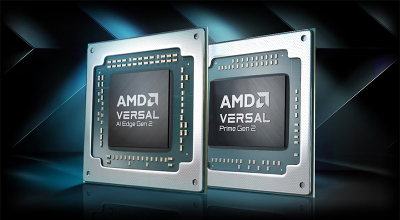

AMD 第二代 Versal AI Edge 系列和第二代 Versal Prime 系列自适应 SoC 为 AI 驱动和经典的嵌入式系统提供了单芯片智能性实现性能

系统看门狗定时器(System WatchDog Timer)通常用于嵌入式系统,可以有效的防止软件错误、系统死锁、篡改以及意外行为

本文旨在探讨在 Versal 中对 eMMC 进行格式化和烧写的方法。

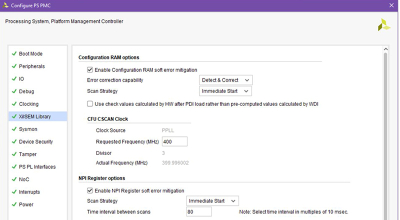

本文介绍如何推迟XilSEM扫描功能的开始。

Versal AI Edge VE2302器件拥有应用处理单元双核Arm Cortex-A72、实时处理单元双核Arm Cortex-R5F

本文介绍如何在Versal器件中推迟XilSEM的扫描工作

摆脱传统多FPGA解耦技术的束缚,在单块FPGA资源中支持更大规模的复杂电力电子电路模型

不同厂商的MSI-X结构所在配置空间的位置不同