Xilinx FPGA 和 SoC 的 UltraFast 设计方法指南 (v2021.2)

judy 在 周二, 11/30/2021 - 09:58 提交

本白皮书描述了推荐的设计方法,以实现对 Xilinx® FPGA 器件资源的有效利用,并在 Vivado® 设计套件中更快地实现设计和时序收敛。提供了推荐方法背后的原因,以支持和实现明智的设计决策。

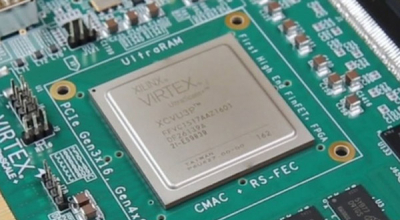

"UltraScale+" 是赛灵思(Xilinx)公司推出的一款 FPGA(可编程门阵列)产品系列。该系列是 Xilinx 的 UltraScale 架构的一部分,旨在提供更高的性能、更低的功耗和更高的集成度。UltraScale+ FPGA 主要面向高性能计算、数据中心加速、通信、工业自动化等领域。

UltraScale+ FPGA 系列的设计目标是满足对高性能、灵活性和可编程性能有要求的广泛应用。这些包括但不限于高性能计算、数据中心加速、5G 通信、人工智能、工业自动化等领域。

本白皮书描述了推荐的设计方法,以实现对 Xilinx® FPGA 器件资源的有效利用,并在 Vivado® 设计套件中更快地实现设计和时序收敛。提供了推荐方法背后的原因,以支持和实现明智的设计决策。

《UltraFast 设计方法时序收敛快捷参考指南》提供了以下分步骤流程, 用于根据《UltraFast设计方法指南》( UG949 )中的建议快速完成时序收敛:

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

赛灵思 UltraFast™ 设计方法旨在帮助简化当今器件设计进程的最佳实践,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

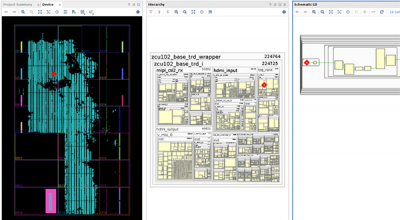

本文档旨在描述推荐的设计方法,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

赛灵思可编程器件含有数百万个逻辑单元 (LC),并且集成的现代复杂电子系统也与日俱增。本高效设计方法指南提供了一整套最佳做法,旨在于较短的设计周期内完成此类复杂系统的创建。

赛灵思可编程器件含有数百万个逻辑单元 (LC),并且集成的现代复杂电子系统也与日俱增。本高效设计方法指南提供了一整套最佳做法,旨在于较短的设计周期内完成此类复杂系统的创建。

卷积占据了CNN网络中绝大部分运算,进行乘法运算通常都是使用FPGA中的DSP,这样算力就受到了器件中DSP资源的限制。比如在zynq7000器件中,DSP资源就较少,神经网络的性能就无法得到提升。利用xilinx器件中LUT的结构特征,设计出的乘法器不但能灵活适应数据位宽,而且能最大限度降低LUT资源使用

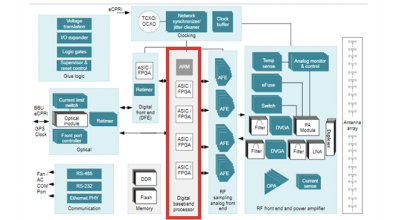

5G是目前通信设备领域的市场趋势, Massive MIMO指的是64T64R应用中常用的多输入和多输出, 更多的发送器和接收器通道需要更多的数字处理器(FPGA / ASIC)来执行数据传输,而典型的64T64R MIMO应用中通常需要4-5个数字处理器。 每个FPGA都需要自己的电源上电/下电的时序,以便FPGA能够正常工作

Xilinx® Alveo™ U280 工程样板 (ES) 数据中心加速器卡旨在满足现代数据中心不断变化的需求。Alveo U280 ES 建立在 Xilinx 16 nm UltraScale™ 架构基础之上,能够以 410 GB/s 的带宽提供 8GB 的 HBM2,从而可为数据库、分析和机器学习推断等内存有限的计算密集型应用提供灵活应变的高性能加速