Xilinx FPGA AXI4总线(四)——自定义 AXI-Lite 接口的 IP 及源码分析

judy 在 周四, 04/08/2021 - 10:19 提交

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

AXI4、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手机制进行通信。信息传输的发起者使用Valid 信号指示数据何时有效,接收端产生 Ready 信号来表明已经准备好接收数据,当两者均为高时,启动传输。

通过嵌入式软核或者硬核通过AXI_Lite接口(Master)控制FPGA端引脚的GPIO。按照AXI互联机制我们知道,我们的自定义IP是通过AXI_Interconnect连接到Master端,整体的框图也比较简单,为了验证方便我们只按照红色线路径进行测试。

对于使用AXI总线,最开始肯定要了解顶层接口定义,这样才能针对顶层接口进行调用和例化,打开axi_lite_v1_0.v文件,第一段就是顶层的接口定义:

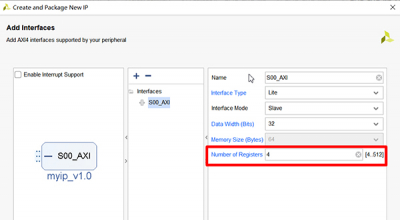

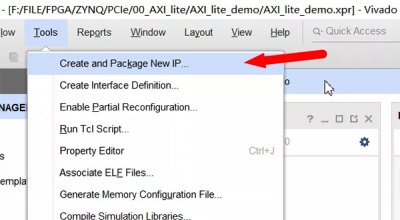

要看到AXI-Lite的源码,我们先要自定义一个AXI-Lite的IP,新建工程之后,选择,菜单栏->Tools->Creat and Package IP