Xilinx PYNQ PS与PL的接口说明

judy 在 周一, 12/24/2018 - 13:32 提交

Zynq在PS和PL之间有9个AXI接口。 在PL方面,有4x AXI Master HP(高性能)端口,2x AXI GP(通用)端口,2x AXI Slave GP端口和1x AXI Master ACP端口。 PS中还有连接到PL的GPIO控制器

Zynq在PS和PL之间有9个AXI接口。 在PL方面,有4x AXI Master HP(高性能)端口,2x AXI GP(通用)端口,2x AXI Slave GP端口和1x AXI Master ACP端口。 PS中还有连接到PL的GPIO控制器

PYNQ-Z2的硬件平台以Xilinx ZYNQ SoC为核心,而Arm与FPGA的异构系统是创建高性能嵌入式系统应用的基础也是与市面上众多嵌入式平台最大的不同之处。本台有别于一般传统的ZYNQ开发平台,PYNQ-Z2支持Python 语言开发,同时也可以采用传统的Xilinx Vivado 开发工具流程平台开发嵌入式系统应用

用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核

实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench文件来与所得结果进行对比验证。

在前面几期的学习中,我们对于PYNQ的环境配置做了较为详细的介绍,并对PYNQ与ZYNQ的异同点做了较为深入的探究。我们知道,PYNQ = Python + ZYNQ,即将ZYNQ部分功能的Python化,直接调用Python库和FPGA硬件库进行功能的开发,典型的例子便是PYNQ_z2开发板

在实际玩Zynq中断之前,先扯一扯中断这个神奇的东西~。实时性是一个嵌入式系统很重要的性能,实时性体现在一个系统对外部事件的响应能力和处理能力上,而CPU对一个事件的响应及处理主要依托于 —— 中断。

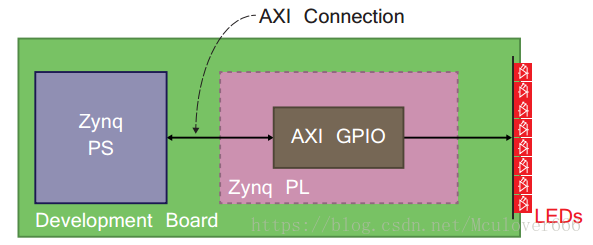

上一节中分别独立实验了Zynq的PS端和PL端,并初步实验了PS端先硬件再软件的开发流程和IP核设计的设计方法。第一节中提及到:Zynq是以PS端的ARM处理器系统为核心的,PS端和PL端是通过AXI总线,并且Xilinx已经提供了各种AXI通信的IP核,接下来的实验中将会更加明确的体验到利用IP核设计的设计方法。

1.实验目标

板载的LED和RGBLED都是接在PL端的,这个实验将利用PS端程序通过AXI总线控制连接在PL端的LED。

2.实验步骤

整个实验流程参考《The Zynq Book Tutorials》的chpt1:First Designs on Zynq(这本实验指导手册是英文的,但我个人认为英文原版要比中文看着清楚很多)。

作者:Mculover666

在上一篇中提到,Pynq是为了降低开发人员的门槛,但是作为一个学习嵌入式开发的学生,当然要一步一个脚印打好基础,所以选择从Zynq入手学习,等跑起来Linux系统再运用Python开发也不迟,知其然也知其所以然,开发效率更高,所以接下来的几篇都是关于Zynq的,如果想直接玩Pynq可直接跳过,毫无影响。

1.Zynq的架构

在开始实验之前对Zynq芯片有一个基本的认识,如果想深入了解关于Zynq的理论部分,推荐参考The Zynq Book,有英文版和中文版,在此对于Zynq的理论浅尝辄止,不做深究,重点放在实验应用上。

Zynq中包含两大功能块:PS部分和PL部分。

作者:Mculover666

今天刚刚到手一块PYNQ-Z2,确认过眼神,是我想要的板子,话不多说,开干。

在goggle上搜zcu102 pynq可以找到一些移植方法的信息

0. Prebuilt

PYNQ移植ZCU102编译好的固件