AMD Xilinx MPSoC VCU 使用要点

judy 在 周三, 04/12/2023 - 16:46 提交

VCU与DDR连接的AXI Interconnect的位宽是32-bit。 建议改为64-bit或者128-bit

VCU与DDR连接的AXI Interconnect的位宽是32-bit。 建议改为64-bit或者128-bit

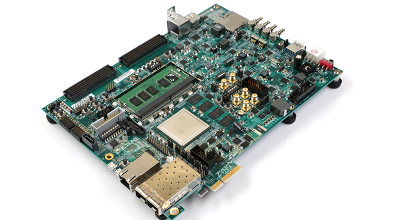

该问题实际有几个方面,其中包括硬件、软件和 ZCU106 VCU TRD 等。

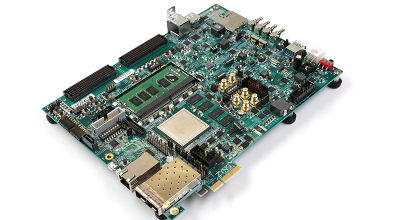

本演讲将展示如何使用 Zynq UltraScale+ MPSoC EV 器件中集成的VCU功能,解决流媒体应用中的技术挑战

在有些应用中,发现I帧不够大。MPSoC VCU CtrlSW可以设置每一帧的QP大小。因此,可以通过设置I帧的QP,提高I帧的大小,从而提高I帧的质量。

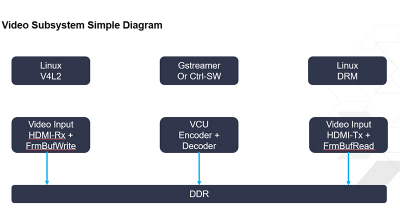

MPSoC VCU在很多产品中得到了应用。在不同产品的调试过程中,有一些共同的办法。首先看看Video子系统的简单框图,其中包含视频输入、编解码、视频输出等模块。视频输入模块,硬件可能是HDMI-RX和FrmBufWrite; 软件一般是Linux V4L2。编解码模块是VCU,配套的软件是GStreamer,或者Ctrl-SW

有工程师询问vcu-ctrl-sw里decoder的退出机制。 下面的内容,根据vcu-ctrl-sw 2020.2分析。

Xilinx提供超低延时编解码方案,并提供了全套软件。MPSoC Video Codec Unit提供了详细说明。其中的底层应用软件是VCU Control-Software(Ctrl-SW)。本文主要说明为Ctrl-SW增加输出NV12视频的功能。

详细了解基于 Zynq UltraScale+ MPSoC 视频编解码器单元 (VCU) ROI 的编码参考设计的系统与硬件架构。 在详细了解硬件架构之前,先大概了解一下系统架构。 最后将介绍用于启动参考设计的资源。

通过本视频详细了解基于 Zynq UltraScale+ MPSoC 视频编解码器单元 (VCU) ROI 的编码参考设计的软件架构。 首先,我们将讨论 Xilinx 视频和连接 IP 支持堆栈, 接着,视频将描述 VCU ROI 应用程序的软件堆栈,并详细讨论 Gstreamer 流输出管道、以及 ROI GStreamer 插件和 Gstreamer 流输入管道。

VCU 模块在PL侧,一共有五个AXI接口,它们分别是两个 Encoder AXI,两个 Decoder AXI, 和一个 MCU AXI。两个 Encoder/Decoder 的 AXI 接口必须都连接到 MPSoC PS,即使只用一路编码,或者一路解码