研讨会回放|AMD Vitis™ HLS 研讨会精彩回放及问题详解

judy 在 周五, 01/05/2024 - 14:38 提交

本次研讨会中我们收到了来自广大用户和网友的热情提问,针对代表性较强的问题,专家在线进行了集中答疑

本次研讨会中我们收到了来自广大用户和网友的热情提问,针对代表性较强的问题,专家在线进行了集中答疑

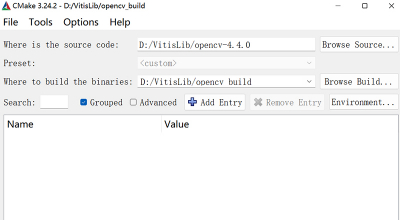

打开cmake-gui.exe,点击Browse Source选择你解压出来的OpenCV Source目录

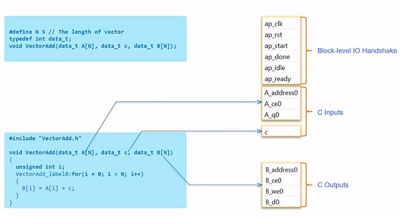

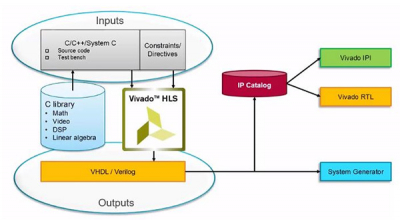

Vitis高层次综合可通过在选定的 AMD 器件上将 C/C++ 代码综合为可编程逻辑的 RTL 代码

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS

您是否担心 RTL 设计中的延迟?您的设计是否有效并经过优化?

LUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!

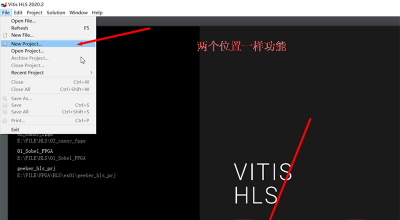

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

本文我们通过一个具体的实例,演示HLS设计流程。

传统的FPGA RTL设计流程主要是采用VHDL、VerilogHDL或System Verilog进行工程的开发,同时也是通过硬件描述语言来编写测试案例对开发的工程进行仿真验证