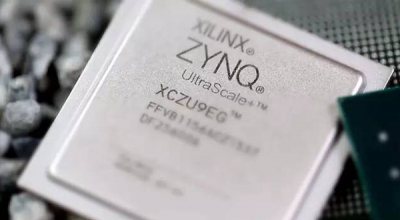

AMD Xilinx SoC: 定制PetaLinux中的FSBL

judy 在 周四, 05/18/2023 - 15:10 提交

客户为AMD Xilinx SoC创建了PetaLinux工程。需要定制PetaLinux中的FSBL

客户为AMD Xilinx SoC创建了PetaLinux工程。需要定制PetaLinux中的FSBL

本文是FSBL关于看门狗的用法总结。

在此物理攻击中,攻击者可能利用 Zynq-7000 SoC 第一阶段启动加载程序 (FSBL) 绕过身份验证

有工程师反馈R5引导A53和R5的应用程序后,A53和R5的应用程序没有正确执行。因此做了一个MPSoC R5引导4个A53和两个R5的应用程序的例子。

话不多说,进入今天的主题:生成zynq裸核启动文件。1、首先在vivado SDK中分别建立两个工程;2、配置Core1即从核中的BSP文件;3.配置Core0和Core1的DDR空间分配;4.建立FSBL文件,并配置main()文件;5.生成mcs文件和烧写mcs文件到QSPI Flash;6.完成操作将.MCS文件烧写进板子里

前言

在上一次分析中,分析到了

HandoffAddress = LoadBootImage();

花了几天看完了FSBL的代码,在这里做个总结,分析一下zynq的启动过程。

众所周知,xilinx zynq 7000系列的芯片中包括两个部分,PS和PL,也就是FPGA的逻辑编程的部分跟嵌入式ARM的部分,ARM部分是双核的A9处理器。关于FPGA的部分在这里就不说了。其实说的简单点,可以吧这个芯片看成一个带有FPGA外设的ARM处理器,下面详细分析一下启动流程。