HLS 分区能否加速 FPGA布局布线?

judy 在 周三, 05/25/2022 - 09:46 提交

最近,在ACM的FPGA 2022会议上发表了一篇题为“RapidStream: FPGA HLS设计的并行物理实现”的论文,论文中描述了一种非常有趣的方法,通过FPGA设计软件推动HLS设计更快地运行在多核处理器上。

最近,在ACM的FPGA 2022会议上发表了一篇题为“RapidStream: FPGA HLS设计的并行物理实现”的论文,论文中描述了一种非常有趣的方法,通过FPGA设计软件推动HLS设计更快地运行在多核处理器上。

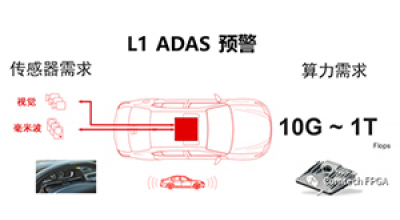

赛灵思作为可编程器件的领导品牌,在汽车电子系统,尤其在传感器融合方面提供了全面的方案。且待本文向您徐徐道来

如果您正开发一款智能边缘应用,需要将处理能力融于超紧凑的封装中,那么我们要告诉您一个好消息:Zynq® UltraScale+™ ZU1 MPSoC 现正以更多样的封装形式出货,包括超紧凑 InFO 封装。

有关安全特性的示例十分广泛,从拒绝错误的用户输入、在特定条件下立即停止输入,到发出的各类警报,再到向邻近设备发出指令,不一而足。

我们一直推荐用户在FPGA板卡硬件调试中使用IBERT测试transceiver,以便于排除电源、参考时钟和连接介质的问题,确保transceiver可以正常进行用户需要的高速串行设计调试。

Xilinx 的 20nm Kintex UltraScale™ XQRKU060 抗辐射现场可编程门阵列 (FPGA) 功能强大,足可实现全新的系统架构。

本文以MRMAC IP为例,并在以太网IP的GT配置那页,选择GTM和156.25MHz时钟。

Vitis HLS 的 2021.1 GUI 中添加了许多新功能。请参阅下面的详细信息。

AMD-赛灵思 AI 团队的论文能在激烈竞争中突出重围,其中一定蕴含着独特的创新与价值。我们与论文第一作者、AMD-赛灵思 AI 团队算法工程师王莉深度对话,为大家带来这份独家的论文解析。

2021赛灵思自适应计算挑战赛答疑会1-4集锦