AMD两篇论文入选可编程逻辑顶会 FPL 2022

judy 在 周四, 08/25/2022 - 15:08 提交

AMD AI 研发团队入选的两篇论文侧重基于 Versal 异构计算平台的 AI 处理器架构设计,充分发挥 Versal 平台的算力和灵活性优势。

AMD AI 研发团队入选的两篇论文侧重基于 Versal 异构计算平台的 AI 处理器架构设计,充分发挥 Versal 平台的算力和灵活性优势。

本演示概述了 Kria SOM 和视觉 AI 入门套件,并指导用户开始使用该套件进行设计。

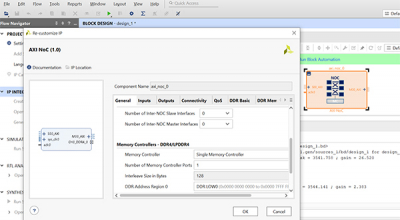

在FPGA开发设计中,我们可能会经历由于资源占用过高的情况,例如BRAM、LUT和URAM等关键资源利用率达到或超过80%

该项目基于AMD Xilinx Varium C1100 FPGA加速卡,为 Filecoin 区块链应用中的Poseidon哈希算法提供了一套完整的硬件加速方案。

本文介绍Xilinx® UltraScale FPGA实现LVDS 1:7接收数据解串

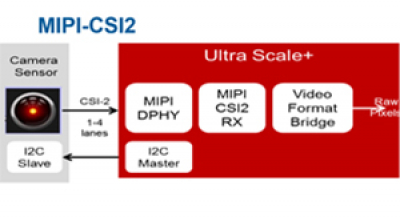

MIPI典型应用是在ISP领域,CMOS senor输出视频流,给FPGA PHY层,串并转换后给协议层处理。

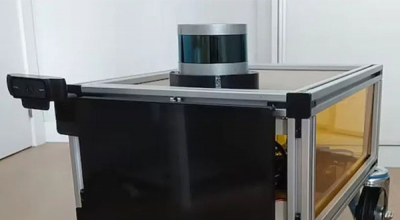

Kria™ KR260机器人入门套件包括用于机器人、机器视觉、工业通信和控制应用的预建接口、可定制的硬件加速功能,并通过Kria SOM加快部署时间。

今天我们来介绍一下I/O planning方面的设计考虑和实现流程。

本文将对 Vitis AI 2.5 的新功能及优化进行概述。

本视频介绍了此版本中的新功能和增强功能,包括 Versal® 设计的结果质量 (QoR) 改进、基于 ML 的资源估计、面向 Versal 器件的 ML 策略运行以及其他器件支持。