直播 | 如何在Alveo Versal上快速部署AI推断 - VCK5000助力软件/AI开发升级

judy 在 周五, 05/21/2021 - 09:30 提交

赛灵思近期推出重磅活动,2495 美元的优惠价购买用于 AI 推断的 VCK5000 Versal™ 开发卡,VCK5000 的计算能力比当前的服务器级 CPU 高 100 倍,MLPerf 推断性能也高于当前的服务器级 GPU,是云加速和边缘计算应用的理想开发平台。

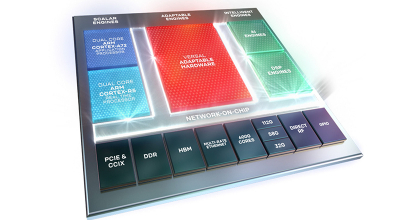

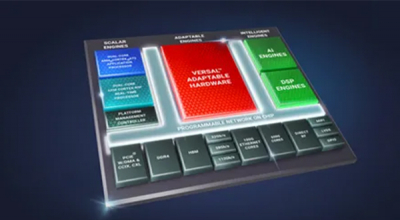

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

赛灵思近期推出重磅活动,2495 美元的优惠价购买用于 AI 推断的 VCK5000 Versal™ 开发卡,VCK5000 的计算能力比当前的服务器级 CPU 高 100 倍,MLPerf 推断性能也高于当前的服务器级 GPU,是云加速和边缘计算应用的理想开发平台。

今年 4 月,赛灵思取得了令人激动的阶段性成果,即宣布实现 Versal™ AI Core 系列和 Versal Prime 系列的全面量产和付运。对于 Versal Prime 系列而言,这意味着 Vm1xxx 的首批量产器件进入供货状态;VM1xxx 器件可支持 PCIe® Gen 4 和 32G GTY 收发器

I2C 总线的两根信号线 SCL 和 SDA 需要上拉才能正常工作,当板卡上没有合适的硬件设置或者没有合适的 I2Cslave 设备,我们就无法进行 I2C 软件测试。那么是否可以将两个 PSI2C 控制器通过 EMIO 接口互连起来呢?

每个 RPU 处理器都有 1 个 DBGDRAR 寄存器,其中包含 CoreSight 根 ROM 表的地址。但读取此寄存器时会返回错误的地址 0xfe800003。正确的返回地址应为 0xf0800003。尝试访问包含错误地址的 CoreSight 根 ROM 表将导致 RPU 处理器发生软件异常。

SmartLynq+ 模块教程视频介绍了如何在 Versal ACAP 设计中包括高速调试端口,并演示了 SmartLynq+ 模块配置和 Linux 映像下载流程。

本视频介绍Versal自适应计算加速平台ACAP。介绍了Versal中的仿真和调试功能。

处理器可使用等待事件 (wait for event, WFE) 或等待中断 (wait for interrupt, WFI) 机制来进入低功耗状态。仅当嵌入式跟踪宏单元 (Embedded Trace Macrocell, ETM) 耗尽 AMBA ATB 接口上的所有跟踪字节后,处理器才能进入低功耗状态。

赛灵思今日宣布,其 Versal AI Core 与 Versal Prime 系列器件现已全面量产并向客户出货。此外,Versal 产品组合的第三个系列 Versal Premium 也已通过赛灵思早期试用计划出货给多家一级客户。

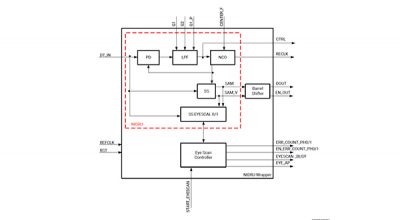

本文描述了Versal™ ACAP的一个非整数数据恢复单元(NIDRU)。NIDRU将较低的数据速率限制扩展到0 Mb/s,并允许SelectIO作为时钟和数据恢复单元运行。

本文描述Versal™设备中可用的SelectIO™资源。