【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章 FPGA片内RAM读写测试实验

judy 在 周一, 12/28/2020 - 09:30 提交

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

使用 2018.2 Ultra96 PetaLinux BSP 构建图像时,如果我在 Matchbox 桌面点击关断图标,电路板不关断。服务器窗口会关闭,屏幕变为空白,但电路板还在运行。

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次,实现亮、灭、亮、灭的控制。会控制LED灯,其它外设也慢慢就会了。

NeoPixels是数字控制的红、绿、蓝像素。由于每种颜色都由8位表示,总共24位,因此每个像素可以显示16777216种颜色中的一种。每个NeoPixel实际上是一个WS2812 LED。这些LED包含五个输入端,相对于地(VSS)在3.3V到5.0V(VDD和VCC)的电压范围内工作。

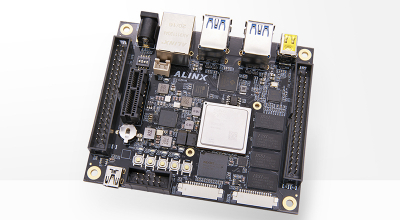

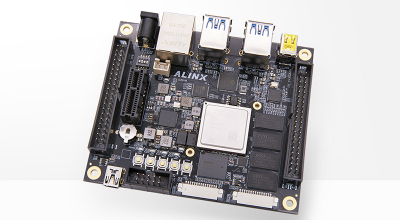

AXU2CGA/B的特点是体积小并扩展了丰富的外设。主芯片采用Xilinx公司的Zynq UltraScale+ MPSoCs CG系列的芯片,型号为XCZU2CG-1SFVC784I。AXU2CGA的PS端挂载了2片DDR4(2GB,32bit)和1片256Mb的QSPI FLASH。

Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平台。其亮点在于FPGA里包含了完整的ARM处理子系统(PS),包含了四核Cortex-A53处理器或双核Cortex-A53加双核Cortex-R5处理器,整个处理器的搭建都以处理器为中心,而且处理器子系统中集成了内存控制器和大量的外设,使处理器核在Zynq中完全独立于可编程逻辑单元

智能驾驶驱动的汽车行业正在走向电气化时代,全球各大车企都在加速电气化进程。未来智能驾驶将朝有哪些关键技术发展,有哪些阻碍发展的痛点,如何解决?以下为本刊独家采访赛灵思汽车电子系统架构师毛广辉实录。

FPGA作为赛灵思的一项重要发明,以其可编程和灵活性著称。起初,FPGA只是用来仿真ASIC,再进行掩码处理和批量制造使用。不过ASIC相比FPGA来说明显在定制化上要求过高,流片量过小情况下成本反而更高,因此两者毫不冲突地“各司其职”。

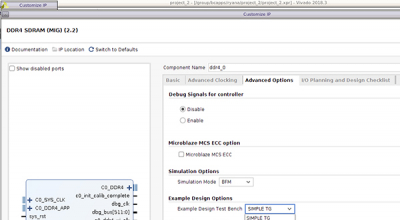

Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上与 Zynq UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

JEDEC LPDDR4 规范 JESD209-4B 的最新发布版本引入了在每次写操作突发前后都将 DQS_c 驱动至高位并保持一段时间的要求(4.13 写操作和屏蔽写操作 DQS 控制信号(WDQS 控制信号)),其详情如下