Verilog如何编写一个基础的Testbench

judy 在 周二, 03/21/2023 - 11:00 提交

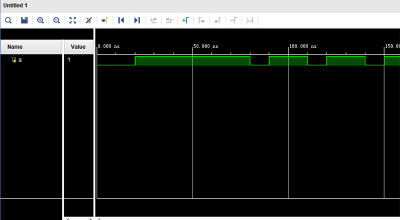

本文将讲述如何使用Verilog 编写一个基础的测试脚本(testbench)。

本文将讲述如何使用Verilog 编写一个基础的测试脚本(testbench)。

这篇文章将讨论 verilog 中一个重要的结构---- always 块(always block)。

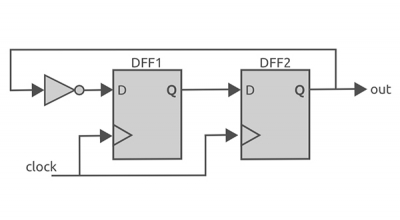

在verilog 中可以实现的数字电路主要分为两类----组合逻辑电路和时序逻辑电路

这篇文章将讨论如何在 verilog 中使用不同的运算符,这些运算符提供了一种在 verilog 设计中处理数字数据的方法

这篇文章主要介绍了 Verilog 在 FPGA 设计中的概念和使用方法

在日常的编码过程中,常常碰到一个参数会被到处调用的情况,比如时钟的定义和调用

Verilog的编译和C语言的编译二者自然不可同日而语,具体到FPGA的开发

本文一起介绍这3个语句的应用场景和应用方法

系统任务$finish的作用是退出仿真器,结束仿真过程

与C语言中的函数类似,在Verilog代码中,通过把代码分成小的模块或者使用任务(task)和函数(function)