本文转载自: OpenFPGA微信公众号

在Vivado使用过程中,会碰到如下情况:设计代码已经编写完成,且仿真、综合或实现中的某一步骤已经通过,不需要再修改。此时可能需要添加一些注释代码,或者调整代码的格式,而任何修改都会导致状态更改为“Out of date”,提示用户更新设计。如何才能在不重新运行综合或实现的情况下解决这个问题?

Vivado状态检测机制

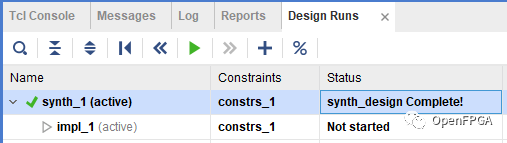

先了解一下Vivado是如何判断综合/实现的运行状态是否为Out-of-date。Vivado在读取源文件时会读取该文件的时间戳,综合/实现运行完毕后,状态会更新为Complete,该状态可以在Vivado的右上角或Design Runs窗口中看到:

每个综合或实现都有一个NEEDS_REFRESH属性,当综合/实现完成时,该属性为False,即不需要更新。当我们修改了设计中的源文件,Vivado会检测到文件时间戳的更新,便会将该属性置为True,同时状态更改为“Out-of-date”,表示需要更新设计:

Force Up-to-Date功能

正如前面所说,我们有时候只是加了些注释,或修改了一些代码格式,并没有做实质上的修改。这种情况下我们并不需要重新运行综合/实现来浪费时间。此时将Out-of-date状态强制更新为Complete即可:

在需要更改状态的综合/实现上右键->Force Up-to-Date,该命令会将NEEDS_REFRESH属性置为False,从而状态修改为Complete,免去重新运行的麻烦。