本文转载自: 明德扬FPGA科教

当我们使用Verilog时,对于信号定义为reg型还是wire型比较混乱,那么今天我们就来讲一讲如何快速的进行信号定义。

在Verilog中,wire永远是wire,就是相当于一条连线,用来连接电路,不能存储数据,无驱动能力,是组合逻辑;并且只能在assign左侧赋值,不能在always @ 中赋值。

reg可以综合成register,latch,甚至是wire(当其只是中间变量的时候),能存储数据,有驱动能力,可以用于组合逻辑或者时序逻辑;在always @模块表达式左侧被赋值。

掌握了基本原理,并不代表我们可以快速的判断信号类型。我们在实际设计中,并不需要考虑这么多,对于信号类型的定义,明德扬有一个小技巧,按照这个技巧使用,就不会出错。即“用always实现的是reg型,其它都是wire型”。

我们举几个例子来使用一下此技巧。

案例一:

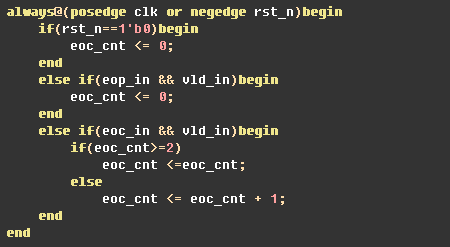

下面代码可以看出是由always模块引导的,因此属于reg类型:

案例二:

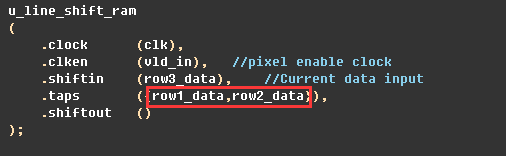

下面代码不是由always模块引导的,因此属于wire类型:

案例三:

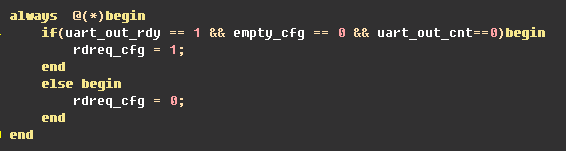

下面代码是由always模块引导的,因此属于reg类型:

案例四:

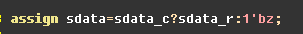

下面代码是由assign模块引导的,不是由always模块引导的,因此属于wire类型:

案例五:

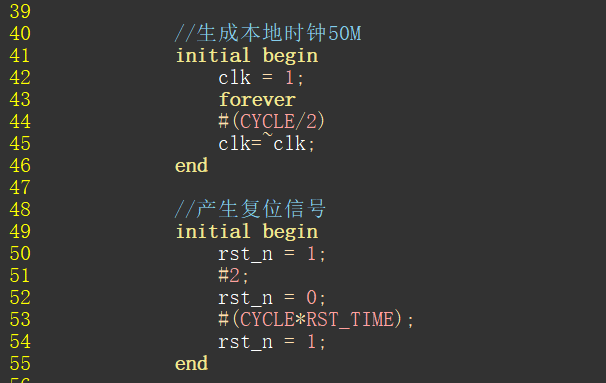

在测试文件中,凡是initial模块引导的信号都是reg类型,因此下面代码属于reg类型:

掌握了信号类型的原理,就非常好判断信号的类型了。大家试着多看一些案例设计进行验证,就会发现明德扬的小技巧非常好用。

因此希望大家可以牢记,定义信号类型时,用always实现的是reg型,其它都是wire型。如果可以完全掌握并多加应用,今后的工程师道路会节省不少的脑细胞。

reg、wire怎么确定?明德扬总结了以下的3句话,大家记好啦:

1、功能文件:

由本模块产生,并且用always产生的信号,就定义成reg

2、测试文件:

由初始化产生(一般是对测模块的输入)的信号,就定义成reg

3、除了以上两种情况,就定义成wire型