来源:内容由半导体行业观察(ID:icbank)编译自hpcwire,谢谢。

AMD 刚刚完成对 FPGA 供应商Xilinx(2022 年 2 月)和 DPU 供应商Pensando (2022 年 5 月)的收购,日前在Hot Chips上,他们预览了它所谓的 400 Gig Adaptive smartNIC SOC 。在日益拥挤和模糊的 smartNIC/DPU 领域,它是另一个竞争者,区分两者并不总是那么容易。

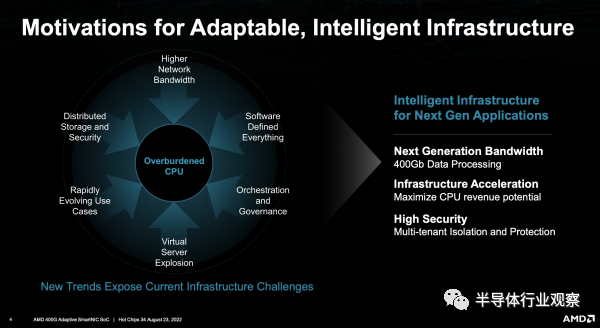

从 Xilinx 加入 AMD 的 Jaideep Dastidar 提出的这些设备类型的动机与近年来Nvidia、Intel 和其他公司的演示非常相似。主机 CPU 忙于处理家务(网络、存储、安全任务)。由于性能和带宽需求的增加、资源的分解以及软件定义一切的兴起,这使情况变得复杂。

Dastidar 说:“转向 smartNIC 和 DPU 的原因是始于行业向软件定义网络的发展,它迅速扩展到软件定义的存储,在你知道之前,你已经拥有了软件定义的一切. 同时,速度和馈送的无情发展仍在继续,网络带宽迅速增加了 25、50、100、200 gig。虚拟化水平也扩大了,你拥有虚拟机,个位数 (VM) 已经上升到 10 位,并且通过容器化,你正在处理 1000 多个虚拟实体。”

“所有这些都导致了 CPU 负担过重的情况。因此,CPU 不是运行多租户应用程序,而是被运行数据中心基础设施所吸收。因此,smartNIC 和 DPU 提供了帮助,因为它们有助于从主机 CPU 卸载这些工作负载,然后主机 CPU 可以重新专注于多租户云应用程序。”Dastidar接着说。

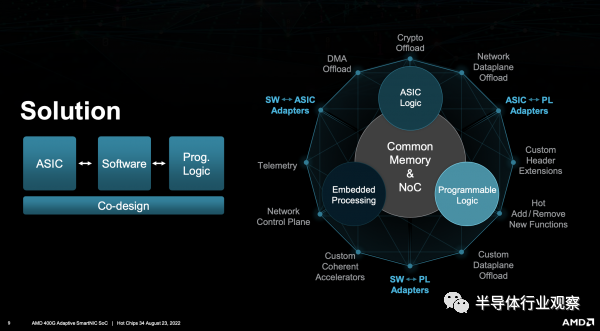

到目前为止,这是一个熟悉的信息。观察市场如何演变将会很有趣。AMD 正在将其 smartNIC 推广为一种灵活高效的 SOC,它在适当的情况下利用固定逻辑 ASIC 技术、在适当情况下利用更灵活的可编程逻辑 (FPGA) 和嵌入式处理器内核。当然,AMD 将自己定位为所有三种技术(ASIC、FPGA 和 CPU/内核)的强大供应商。

与其他公司一样,AMD 也在其系统中加入了先进的安全管理。用例可能非常多样,涵盖网络管理、存储管理和安全性。对 CXL 2.0 的支持值得注意。

“CXL 绝对是一项新兴技术。在第二类设备中,您可以缓存主机内存,也可以拥有加速的设备附加内存。现在,通过可编程逻辑,我们只是想提供灵活性,以便您可以将 smartNIC 作为传统的 PCIe 端点连接,但您也可以探索用例。从 CXL 的角度来看,您需要大量的生态系统支持,因此我们只是在创建能力——创建基础技术——以便人们可以去探索可能作为第二类 CXL 运行得更好的不同用例设备,”Dastidar说。

Dastidar 提供了 AMD 设计思维之旅:“我们决定采用传统的硬件-软件协同设计范式,并将其扩展到硬件-软件-可编程逻辑协同设计。您在右图(上图)中看到的内容,在顶部,我们将 ASIC 逻辑应用在它最擅长的地方:加密卸载、DMA 卸载,甚至是完整的网络数据平面卸载。然后,当您按顺时针方向前进时,我们添加了 ASIC 到可编程逻辑适配器,您开始希望在其中进行分层,例如custom header extensions。继续顺时针方向,您还可以在可编程逻辑中完全热添加或删除新的加速器功能。然后,如果您想一直倾斜天平,我们还希望能够让 SOC 执行完整的自定义数据平面卸载。

“继续顺时针方向。当您有需要与嵌入式处理子系统交互的可编程逻辑代理时,我们有软件到可编程逻辑适配器接口,这样您就可以创建与嵌入式处理器子系统交互的一致 IO 代理。现在,嵌入式处理子系统的尺寸已被确定为运行网络控制平面。如果您注意到,这是我们第一次提到控制平面。与此同时,数据平面正在被完全执行,无论是在 ASIC 逻辑还是可编程逻辑或两者的组合中,”他说。

在遥测功能( telemetry functionality)方面,Dastidar 表示,虽然遥测数据是 SOC 范围的,但嵌入式处理子系统是“收集所有遥测数据、合成数据、然后将其上传到云管理平面(如果他们选择)的最佳位置。”

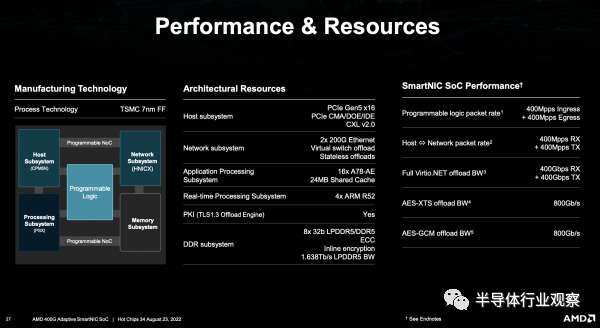

SOC将采用台积电的7nm工艺制造,由功能块组成。虽然 Dastidar 提供了大量有关功能和支持的特性的材料,但他很少提及所需的编程工具是什么。

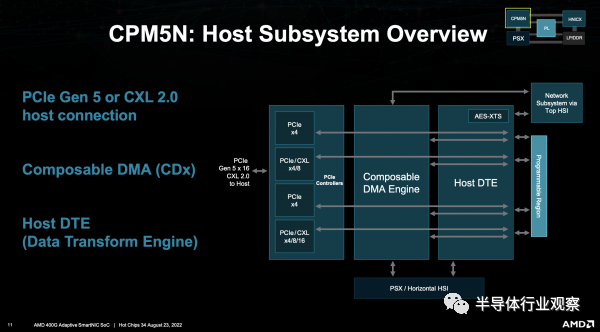

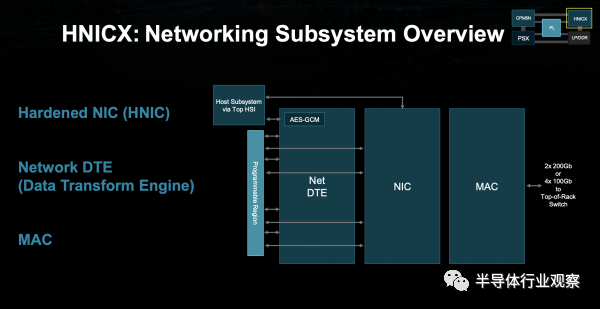

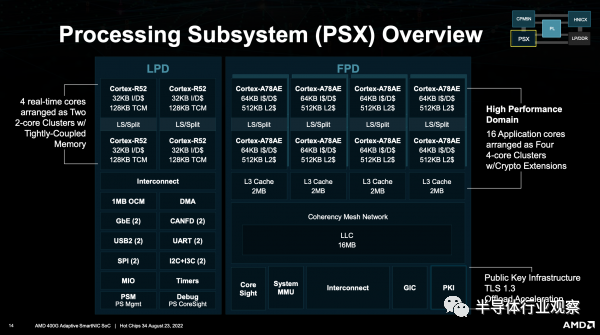

如上图所示,AMD 已将这些设计理念映射到自适应 SOC 内的特定子系统中。主机子系统包含主机连接和主机域加速。包含网络连接和网络域加速的网络子系统。处理子系统包含所有嵌入式处理核心。

Dastidar 说:“虽然这里以视觉方式显示,但我希望您将可编程逻辑元件和内存子系统视为具有芯片普遍连接和访问的芯片普遍资源。片上可编程网络进一步增强了这种连接性,[它]允许子系统到子系统的数据移动,并且任何子系统都可以根据架构选择访问公共内存位置。”

Dastidar 还遍历了每个子系统。这是他对主机子系统的描述的片段。

“主机连接可以是单个主机 PCIe Gen 5 x16 连接到 smartNIC。或者,它可以一直连接到 smartNIC 的四主机 4x Gen 5 x4 连接。此外,控制器支持 CXL 2.0,它们可以支持第一类、第二类或第三类 CXL 设备。现在,正如我之前提到的,PCIe 控制器已升级到最新的 PCIe ECN 安全标准。例如,PCIe CMA(组件测量和身份验证)、PCIe DOE(设备对象交换)、PCIe IDE(完整性和数据加密)和控制器还支持 TDISP,它允许受信任的 VM 以机密计算方式与端点通信, ”达Dastidar说。

“中间的块是可组合的 DMA 引擎。这是一个分层的数据移动器。虽然它可以继续进行主机到卡 [和] 卡到主机数据移动的传统卸载,它还可以促进子系统到子系统的数据移动,并且它可以引导主机到卡的数据数据传输到特定子系统,无论是网络子系统、可编程逻辑还是处理子系统。”

显示其他三个子系统的幻灯片包含在文章的末尾。

还有很多东西需要消化和解包。Dastidar 没有透露该产品何时推出。值得注意的是,新的 smartNIC 基于 Xilinx 的 Versal ACAP(自适应计算加速平台)smartNIC 架构。在问答期间,Dastidar 对有关区分 AMD 的新 smartNIC 与 Pensando DPU 和 Xilinx 的 Versal smartNIC 的问题的回答有点模糊。

“[我们发现] Xilinx smartNIC 技术和 Pensando DPU 技术的结合非常相得益彰。数据中心的不同客户有不同的参与模式。现在 AMD 提供的这种广泛的产品组合让客户可以选择参与其中的任何一种模式。您知道数据中心中的部署不是同质的。在某些情况下,客户可能会发现基于自适应 SOC 的智能网卡对数据中心中的某个节点特别有吸引力,而 Pensando 的基于 DPU 的智能网卡也非常有吸引力。我们注意到的一个常见元素是对客户易用性的高度关注。从文化的角度来看,在客户如何与这个 SOC 以及 Pensando 交互方面,无论是从自适应 SOC 来看,两者都非常接近。有很多投资。

AMD 与 Xilinx 和 Pensando 的合并仍处于早期阶段,产品线整合和协调尚未解决也许不足为奇。smartNIC/DPU 市场正迅速变得更加拥挤,这值得关注。

本文转载自:半导体行业观察微信公众号