作者:Nathan Xu,AMD工程师

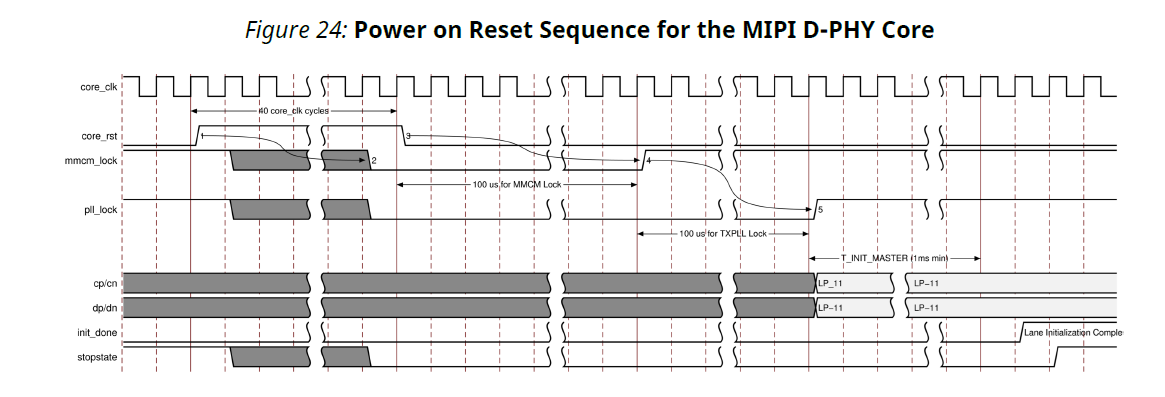

DPHY初始化:

DPHY需要完成初始化, 当clock lane和data lane的init_done置高, 以及stopstate拉高, 标志着初始化完成。 见下图。

给到DPHY的Core_clk需要时200MHz, free-running的时钟, 这个时钟可以来自版上时钟晶振, 或者FPGA内单独的MMCM/PLL, 但该时钟不能来自与两个级联的MMCM。

另外需要注意的是, 所有给到DPHY的时钟需要满足+/-100PPM, 不满足该要求可能会导致数据出错或者重复数据。

Core_rst, 如图所示, 需要assert至少四十个dphy_clk_200M cycle, 然后才能释放。

在上电后, 当master DPHY发给slave D-PHY的cp/cn(clock lane)和dp/dn(data lane)保持在LP-11超过T_INIT时间, 初始化完成. T_INIT必须大于100us。

MIPI CSI-2 RX Subsystem时钟要求:

当line rate < 1500Mbps, video_aclk1 = Line Rate(Mb/s)*Data Lanes/(8*4), 同是, 还需要满足输出的带宽大于等于输入带宽, video_aclk2 = (Line Rate(Mb/s)*Data Lanes) /(Pixels per Clock*Number of Bits Per Pixel). 因此, video_aclk需要同时大于这两个数值。

当line rate> 1500Mbps, 只需要满足输出的带宽大于等于输入带宽, video_aclk >= (Line Rate(Mb/s)*Data Lanes) /(Pixels per Clock*Number of Bits Per Pixel)。

当没有VFB并且line rate < 1500Mbps, video_aclk >= Line Rate(Mb/s)*Data Lanes/(8*4)。

当没有VFB并且line rate > 1500Mbps, video_aclk >= rxbyteclkhs。

对于UltraScale +, 满足timing的Video_aclk最大值是250MHz, 7 series是150MHz, 如果需要提高吞吐量, 可以增加pixel per clock。

Lite_aclk应该小于等于video_aclk。

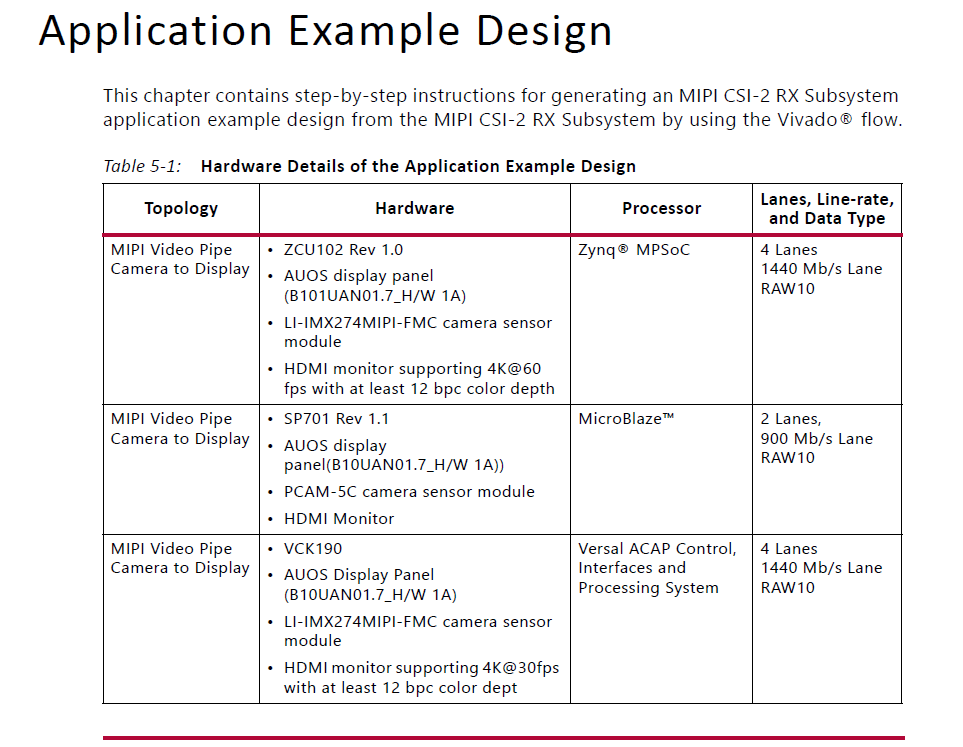

Demo例程:

PG232提供了几个demo, 如下, 这些demo可以用来作为参考和帮助debug。

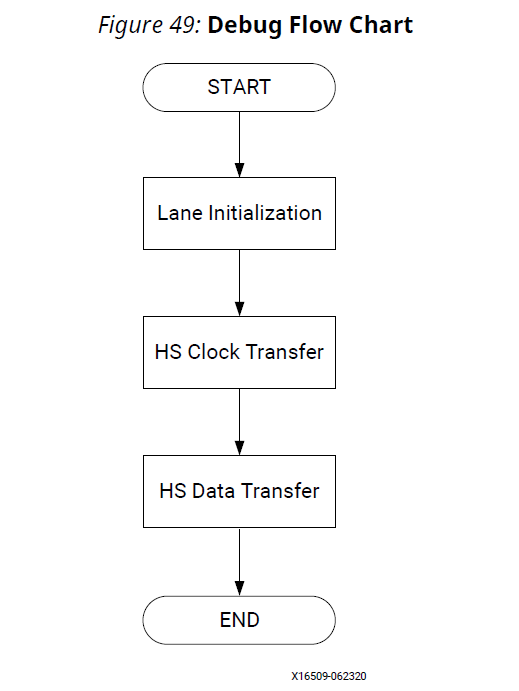

Debug建议:

下图是DPHY的流程图, 在PHY完成初始化后,clock lane切换到HS mode, 然后data lane切换到HS mode, 开始接收数据。

初始化完成后,可以读MIPI CSI-2 RX subsystem IP的所有寄存器。比如,Core Configuration Register (0x00)的bit 0 (Core Enable)有没有打开。

Timing有没有满足。

Video_aclk有没有IP要求。

Interrupt Status Register (0x24) bit 21(Incorrect Lane configuration)有没有置高。

Interrupt Status Register (0x24) line buffer full有没有置位,如果是,一般是输入快于输出, 可以考虑增加pixels per clock, 降低line rate。

如果MIPI CSI-2 RX Subsystem没有收到packets, 那么可能sensor没有发数据, 或者, Frame end packets没有收到, 或者ECC校验没有通过.这时候可以观测DPHY的DL_STATUS Register的PKT_CNT,确认packets有没有增加. 如果没有增加, 进一步检查DPHY的输入和输出.检查MIPI CSI-2 RX Subsystem的Interrupt Status Register的ECC错误, 如果看到很多的ECC 2-bit错误, 那么就是ECC检验没有通过。

如果看到SoT Error, SoT sync Error或者 ECC 1-bit, ECC 2-bit, CRC错误, 一个可能是sensor和MIPI CSI-2 RX Subsystem Lane position mismatch,需要检查是否first byte of the packet在lane 0, 然后next byte在lane 1. 另外一个就可能是sensor的输出timing问题, 可以尝试调整DPHY的HS_SETTLE,当然, 也有可能是SI问题。