来源:内容由半导体行业观察(ID:icbank)编译自Tomshardware,谢谢。

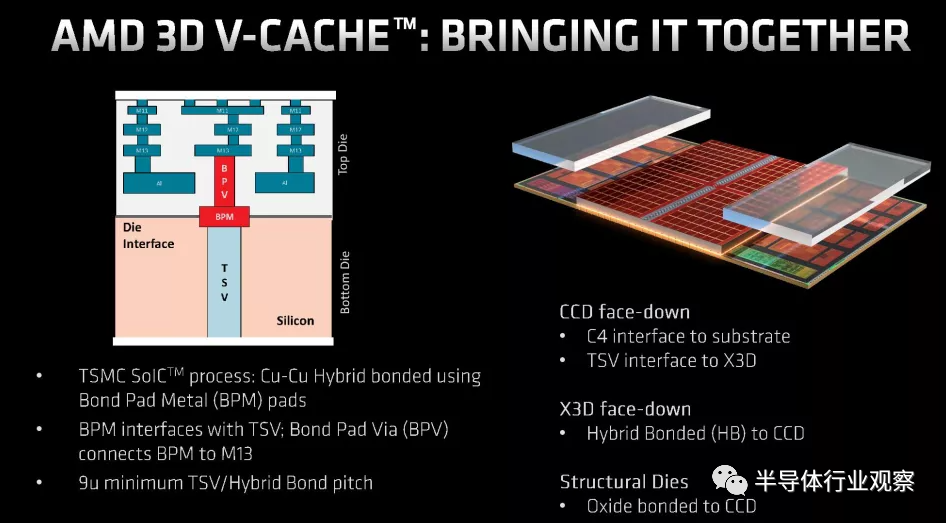

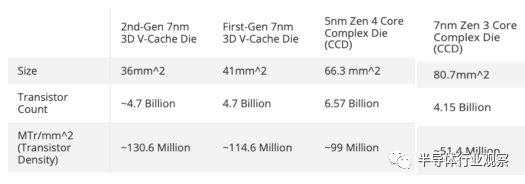

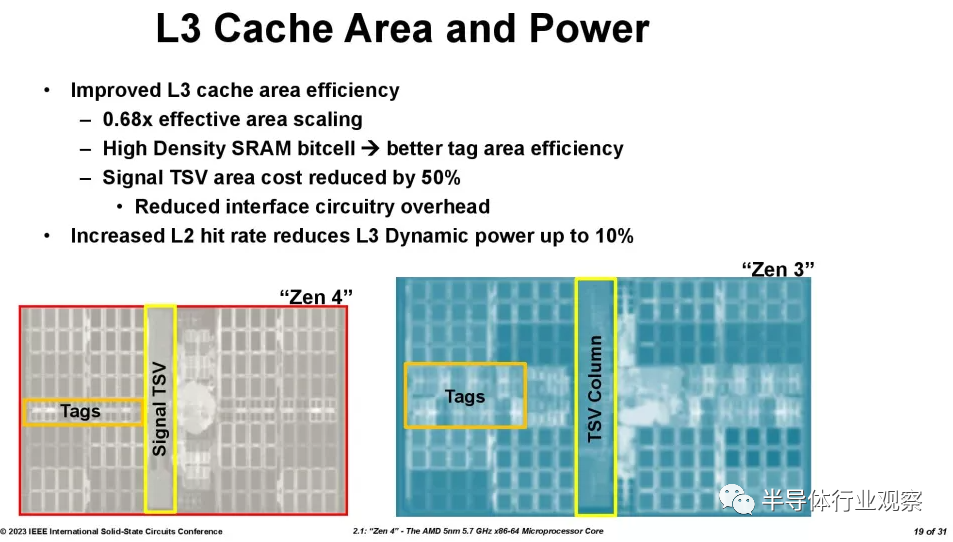

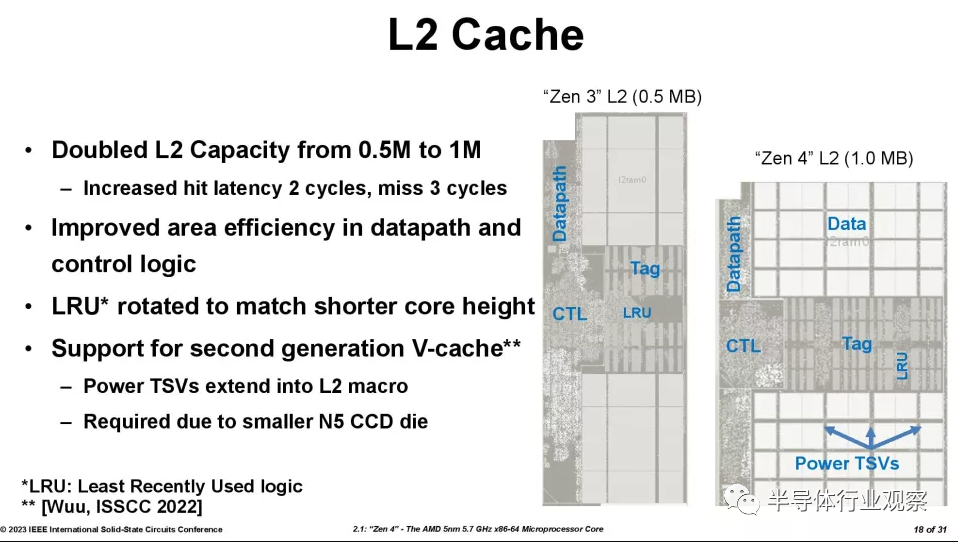

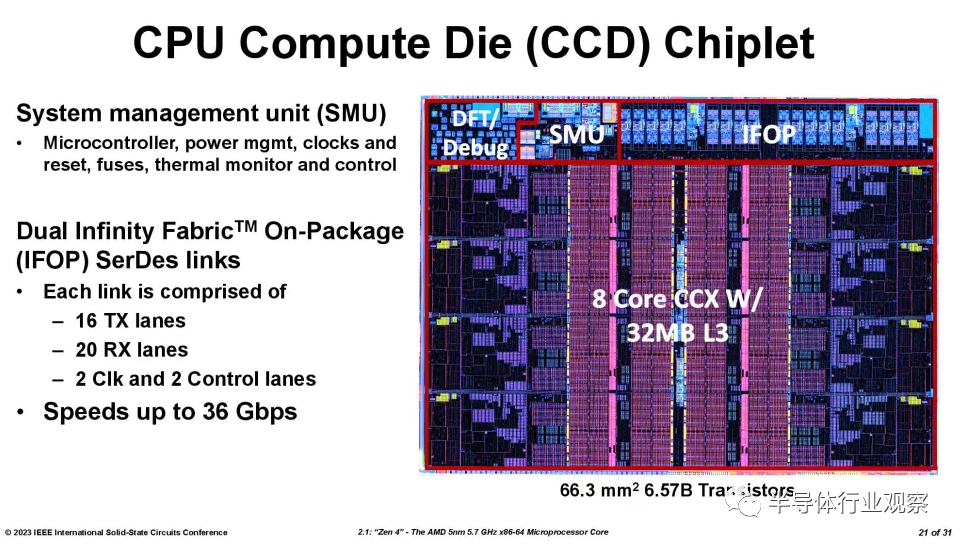

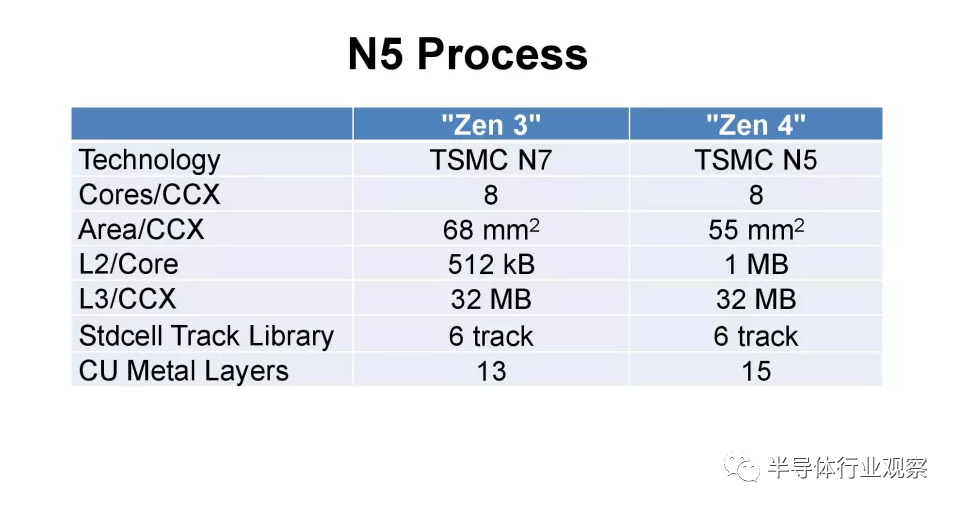

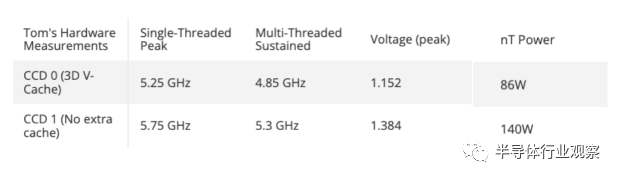

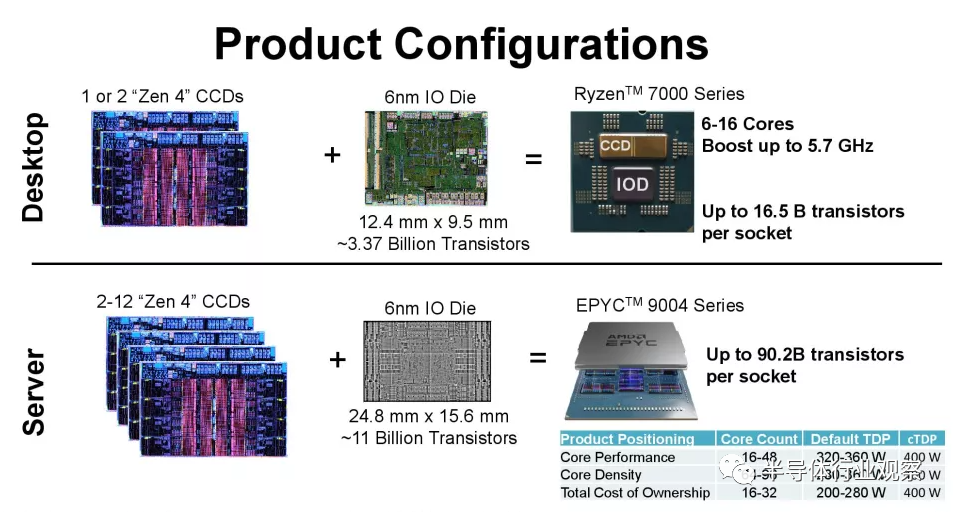

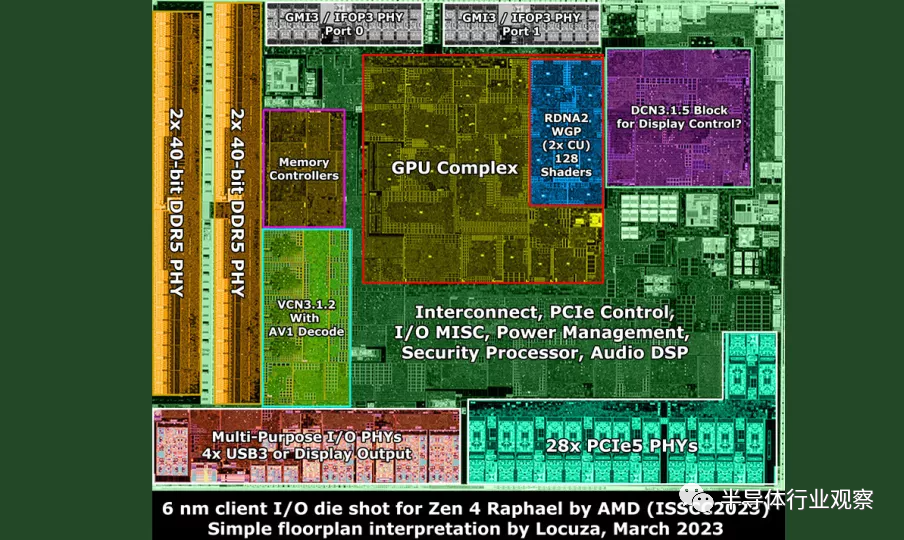

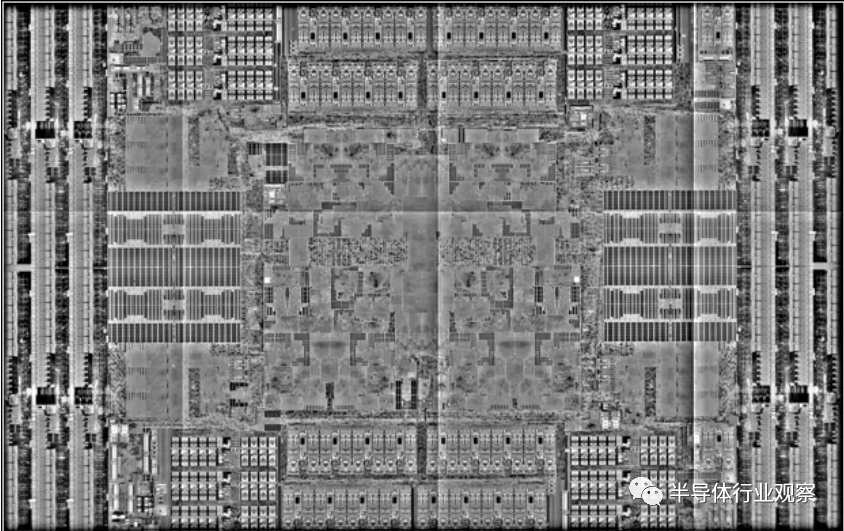

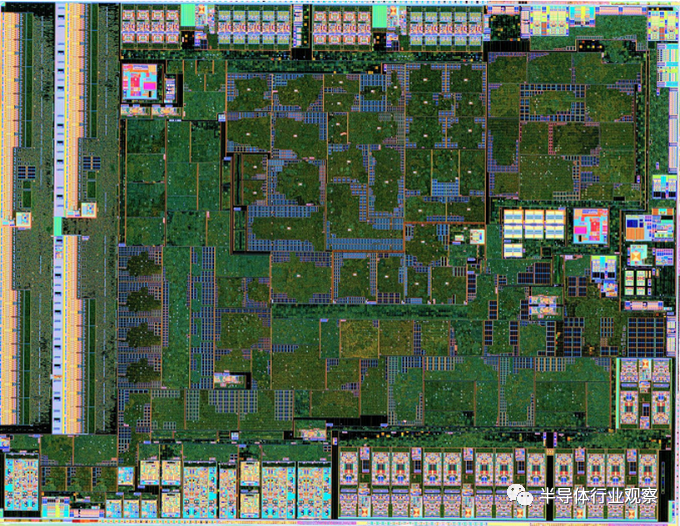

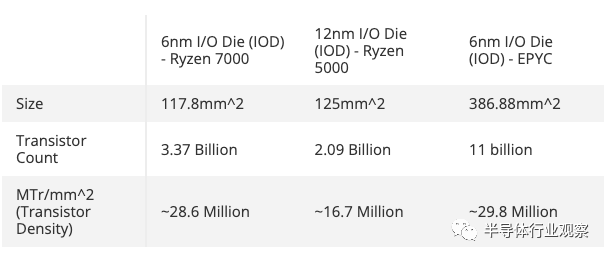

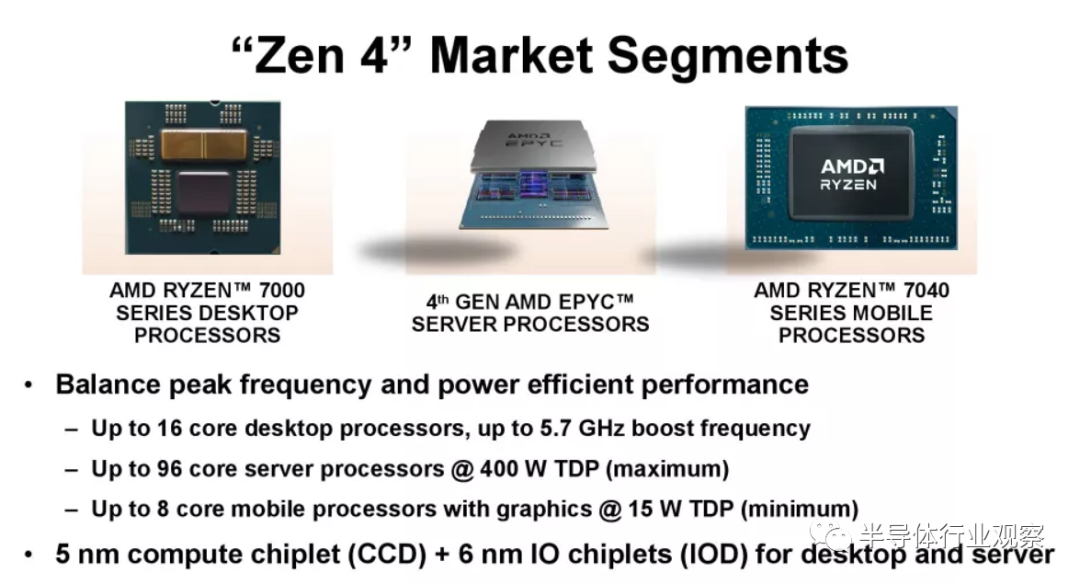

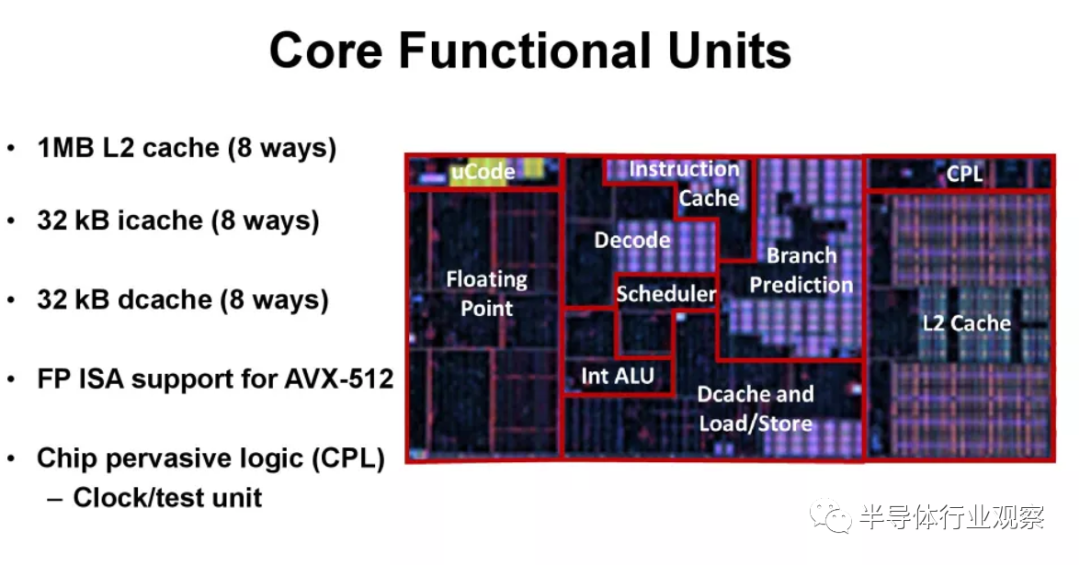

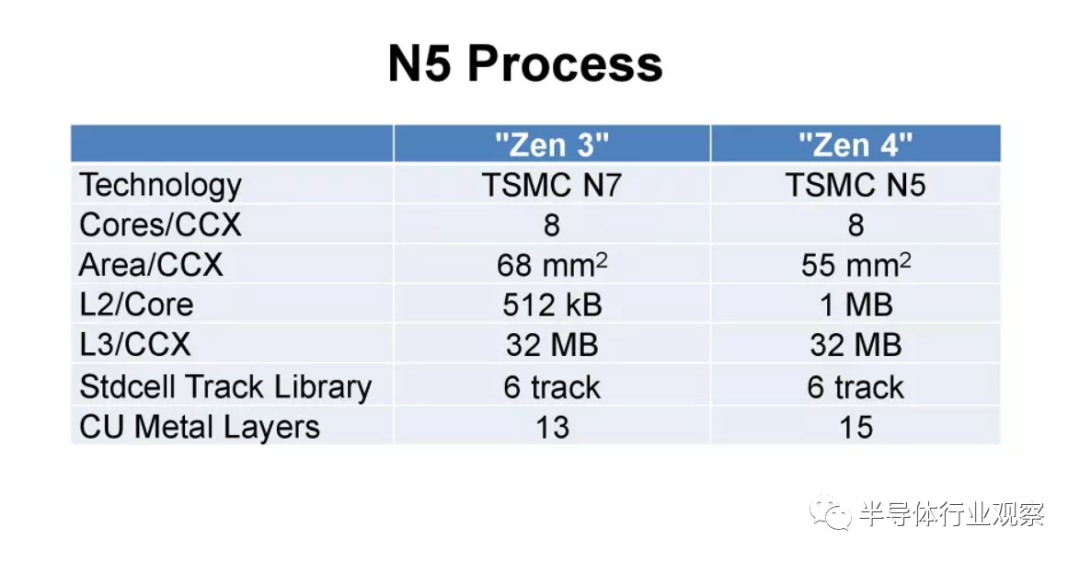

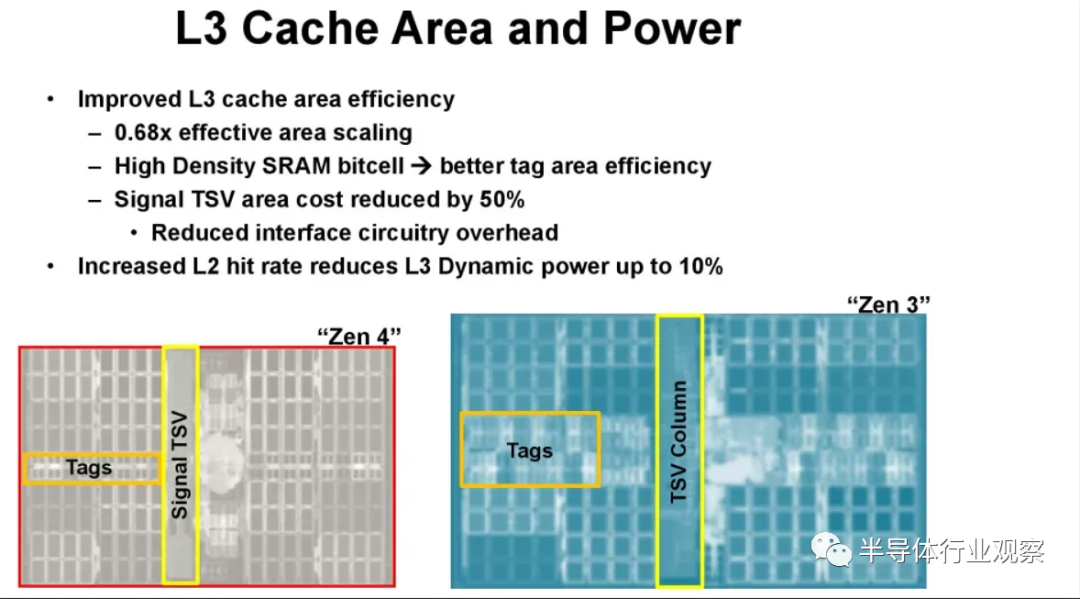

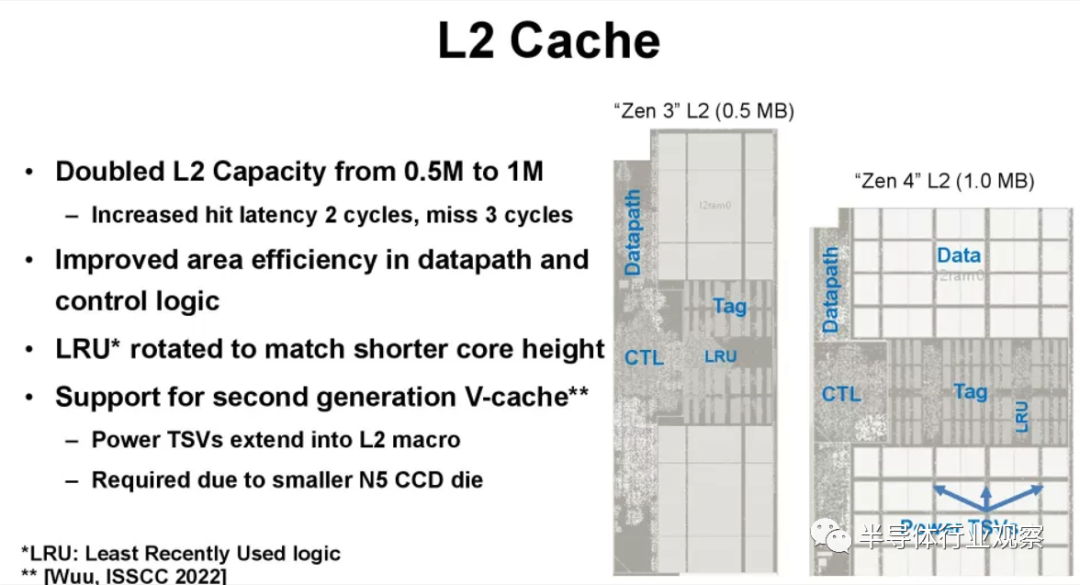

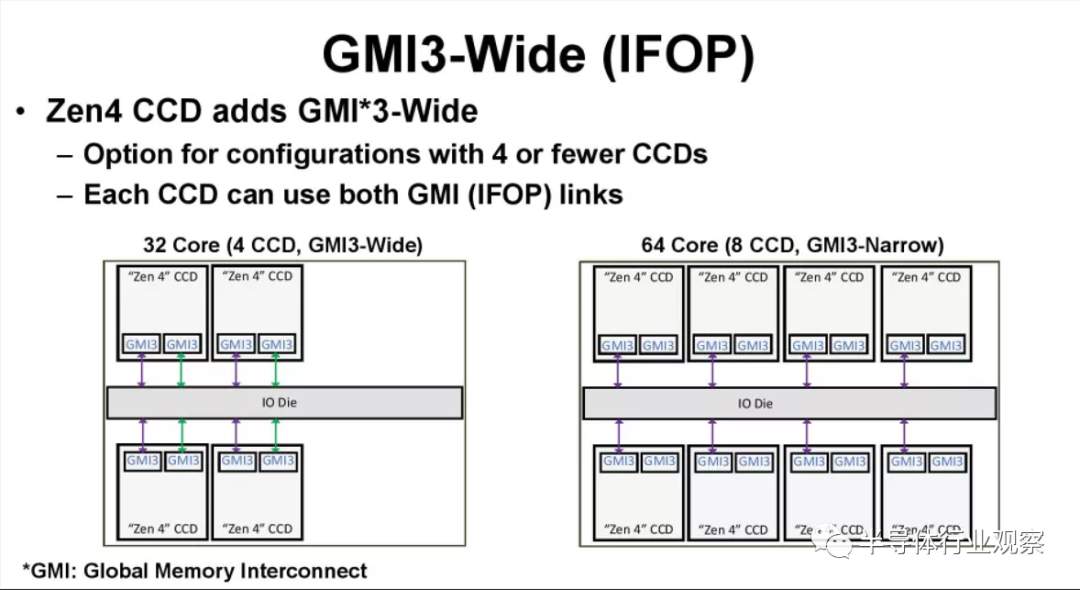

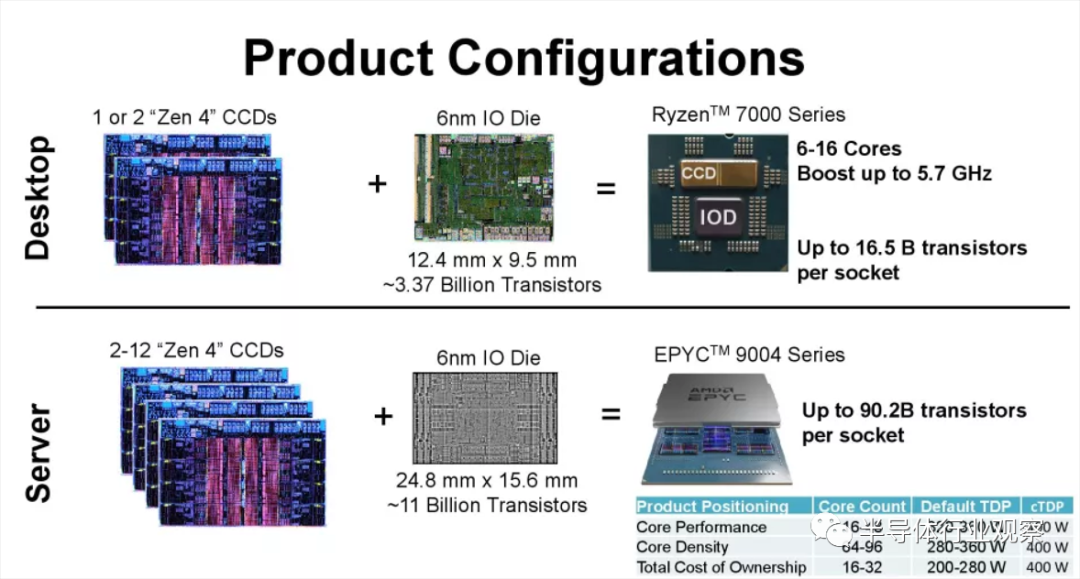

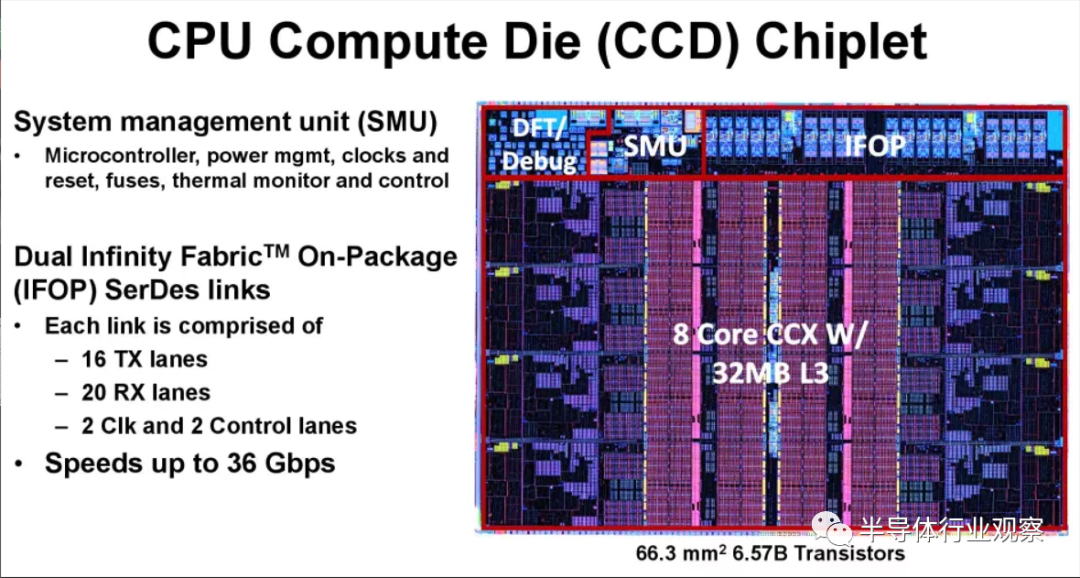

AMD 的Ryzen 9 7950X3D是地球上最快的游戏 CPU,因为 AMD 决定将其颠覆性的 3D 芯片堆叠技术引入 Zen 4,但奇怪的是在其 Ryzen 7000X3D 简报材料中,该公司没有分享有关其新的第二代 3D V-Cache 的任何细节。我们最初在最近的一次技术会议上发现了一些细节,并将其纳入了我们的评测中。 现在 AMD 终于回答了我们的一些后续问题并分享了重要的新细节,包括 chiplet 仍然采用 7nm 工艺,现在有一个峰值带宽高达 2.5 TB/s,而第一代 3D V-Cache 的峰值带宽为 2 TB/s(还有许多其他新信息)。我们还有 AMD 用于其 Ryzen 7000 处理器的新 6nm I/O 芯片的新图片和图表。 AMD 已经转向其 3D V-Cache 的第二代,而英特尔没有与之竞争的技术。这确保了 AMD 在游戏和某些数据中心应用程序的最佳 CPU方面获胜。 总体而言,AMD 的第二代 3D V-Cache 技术比第一代技术向前迈出了令人印象深刻的一步,因为它允许公司利用现在成熟且成本较低的 7nm 工艺节点来提升其尖端 5nm 计算的性能die。新设计代表 AMD 将基于小芯片的设计方法的关键优势——使用旧的、更便宜的工艺节点与昂贵的新工艺技术相结合——进入三维。 现在,我们详细介绍其细节。 首先,快速进行高级复习。正如您所看到的,AMD 的 3D V-Cache 技术将一个额外的 L3 SRAM 芯片直接堆叠在计算芯片 (CCD) 芯片的中心,以将其与发热核心隔离开来。该缓存将配备 3D V-Cache 的小芯片的容量提高到 96MB,从而提高对延迟敏感的应用程序(如游戏)的性能。 我们直接从 AMD 和 2023 年国际固态电路会议 (ISSCC) 收到了有关第二代实现的新信息,AMD 在会上介绍了 Zen 4 架构。 AMD 的上一代 3D V-Cache 使用堆叠在 7nm Zen 3 CCD 之上的 7nm L3 SRAM 芯片。AMD 坚持为新的 L3 SRAM 芯片(称为“L3D”)采用 7nm 工艺,但现在将其堆叠在更小的 5nm Zen 4 CCD 之上(见下表)。但是,这会造成尺寸不匹配,需要进行一些改动。 首先,AMD 使 7nm SRAM 芯片更小,因此与上一代的 41mm2相比,它现在的尺寸为 36mm2 。然而,晶体管总数保持不变,约为 47 亿,因此新芯片的密度明显高于第一代小芯片。 正如我们在第一代 SRAM 小芯片上看到的那样,7 纳米 L3 SRAM 小芯片具有令人难以置信的晶体管密度——我们看到的密度几乎是第一代 7 纳米计算小芯片的 3 倍,而且令人惊讶的是,7 纳米 SRAM 小芯片的密度明显高于第一代 7 纳米计算小芯片。5nm 计算小芯片。这是因为,和以前一样,小芯片使用专门用于 SRAM 的密度优化版本的 7nm。它还缺少缓存中的典型控制电路——该电路驻留在基础芯片上,这也有助于减少延迟开销。相比之下,5nm 芯片包括几种类型的晶体管以及数据路径和简化的 L3 SRAM 芯片中不存在的其他类型的结构。 和以前一样,额外的 L3 SRAM 缓存带来的额外延迟为 4 个时钟,但 L3 小芯片和基础裸片之间的带宽增加到 2.5 TB/s,比之前的 2 TB/s 峰值提高了 25%。 堆叠的 L3 SRAM 小芯片通过两种类型的硅通孔(TSV——垂直电连接)连接到基础芯片。功率 TSV 在小芯片之间传输电力,而信号 TSV 在单元之间传输数据。 在第一代设计中,两种类型的 TSV 都位于基础小芯片的 L3 区域。然而,由于 5nm 工艺密度的增加,基础芯片上的 L3 缓存现在更小了,即使 7nm L3 SRAM 小芯片更小,它现在也与 L2 缓存重叠(上一代仅与基础上的 L3 重叠死)。因此,AMD 不得不改变基础芯片和 L3 SRAM 芯片中的 TSV 连接。 由于基础芯片上 5nm L3 缓存的尺寸较小(密度增加和其他因素的结果),AMD 不得不将功率 TSV 从 L3 扩展到 L2 区域。对于基础裸片,与旧的 7nm 基础小芯片相比,AMD 在 L3 缓存、数据路径和控制逻辑上实现了 0.68 倍的有效面积扩展,因此 L3 缓存中 TSV 的物理空间更小。 信号 TSV 保留在基础芯片上的 L3 缓存区域内,但 AMD 通过应用从第一代设计中学到的知识以及 DTCO 改进,将 L3 缓存中的 TSV 区域缩小了 50%,以减少新接口设计中的开销电路。 AMD 的 3D 芯片堆叠技术基于 台积电的 SoIC 技术. 台积电的 SoIC 是无凸块的,这意味着它不使用微凸块或焊料来连接两个芯片。AMD 告诉我们,它使用了相同的基本键合工艺,并结合了持续的工艺和 DTCO 改进,但最小 TSV 间距没有改变。 L3 SRAM 小芯片也与 CPU 内核保持在同一电源域,因此无法独立调整。这有助于降低配备缓存的小芯片的频率,因为电压不能超过 ~1.15V。 AMD 的 ISSCC 演示文稿还包括大量有关 Ryzen 7000 和 EPYC Genoa 处理器中使用的 6nm I/O 芯片 (IOD) 的新细节。在上面的相册中,您可以看到放大的图像和来自芯片侦探@Locuza_的带注释的die shot。 我们将规格放在表格中以便于比较,如您所见,与 Ryzen 7000 变体相比,EPYC Genoa I/O Die 非常庞大 — 这是因为 AMD 可以将多达 12 个计算小芯片 (CCD) 连接到 I /O 用于其EPYC Genoa处理器。 相比之下,消费类芯片仅限于两个小芯片,这是一个不可改变的限制,因为正如您在 Locuza 的图表中所见,Ryzen 7000 I/O Die 只有两个全局内存互连 2 (GMI2) 链接,将计算小芯片连接到IOD。真可惜——具有四个 CCD 的较低内核数 Genoa 模型可以具有双 GMI3 链接(宽模式),这是一种新功能,可以在某些内存吞吐量密集型任务中提供优势。将其添加到消费芯片中会很有趣。 附:AMD在ISSCC上的完整PPT