从音频输入到输出,现有的实时数字音频系统很难实现低于 1ms 的时延。实际上,200µs 是到目前为止可实现的最佳时延。INSA(法国)的 Emeraude 研究团队正在开发 Syfala 编译器,该编译器结合了 Faust (一种用于实时音频 DSP 的领域特定语言)和 AMD Vitis™ HLS,使其为音频 DSP 用户提供非常高级的音频合成工具。

Emeraude 采用基于 AMD Zynq™ 的FPGA 板卡、低时延音频编解码器和 Syfala 编译器,在众多简单的 DSP 程序上实现了 11µs 的低时延。这项新技术适用于声音合成和主动声学控制。

1. 项目挑战

实时音频数字信号处理( DSP )已经在广泛的计算机架构上实现:采用冯・诺依曼架构的 CPU、多核 CPU、GPU、专用电路、FPGA 等。然而,实现超低时延(即小于 1ms)的唯一方法是使用专用电路,如 ASIC 或 FPGA。

尽管如此,对于 DSP 程序员而言,使用 FPGA 几乎是不可能的事情,因为他们没有掌握硬件设计技能。

因此,该项目的主要挑战在于设计出一款工具,允许音频 DSP 程序员以极低时延(即小于 100µs)在 FPGA 上实现任意音频 DSP 算法。

2. 解决方案

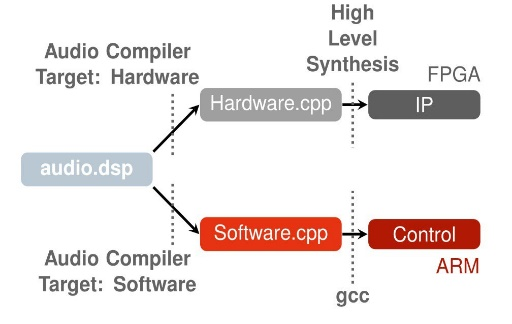

采用的解决方案是将音频 DSP 语言编译器(即 Faust)的输出与 HLS 工具 Vitis HLS连接起来。Faust 编译器不仅可处理软硬件分区,而且还可隔离将在 FPGA 上实施的内核 DSP 算法,如图 1 所示。

图 1:从 Faust 程序到 FPGA 的 Syfala 编译流程

Vitis HLS 用于实现该内核 DSP 的硬件,允许访问外部 DDR 内存以及使用 ARM Zynq 处理系统驱动程序的硬件控制器。

图 2:DSP 硬件控制在 Digilent Zybo 板上实现

INSA-LYON 的研究团队主管 Tanguy Risset 表示:“Vitis HLS 允许我们直接重复使用 Faust 编译器生成的 C++ 代码,因此从 Faust 高级规范直至 FPGA 比特流都无需经历手动设计流程。此外,Vitis HLS 与 AMD 的设计流程能够很好地集成在一起,方便我们进行硬件/软件的协同设计。”

3. 设计成效

最终成效就是获得一个新的编译流程,可将任意音频 DSP 程序自动编译到基于 AMD Zynq 7000 的 FPGA 板卡(如 Digilent Zybo 或 Genesys)上。这样一来,从模拟输入到模拟输出,所实现的程序的时延可低至 11µs。如此短的时延是前所未有的。该编译器是开源的,目前用于实现主动声学控制算法和 3D 音频编解码流程。

Risset 补充道:“Vitis HLS 使我们能够精确控制 IP 的时延。特别是 Vitis HLS 能够生成一个有一个样本延迟时延的 IP。这对于实现我们在模拟与模拟之间实现的时延极为重要。”

Risset 表示,Vitis HLS IP 的调度视图有助于我们了解 Vitis HLS 是如何引导并行化,以及内存访问是如何对 IP 时延产生影响的。他补充道:“这促使我们在 Faust 生成的 C++ 代码中对内存访问进行优化,这是实现低时延的必要步骤。”

进一步了解 AMD Zynq SoC,请访问产品专区。

关于 Emeraude INSA 研究团队

Emeraude INSA 研究团队正在就嵌入式音频编程系统展开研究,同时也在为 Faust 编译器提供维护服务。

关于 Syfala 编译器

Syfala 编译器目前可用于 GitHub,而且可以与任意 I2S 音频编解码器(基于任何 Zynq 平台的板卡)配合使用。此外,它也可用于非超低时延音频的环境中,例如包括高阶环绕声等在内的多声道应用。