使用PCIE更新ZYNQ的QSPI Flash参考设计

judy 在 周四, 11/16/2023 - 16:59 提交

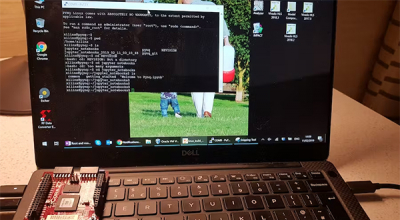

本教程提供一个最小的参考设计,使上柆机可以通过PCIE端口

本教程提供一个最小的参考设计,使上柆机可以通过PCIE端口

LeNet-5 是一个非常经典和成功的卷积神经网络结构

该项目演示如何在 Zynq SoC 上开始使用 FreeRTOS

本项目将是一个非常简化的基带符号映射器,用于 FSK 数字调制方案的链的发送端

本文介绍了在AMD Xilinx Zynq平台上实现嵌入式软件和FPGA设计的集成工作流程

本文将探讨为何采用 8K 视频、其优势和潜在缺点

如何为自己的ZYNQ板卡创建 Pynq 镜像

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

选择创建Block Design并命名,点击Add IP,并选择ZYNQ7

本文说明如何向Block Design添加.v文件模块