作者:Suhel Dhanani,AMD 自适应 SoC 和 FPGA 事业部软件市场营销总监

随着设计变得日益复杂,AMD 不断推动创新,确保为系统架构师和开发人员提供所需的工具,以高效开发包含处理子系统和 FPGA 架构的混合域设计。

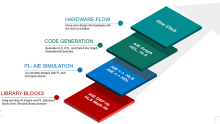

今天,我很高兴地宣布 Vitis™ 统一软件平台 2023.2 版本发布,该版本提供了一个单一的环境,便于使用 AMD 自适应 SoC 与 FPGA 简化高性能设计的设计、仿真与实现。

我们的最新版本发布了新的功能,例如用于嵌入式 C/C++ 设计的独立工具、新的统一图形用户界面( GUI )以及一系列增强功能,从而简化了搭载 AI 引擎( AIE )的 AMD Versal 自适应 SoC 的使用。

新功能助您开发 Versal AIE-DSP 设计

我们的 2023.1 版本提供了增强的工具,支持基于 AIE 的 DSP 设计的实现。2023.2 版本将这些增强推进了一步,提供了新的 DSP 库函数、DSP 函数的新的 API 支持,以及 AIE 模拟器/编译器中的新功能。

从 2023.2 版本开始,AIE 模拟器/编译器工具链现在可支持 Versal Edge AIE-ML 架构,包括更大型的 AIE-ML 内存块。这使得在 Versal AI Edge 器件中实现高性能 DSP 设计成为可能。

面向 AIE 的全新 DSP 库函数,如混合基 FFT( Mixed Radix FFT )、离散傅里叶变换( DFT )和通用矩阵向量乘法( General Matrix-Vector Multiply )等,都有助于简化开发流程。对于 AIE-ML 来说,新的 DSP 库函数包括额外的 FIR 滤波器配置(半带、单速率、分数重新采样器、速率变化插值/抽取)以及通用矩阵乘法( GeMM )和 DFT。

此版本还为使用 cint32 twiddle 数据类型、面向 Radix-4 FFT 的 cint16,以及向量化的“fix2flt”和“fit2fix”运算执行 FFT 提供 API 支持。

全新的多线程模拟器内核能够加速 AIE DSP 设计仿真。此外,AIE 模拟器现在还支持使用 MATLAB® 和 Python 的实时流量生成功能进行测试。

Vitis™ 分析器现在增加了指导报告,旨在帮助用户选择合适的 FIFO 大小,从而防止死锁拥塞并最大限度提升系统性能与可靠性。

使用独立工具快速构建嵌入式设计

我们听取了客户关于需要用于 C/C++ 应用代码开发的独立嵌入式工具的反馈。2023.2 版本推出了 Vitis™ Embedded,这是一款根据开发人员需求而定制的全新工具,旨在为嵌入式处理子系统设计和编译 C/C++ 软件。

新工具单个文件下载的大小不到 15 GB,比完整 Vitis 软件平台要小得多,不仅可为 Arm® 和 MicroBlaze™ 处理器提供完整的编译器和模拟器,还具备开发人员进行嵌入式处理子系统设计所需的所有功能。

借助易于使用的统一界面简化开发

在这个新版本中,我们面向所有 Vitis 工具推出了新的、统一的、下一代图形用户界面( GUI )。现在,开发人员无需在多个 GUI 中学习与工作了。

Vitis Embedded、Vitis HLS、Vitis 分析器和 AIE 编译器现在均具有一致的观感,从而带来无缝的用户体验。

利用端到端工具进行复杂设计

我们希望您和我们一样对更新感到兴奋不已。

展望 2024 年,我们将继续专注于对工具、库和功能进行优化,以满足下一代设计需求,包括在 Versal 自适应 SoC 中使用 AIE。

立即下载 2023.2 版本快速启动您的设计吧