作者:Ivy Guo,AMD工程师;来源:AMD Xilinx开发者社区

SEM IP将错误大致分为两类,可纠和不可纠。在开启了Correction纠错功能后,绝大部分SEU错误都能被IP及时检测到并纠正;但是也有极小一部分因为位置、数量的原因,仅能被检测到但是无法纠正。一般IP碰到此类错误,会上报错误信息然后进入IDLE停止状态,等待上层机制的判定:比如复位,重新配置,掉电等等。

那么实验室环境如何模拟这一错误现象呢?其实很简单。查看pg187,注意有这样一句描述:

ECC algorithm-based correction that supports correction of configuration memory

frames with up to 4-bit errors.

这其实暗含了UltraScale/UltraScale+系列的纠错能力的说明:即同一个配置帧内,可以同时纠正多达4bit的错误。

那么相应地,我们只要在同一个地址帧内注入超过4个错误,就超出了IP的纠错能力范围,可以在log中读到uncorrectable error的信息了。

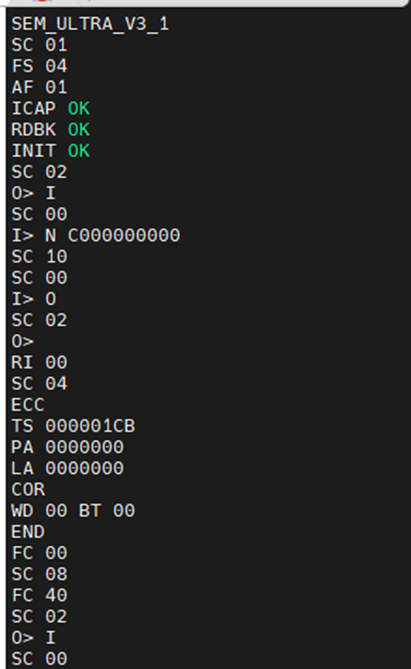

以VCU108开发板为例,先运行一个基本的纠错功能程序:

可以看到,SEM IP正常工作,在插错后正确检测到了错误的位置,并进行了纠正。

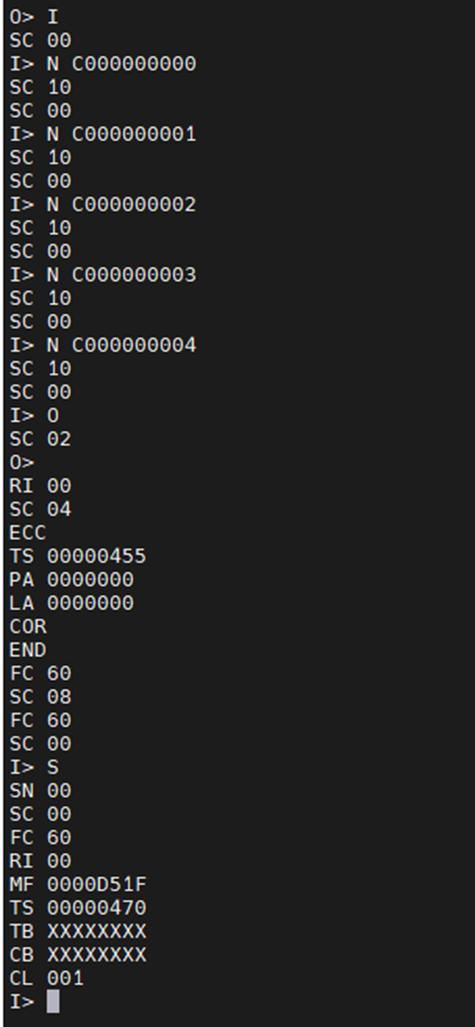

接下来我们连插5个相邻的bit位置实验一下:

如图,5个相邻bit已经超出了SEM IP的纠错能力范围,此时它只能够检测出错误所在的帧地址,但是具体位置已经‘不可知’了,当然这种情况下也就无法纠正了。IP报告这一情况后 (COR/END/FC 60),进入了IDLE状态。虽然仍然支持通过命令口查询当前状态‘S’,但实际上已经不再扫描器件了。需要上层决策层决定下一步的操作。

自然界中SEU现象本身就是比较少,多bit错误更是罕见。像这种一下子击中CRAM的连续5bit以上的错误,概率更是极低。所以正常情况下,SEM IP的纠错能力已经足够使用。此方法仅是让大家观察一下IP在碰到不可纠错误后的反应,以做好应对策略。