面试题:2个异步FIFO的处理

judy 在 周一, 09/18/2023 - 09:24 提交

有一个数据需要从A时钟域同步到B时钟域,数据位宽是512bit的

有一个数据需要从A时钟域同步到B时钟域,数据位宽是512bit的

异步FIFO通常用于跨时钟域处理,是逻辑设计常用基础模块

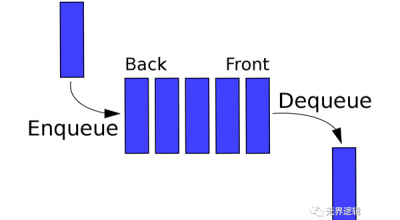

FIFO:First in, first out,先进先出;其主要作用是:数据缓存

在一个跨异步时钟的设计中,数据需要从A时钟域同步到B时钟域

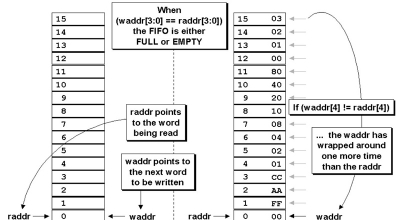

本文讨论了一种 FIFO 设计风格以及在进行异步 FIFO 设计时必须考虑的重要细节

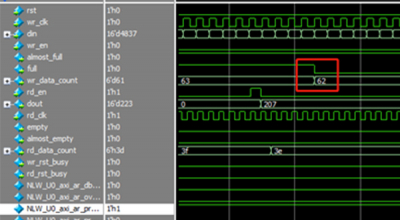

以前从来没有这么细扣过,认识比较肤浅,通过几天对Xilinx IP核的仿制,对异步FIFO有了更深刻的认识。

FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

1.定义

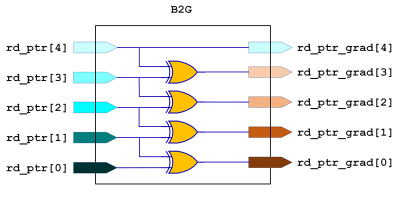

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。