为啥FPGA资源/时序都有很大的优化空间?

judy 在 周二, 04/23/2024 - 09:49 提交

在工作中,我们接触到的至少90%以上的FPGA项目,它的的资源/时序都有很大的优化空间,为啥这么说?

在工作中,我们接触到的至少90%以上的FPGA项目,它的的资源/时序都有很大的优化空间,为啥这么说?

今天的文章让我们来看看当设计不能满足时序要求时如何分析并解决它

跟FPGA打交道这么多年,多多少少总会碰到一些时序问题

对于搞FPGA的人来说,资源和时序的优化,应该是一个永恒的话题

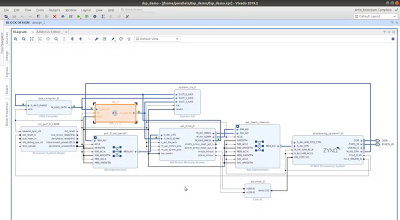

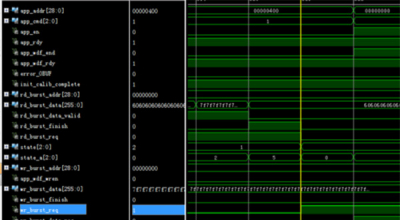

DDR接口信号分为DDR对外接口信号、用户应用接口信号和读写控制信号。对外接口信号直接与DDR芯片连接,用户应用接口信号为DDR控制器IP输出信号

运行“report_timing” 或 “report_timing_summary” 命令后,我注意到 WNS、TNS、WHS 和 THS。什么是 WNS、TNS、WHS 和 THS?

本篇博文中的分析是根据客户真实问题撰写的,该客户发现即使时序已得到满足的情况下,硬件功能仍出现错误。最后发现,问题与时钟域交汇 (Clock Domain Crossing) 有关,因此,本篇博文介绍了如何调试设计中的时钟域交汇问题。

Xilinx Artix®-7 系列的成本优化型 FPGA ,提供具有业界最高性能功耗比的结构、收发器线速、DSP 处理能力和 AMS 集成。该系列产品采用 MicroBlaze™ 嵌入式软核,支持 1066Mb/s DDR3,特别适用于各种成本功耗敏感型应用,比如软件定义无线电、机器视觉相机和低端无线回传。大电流型号适合 > 4A 的设计,小电流型号适合 < 4A 的设计。

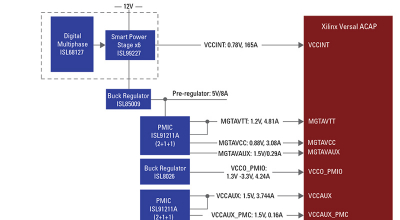

Versal 自适应计算加速平台(ACAP)是 Xilinx 最新的 SoC 片上系统系列之一。它包含了标量处理引擎、适配硬件、(软件可编程和硬件可调整)智能引擎和片上网络,即一个软件可编程基础架构。这需要适应能力很强的精确时序和电源。

本文将从代码风格,时序修正,工程设置等几个方面介绍本人的实践经验,希望让各位初学者快速提高,也希望FPGAer能给出宝贵建议。